我是靠谱客的博主 糟糕纸鹤,这篇文章主要介绍※以同步左移移位寄存器为基础, 设计001010序列信号发生器(对比以同步右移移位寄存器为基础, 设计001010序列信号发生器),现在分享给大家,希望可以做个参考。

在上一篇博文中, 我们了解到该如何使用同步右移移位寄存器设计001010序列信号发生器——这是本例设计的基础.

使用同步右移移位寄存器作为设计核心部件, 得到的序列信号从Q3端获取. 下面我们看一下使用同步右移移位寄存器作为核心部件展开设计的状态顺序表.

| 状态顺序表(右移) | ||||

| CLK顺序 | Q3 | Q2 | Q1 | Q0 |

| 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 2 | 1 | 0 | 1 | 0 |

| 3 | 0 | 1 | 0 | 0 |

| 4 | 1 | 0 | 0 | 0 |

| 5 | 0 | 0 | 0 | 1 |

| 6 | 0 | 0 | 1 | 0 |

若将状态顺序表中的Q3Q2Q1Q0改为Q0Q1Q2Q3, 则得到下述状态顺序表.

| 状态顺序表(左移) | ||||

| CLK顺序 | Q0 | Q1 | Q2 | Q3 |

| 0 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 2 | 1 | 0 | 1 | 0 |

| 3 | 0 | 1 | 0 | 0 |

| 4 | 1 | 0 | 0 | 0 |

| 5 | 0 | 0 | 0 | 1 |

| 6 | 0 | 0 | 1 | 0 |

如此一来, 原本现态与次态间的关系就由"右移一位"变为"左移一位"了, 且序列信号001010由Q0端获得.

我们再来看一下右移关系的状态表.

| 状态表(右移) | |||||||

| Q3 | Q2 | Q1 | Q0 | Q3* | Q2* | Q1* | Q0* |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

显然, 若将Q3Q2Q1Q0改为Q0Q1Q2Q3, 则得到左移关系的状态表.

| 状态表(左移) | |||||||

| Q0 | Q1 | Q2 | Q3 | Q0* | Q1* | Q2* | Q3* |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 0 |

由状态表(左移), 得到状态激励表(由于是"左移"关系, 所以只需要考虑同步左移移位寄存器的左移串行输入端(D3)).

| 状态激励表 | ||||

| Q0 | Q1 | Q2 | Q3 | D3 |

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

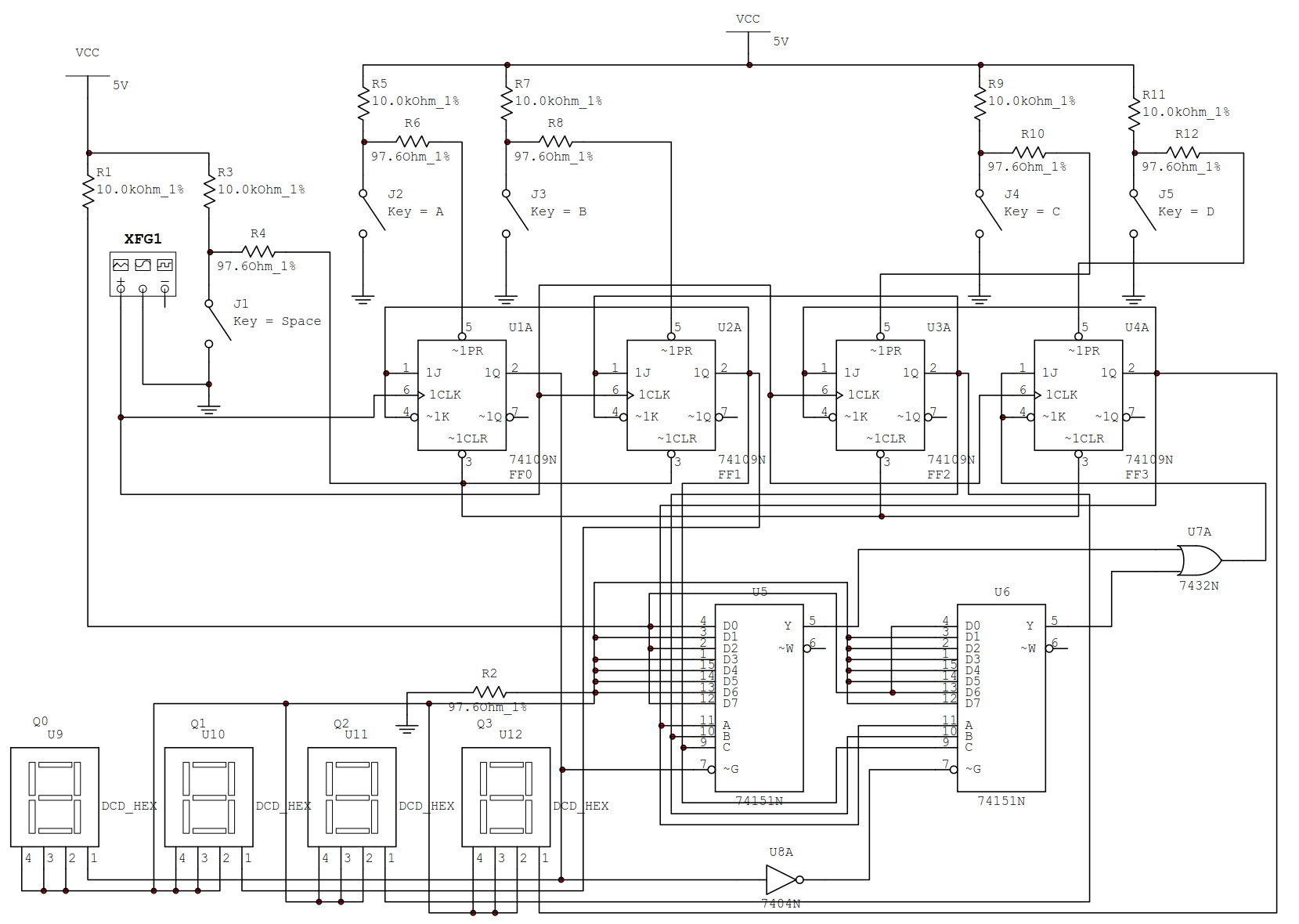

用2片74151和一片非门实现16选1数据选择器, 将D3的逻辑表达式实现.

由上面的分析, 绘制电路的原理图.

本题的设计思路十分经典, 读者应掌握该种改造方式, 可大大提升电路设计效率.

最后

以上就是糟糕纸鹤最近收集整理的关于※以同步左移移位寄存器为基础, 设计001010序列信号发生器(对比以同步右移移位寄存器为基础, 设计001010序列信号发生器)的全部内容,更多相关※以同步左移移位寄存器为基础,内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复