实验:带加载使能和移位使能的并入串出移位寄存器

设计思路:

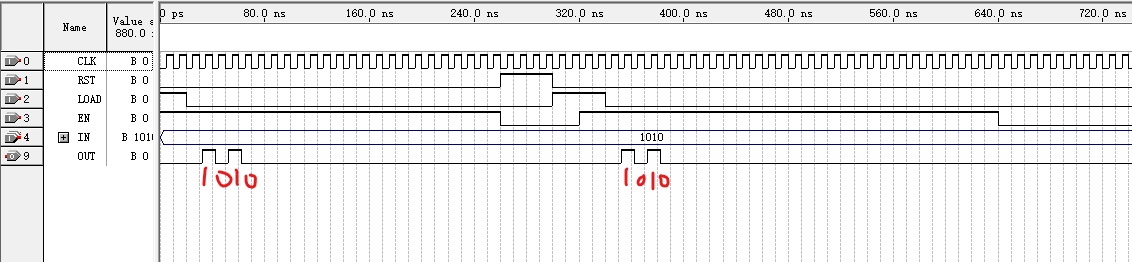

本实验规定输入信号是4位位宽,如果移位使能有效,4位输入信号同时输入,最高位先输出,移位寄存器中剩下的3位信号往右移一位,同时最低位补零;

如果加载使能有效,输入端重新输入4位信号,寄存器连续依次输出4位输入信号。

实验代码:

module shift_register_02(

RST , // 异步复位, 高有效

CLK , // 时钟,上升沿有效

EN , // 输入数据串行移位使能

LOAD , //输入数据加载使能

IN , // 输入串行数据

OUT ); // 并行输出数据

input RST, CLK, EN, LOAD;

input [3:0]IN;

output OUT;

reg [3:0] shift_R;

reg OUT;

// shift_R 会被编译为D触发器

always @ (posedge CLK or posedge RST or posedge LOAD) begin

if(RST) //如果复位信号有效

shift_R[3:0] <= 0; //4个D触发器数据全部清零

else begin

if(LOAD) begin //如果复位信号无效,加载使能有效

shift_R[3:0] <= IN[3:0]; //4位输入信号全部送到D触发器中

end

else begin

if(EN) begin //如果复位信号无效,加载使能无效,移位使能有效

shift_R[3:1] <= shift_R[2:0];

shift_R[0] <= 0;

OUT = shift_R[3];

end

else begin // 使能无效保持不动

shift_R[3:0] <= shift_R[3:0];

end

end

end

end // end always

endmodule

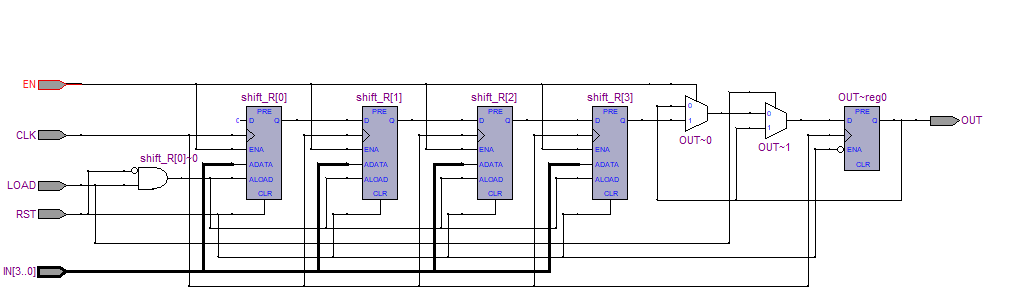

RTL Viewer:

时序仿真图:

最后

以上就是热情小刺猬最近收集整理的关于带加载使能和移位使能的并入串出移位寄存器的全部内容,更多相关带加载使能和移位使能内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复