长度为n=6的序列信号110111

循环移位寄存器

会消耗较多的寄存器资源。需要n个寄存器,也就是6个。

由于输入输出之间没有组合电路,不需要组合逻辑反馈运算,因此电路工作频率高,但问题在于移位寄存器的长度取决于序列长度,占用电路面积大。

module seq_gen(

input clk,

input rst_n,

output seq );

reg [5:0]out_seq;

always@(posedge clk or negedge rst_n)

if(!rst_n) out_seq <= 8'b110111;

else out_seq <= {out_seq[4:0],out_seq[5]};

assign seq = out_seq[5];

循环移位寄存器+组合逻辑电路

其设计按以下步骤进行:

(1)根据给定序列信号的循环周期n,确定移位寄存器位数m,2^(m-1) <n≤ 2^m

(2)确定移位寄存器的n个独立状态。将给定的序列码按照移位规律每m位一组,划分为n个状态。若n个状态中出现重复现象,则应增加移位寄存器位数。用m+1位再重复上述过程,直到划分为n个独立状态为止.

(3)根据n个不同的状态列出移位寄存器的态序表和反馈函数表,求出反馈函数F的表达式。

对于“100111”序列的信号发生器。

首先,确定所需移位寄存器的个数m。因n=6,故m≥3。

然后,确定移位寄存器的六个独立状态。

按照规律每三位一组,划分六个状态为100、001、011、111、111、110。

其中状态111重复出现,故取m=4,并重新划分状态,得到:1001、0011、0111、1111、1110、1100。因此确定m=4。

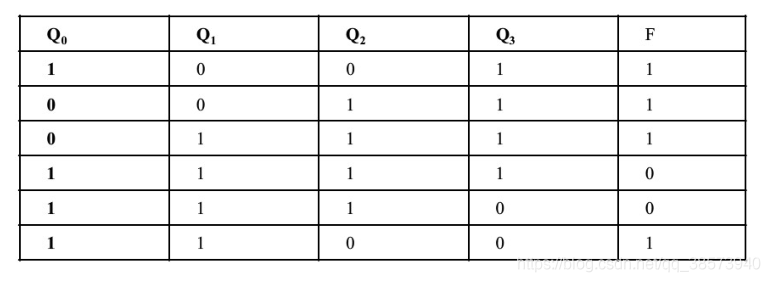

第三,列态序表和反馈激励函数表,求反馈函数F的表达式。

always @(posedge clk)

if(load)

Q<=D;

else

Q<={Q[2:0],w1};

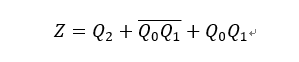

assign w1=(~Q[3])|((~Q[1])&(~Q[0]))|(~Q[3]&(~Q[2]));

assign out=Q[3];

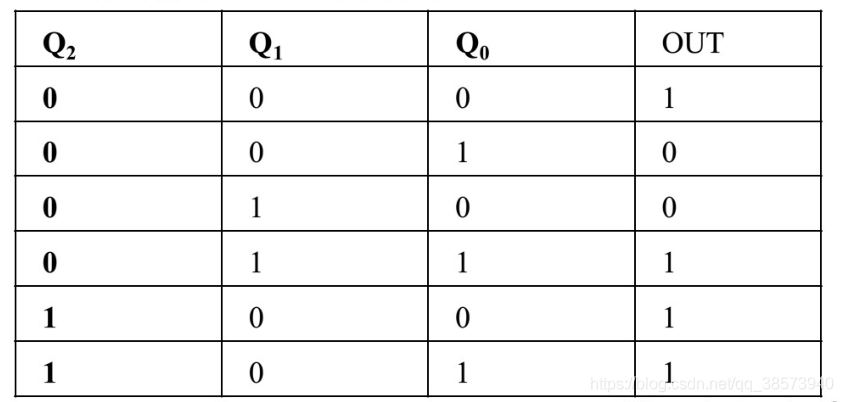

计数器+组合逻辑

序列信号的长度为6,需选用模6计数器,寄存器3个。

根据计数值列输出真值表

always @(posedge clk)

if(!reset)

count<=3'b000;

else

counter<=counter+1;

assign out=counter[2]|((counter[1])&(~counter[0]))|(counter[1]&counter[0]);

https://blog.csdn.net/qq_38573940/article/details/109440396

最后

以上就是如意蜻蜓最近收集整理的关于Verilog实现序列信号发生器的全部内容,更多相关Verilog实现序列信号发生器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复