multisim仿真文件:1001序列检测器(mealy机)-单片机文档类资源-CSDN下载

modelsim仿真文件:1001序列检测器modelsim仿真和测试文件-单片机文档类资源-CSDN下载

实验报告:1001序列检测器实验报告-单片机文档类资源-CSDN下载

电 子 科 技 大 学

- 课程设计名称: 1001序列检测器

- 设计要求

设计一个两位十进制数的BCD码检测器,待检测的两位十进制数来自每组某位同学的学号最后2位数。当检测到待测序列后,输出为高电平,否则输出为0。要求分别采用Moore机和Mealy机实现,给出仿真波形,并分析比较两种设计在波形上的区别。

- 设计原理

- 以学号最后两位数09为例,09的BCD码为1001,即设计1001序列检测器。

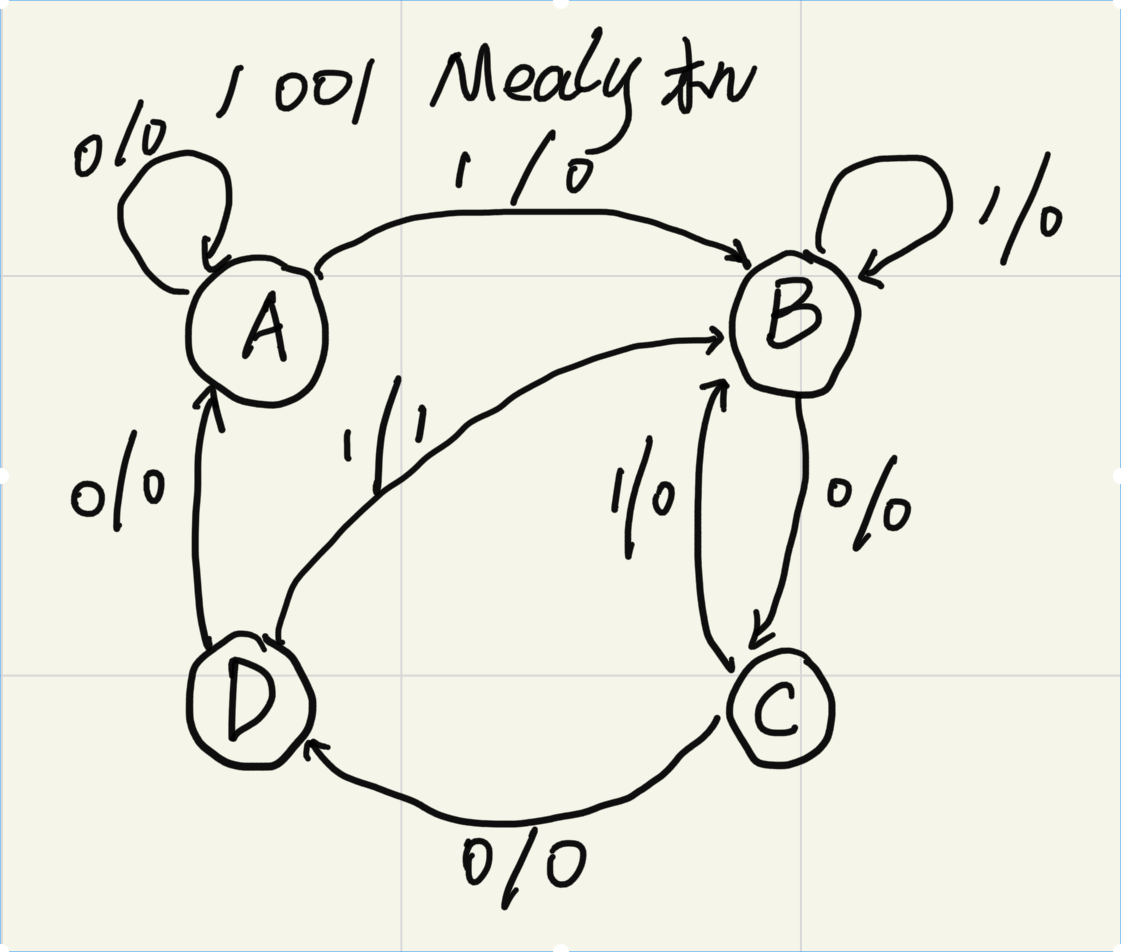

- 1001序列检测器mealy机状态图

状态转移表:

|

|

| X | |

| Q2 | Q1 | 0 | 1 |

| 0 | 0 | 00/0 | 01/0 |

| 0 | 1 | 11/0 | 01/0 |

| 1 | 1 | 10/0 | 01/0 |

| 1 | 0 | 00/0 | 01/1 |

JK触发器特征方程为:Q*=JQ’+K’Q

由状态转移表可得:

Q*2=X’Q1Q’2+Q1X’Q2 Q*1=XQ’1+(X’Q2)’Q1

即J1=X’Q1;K1=(Q1X’)’’;J2=XQ’1;K2=X’Q2。

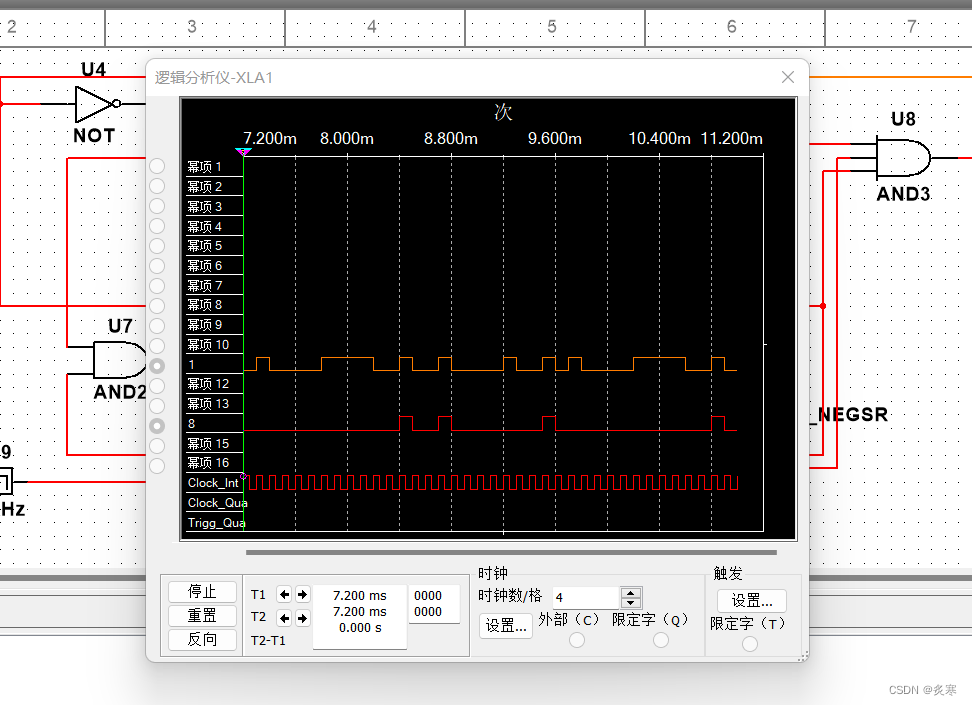

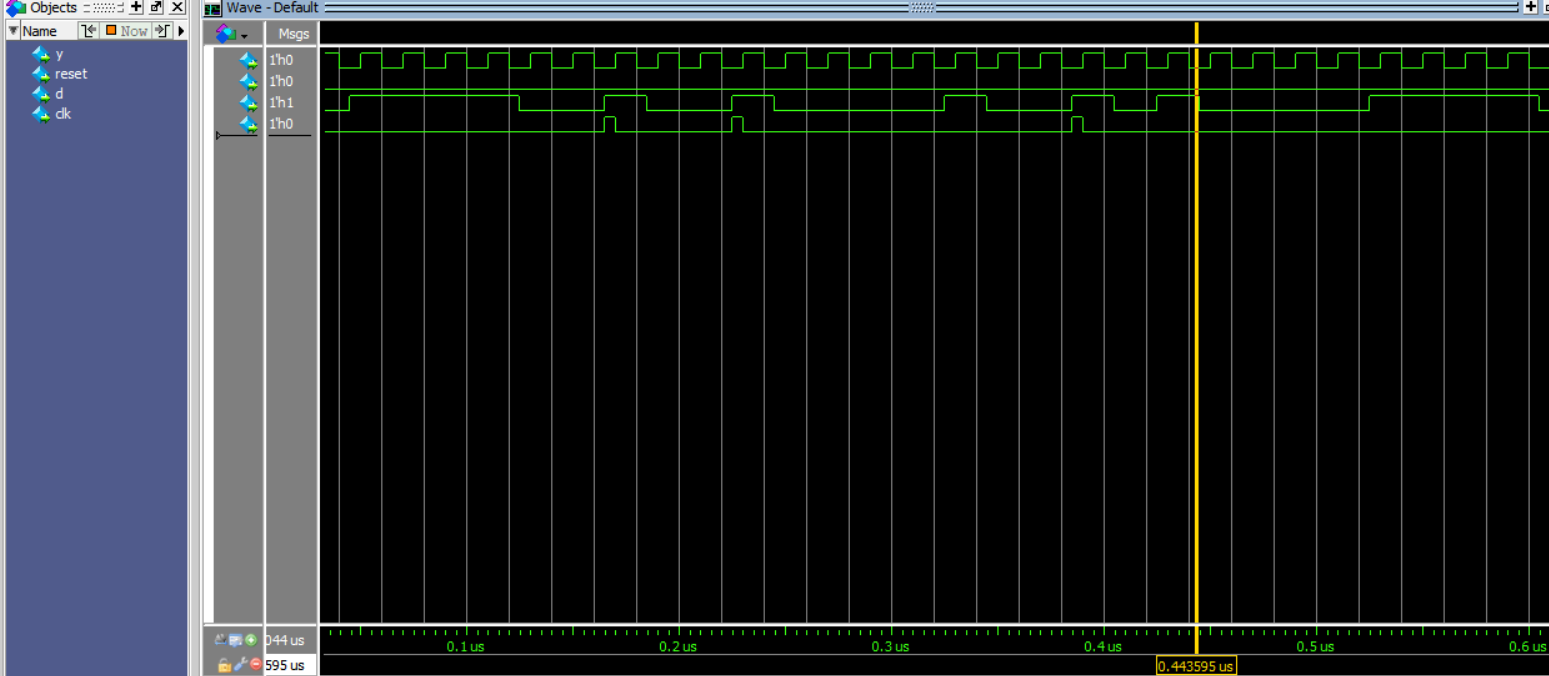

仿真图如下:

1001序列检测器(mealy机)-单片机文档类资源-CSDN下载

对该电路输入0011_1100_1001_0000_1001_0100信号时,应得到00000000100100000001信号输出。

输出波形如下:

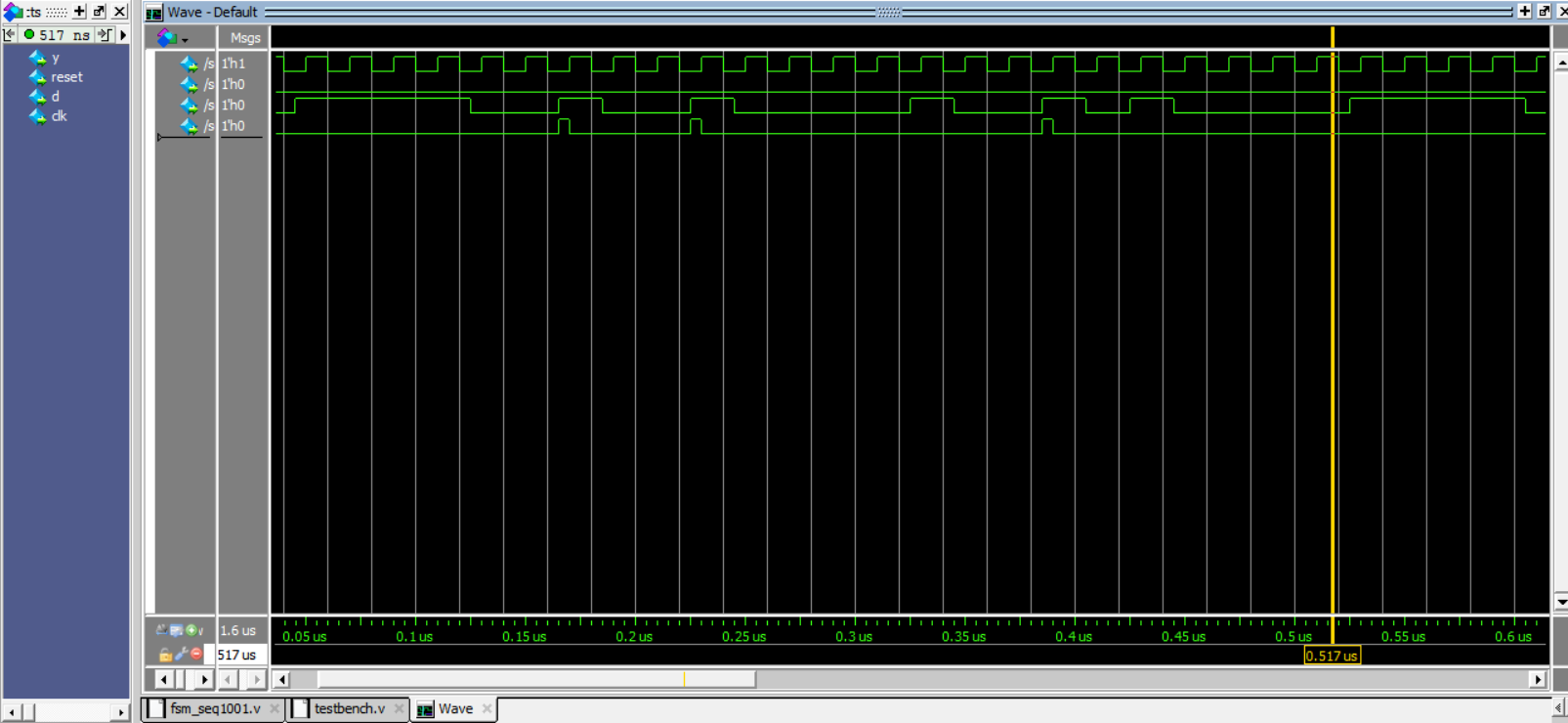

软件仿真:

仿真代码:

module sequential_detector(clk, reset, d, y);

//输入输出端口定义

input clk, reset, d;

output y;

//内部寄存器及连线定义

reg [2 : 0] state;

wire y;

//状态编码

parameter idle = 2'b00, s1 = 2'b01, s2 = 2'b11, s3 = 2'b10;

//状态机实现

always@(posedge clk or posedge reset)

......

......

assign y = (state == s3 && d == 1) ? 1 : 0;

endmodule

测试文件代码:

`timescale 1ns/1ns

`define halfperiod 10

module sequential_detector_t(clk, reset, d, y);

//定义要观察的的信号

output clk, reset, d, y;

//定义内部连线及寄存器

reg clk, reset;

reg [23 : 0] data; //定义一个24位的寄存器用于存放待测数据码

wire d, y;

//生成测试信号逻辑

initial

begin

clk = 0; reset = 0;

#5 reset = 1;

#20 reset = 0; data = 24'b0011_1100_1001_0000_1001_0100;

......

......

输出波形:

-

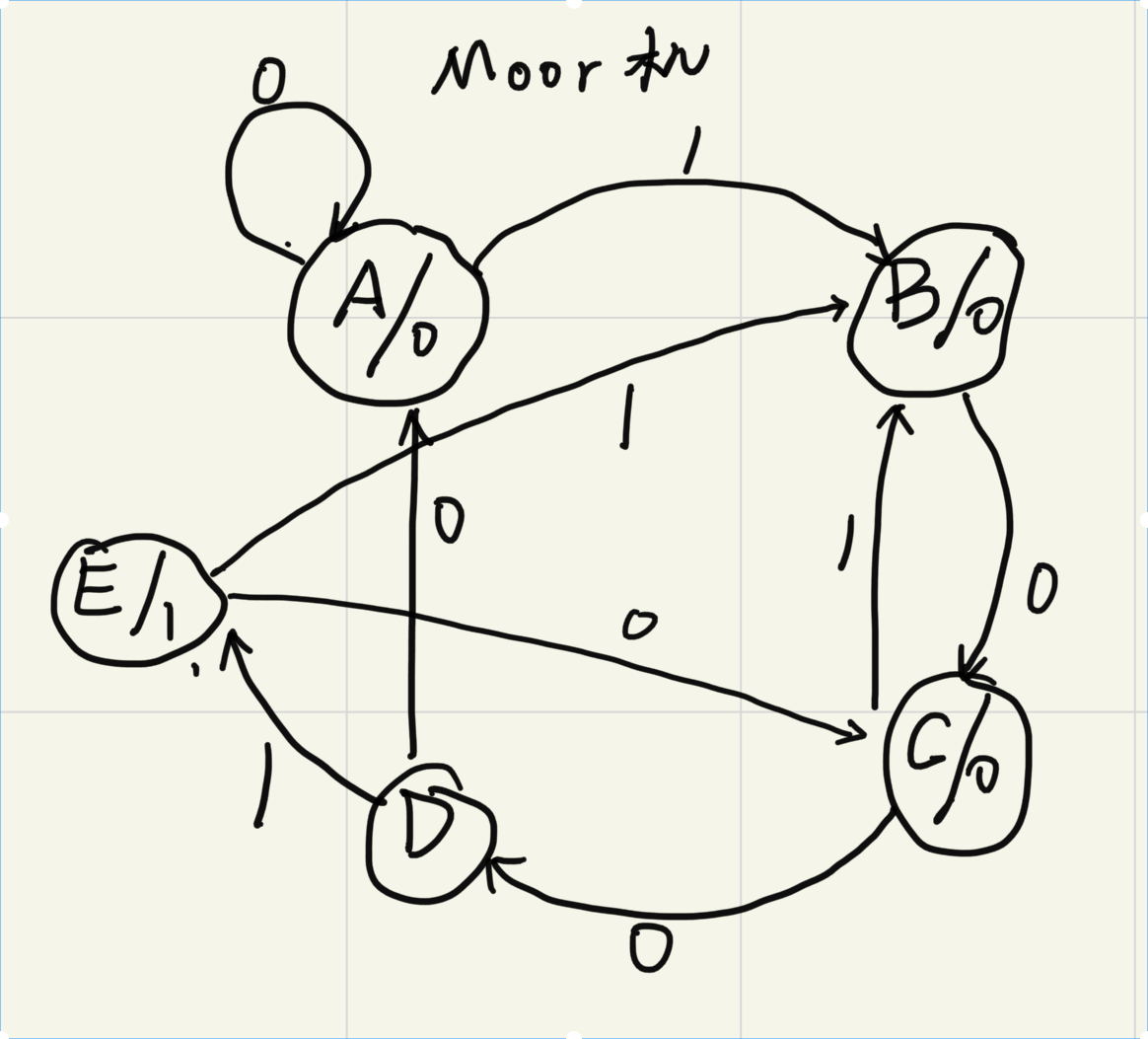

- Moor机实现

仿真代码:

module state_test(clk, reset, d, y);

input clk, reset, d;

output y;

reg [2 : 0] state;

wire y;

parameter idle = 3'b000, s1 = 3'b001, s2 = 3'b011, s3 = 'b010,s4 = 3'b110;

always@(posedge clk or posedge reset)

begin

if(reset) state <= idle;

else

begin

casex(state)

......

......

endmodule

测试代码:

`timescale 1ns/1ps

`define halfperiod 10

module state_test_tb(clk, reset, d, y);

output clk, reset, d, y;

reg clk, reset;

reg [23 : 0] data;

wire d, y;

initial

begin

clk = 0; reset = 0;

#5 reset = 1;

#20 reset = 0; data = 24'b0011_1100_1001_0000_1001_0100;

......

......

输出波形:

最后

以上就是顺心手机最近收集整理的关于1001序列检测器的全部内容,更多相关1001序列检测器内容请搜索靠谱客的其他文章。

发表评论 取消回复