行为级建模,结构化过程语句;

always语句包括的所有行为语句构成了一个always语句块。该always语句块从仿真0时刻开始执行其中的行为语句;最后一条执行完成后,再开始执行其中的第一条语句,如此往复循环,直到整个仿真结束。因此,always语句块常用于对数字电路中一组反复执行的活动进行建模。比如大家熟知的时间信号发生,每半个时钟周期时钟信号翻转一次。

module clock(output reg clock)

//在零时刻把clock变量初始化

initial

clock = 1'b0;

//每半个周期把clock信号翻转一次

always

#10 clock=~clock;

initial

#1000 $finish;//1000个时间单位后,停止仿真

endmodulewarning:在这个例子中,clock是在initial语句中被初始化的,如果放在always语句中,always每次执行都将初始化clock!(而不是只执行一次)所以,从C语言的角度看,always像一个无限循环语句

看下面一个例子;

always @(posedge clock)

begin

......

end这就是条件循环语句了。

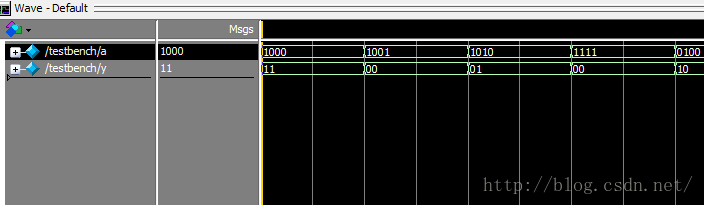

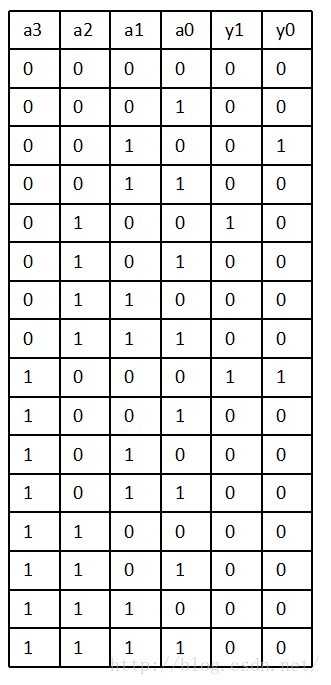

下面是今天做个一个小栗子,4-2线编码器:

module enc4to2 (

input [3:0] a,

output [1:0] y

);

assign y[1] = ~a[1] & ~a[0];

assign y[0] = ~a[2] & ~a[0];

endmodule

给出激励文件:

`timescale 100ns/1ns

module testbench ;

wire [1:0] y ;

reg [3:0] a ;

enc4to2

DUT (

.y (y ) ,

.a (a ) );

initial

begin

a[0]=0;

a[1]=0;

a[2]=0;

a[3]=1;

end

always #2

begin

a[0]=~a[0];

end

always #4

begin

a[1]=~a[1];

end

always #6

begin

a[2]=~a[2];

end

always #8

begin

a[3]=~a[3];

end

endmodule激励文件是用modesim自动生成的,自己写个initial之类就好

最后

以上就是合适洋葱最近收集整理的关于总结Verilog中always语句的使用的全部内容,更多相关总结Verilog中always语句内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复