(1) 在 Quartus-II 中自己用门电路设计一个D触发器,并进行仿真,时序波形验证;

参考附件1“Quartus-II输入原理图及仿真步骤.docx”;

(2)在 Quartus-II 中直接调用一个D触发器电路,进行仿真,时序波形验证,与2做比较。

这目录

- 一.Quartus-II 13 和Modelsim的安装

- 二.什么是D触发器?

- 三.D触发器de设计与仿真

- 四.调用一个D触发器电路进行仿真

- 五.写一个D触发器并仿真

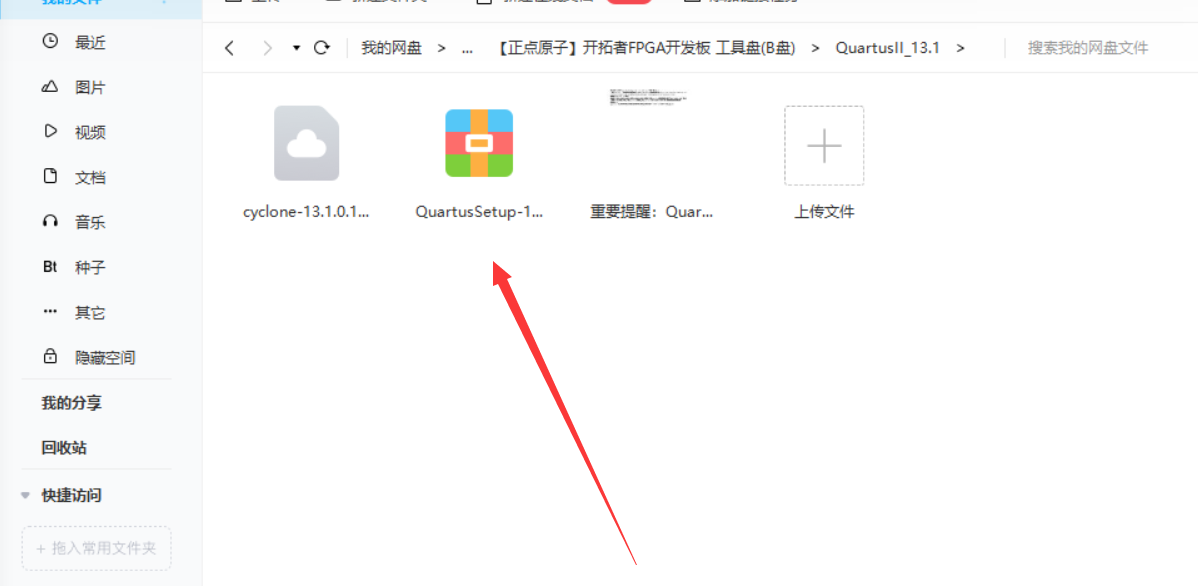

一.Quartus-II 13 和Modelsim的安装

资料链接 https://pan.baidu.com/s/1a9d-bq9RZmWrRV542X4IEA

提取码:ifte

下载

安装参考网址:

https://blog.csdn.net/qq_43279579/article/details/115158140

二.什么是D触发器?

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

D触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。

D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。

对于边沿D触发器,由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等等。

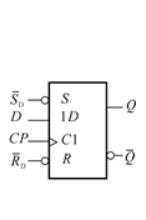

1.结构

D触发器(data flip-flop或delay flip-flop)由4个与非门组成,其中G1和G2构成基本RS触发器。电平触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。边沿D触发器可由两个D触发器串联而成,但第一个D触发器的CP需要用非门反向。

2.工作原理

SD和RD接至基本RS触发器的输入端,它们分别是预置和清零端,低电平有效。当SD=1且RD=0时(SD的非为0,RD的非为1,即在两个控制端口分别从外部输入的电平值,原因是低电平有效),不论输入端D为何种状态,都会使Q=0,Q非=1,即触发器置0;当SD=0且RD=1(SD的非为1,RD的非为0)时,Q=1,Q非=0,触发器置1,SD和RD通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。

工作过程如下:

1)CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5非=D非。

2)当CP由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5非=D非,Q4=Q6非=D。由基本RS触发器的逻辑功能可知,Q=Q3非=D。

3)触发器翻转后,在CP=1时输入信号被封锁。这是因为G3和G4打开后,它们的输出Q3和Q4的

状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS触发器的路径;该反馈线起到了使触发器维持在1状态和阻止触发器变为0状态的作用,故该反馈线称为置1维持线,置0阻塞线。Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。Q4输出端至G6反馈线起到使触发器维持在0状态的作用,称作置0维持线;Q4输出至G3输入的反馈线起到阻止触发器置1的作用,称为置1阻塞线。因此,该触发器常称为维持-阻塞触发器。

总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。与主从触发器相比,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度。 /span>。由基本RS触发器的逻辑功能可知,Q=Q3非=D。

特征

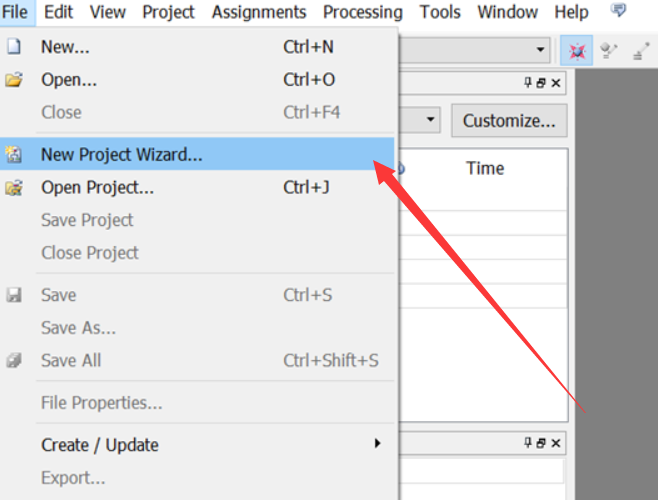

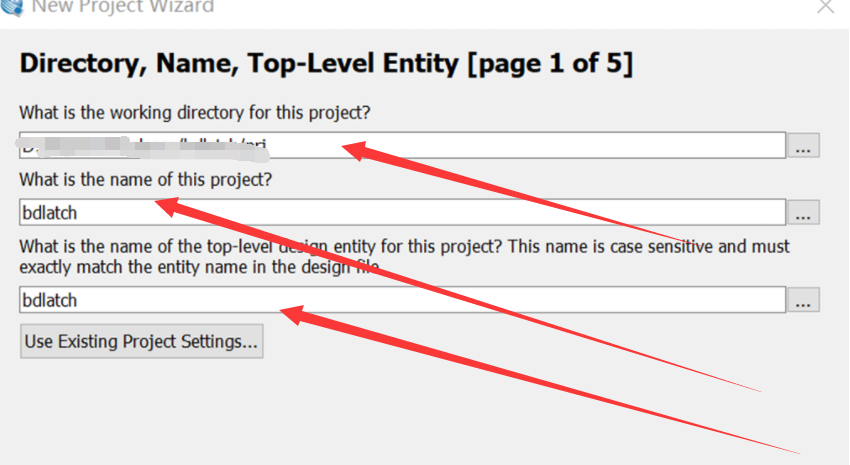

三.D触发器de设计与仿真

1.创建

新建一个工程

选择位置/名称等

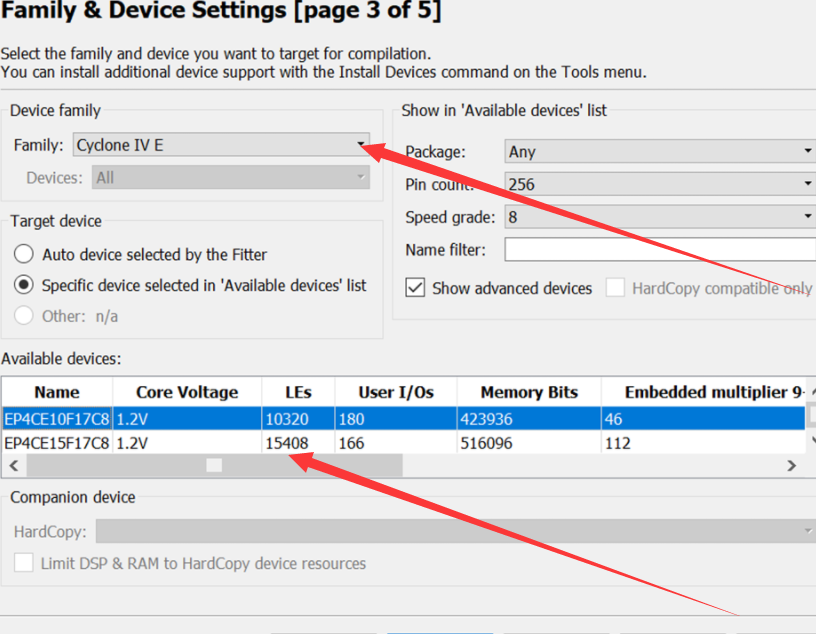

选择芯片系列及类型

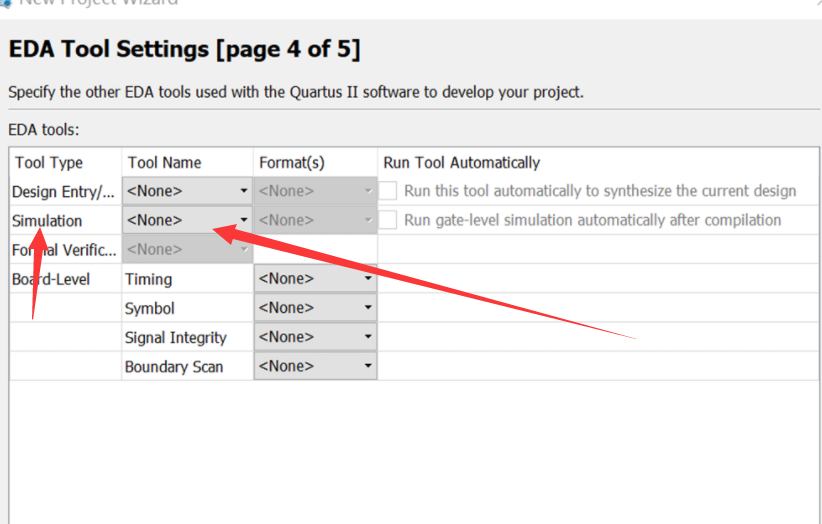

EDA工具-simulation中选None

然后finish

2.波形文件

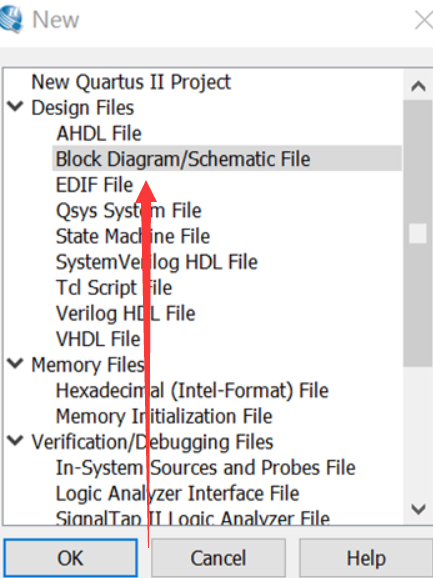

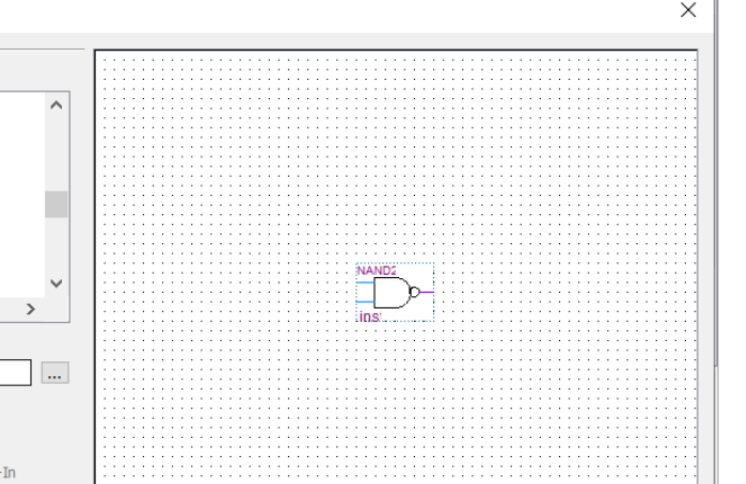

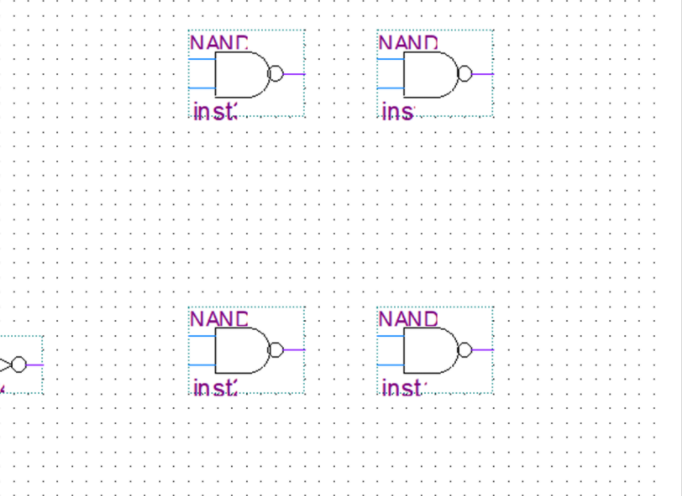

选择nand2,二个输入的与非门,依次添加四个and2和一个非门not

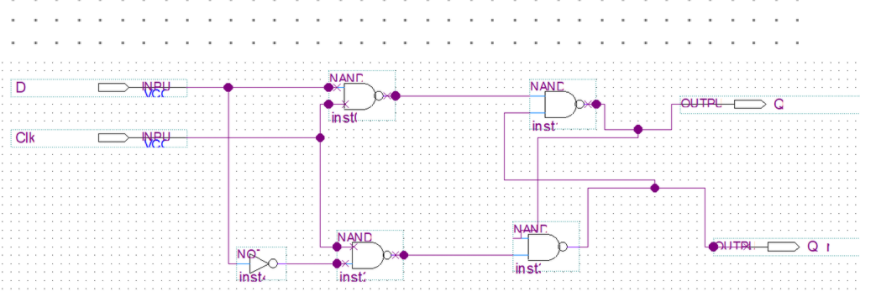

通过工具栏上面输入输出工具,以及连线工具,设计出以下的电路图。

3.保存以及编译

保存文件后启动分析与综合,编译原理图文件

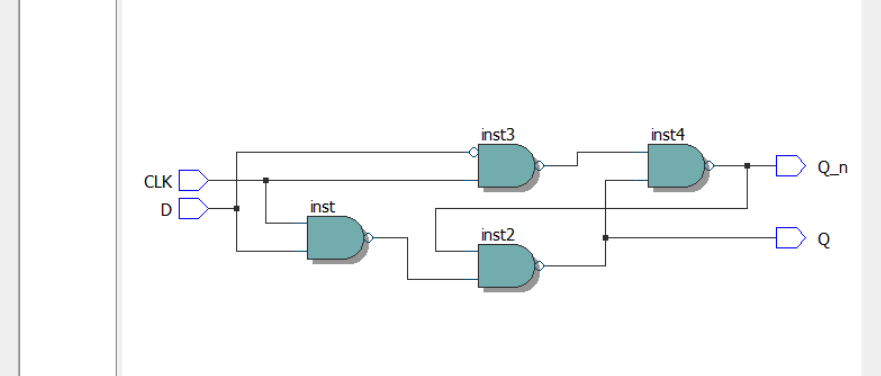

编译后,用rtl viewer,可以看到下面硬件电路图。

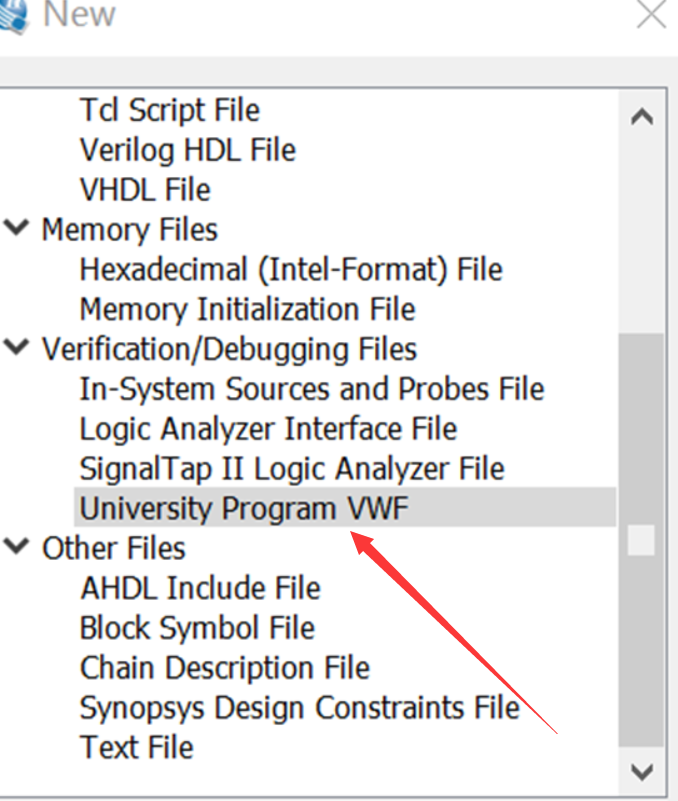

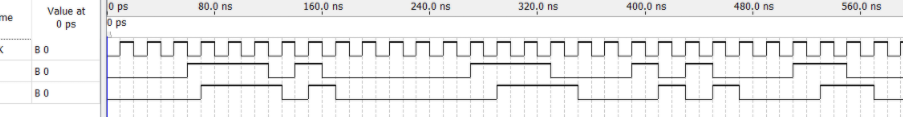

4.创建格式文件,输入激励

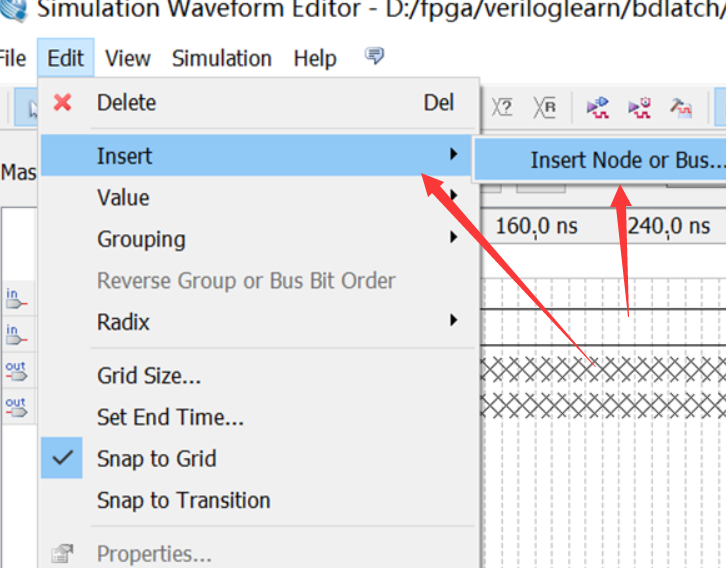

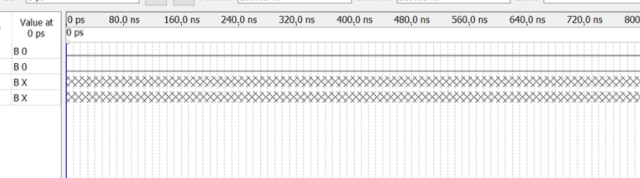

插入Node和bus后,得到下面的波形

进行仿真

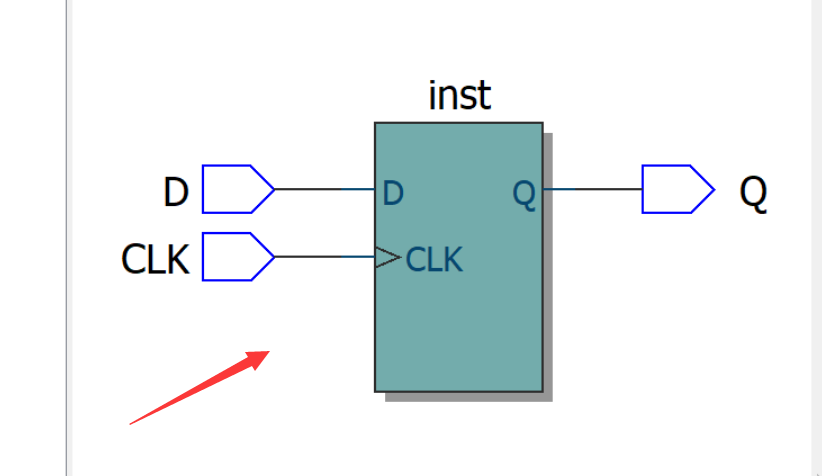

四.调用一个D触发器电路进行仿真

1.新建工程

创建工程文件如上相同步骤

2.新建文件

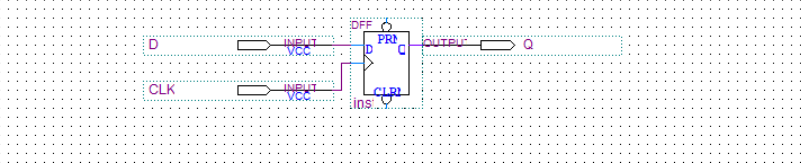

调用D触发器

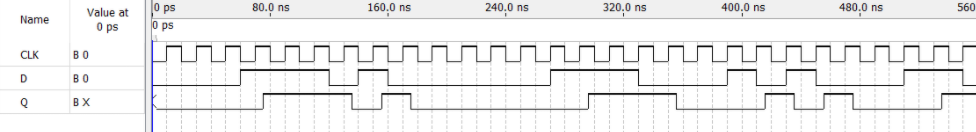

3.编译原理图

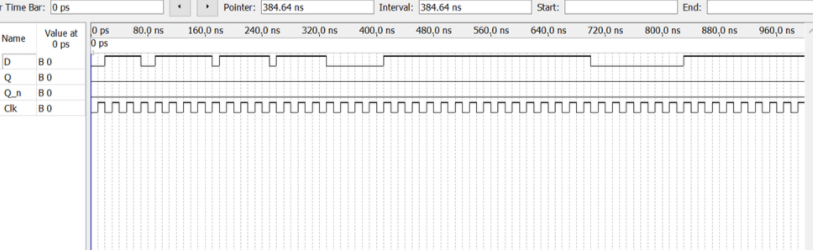

4.创建格式文件并仿真

创建vwm格式波形文件方法如上

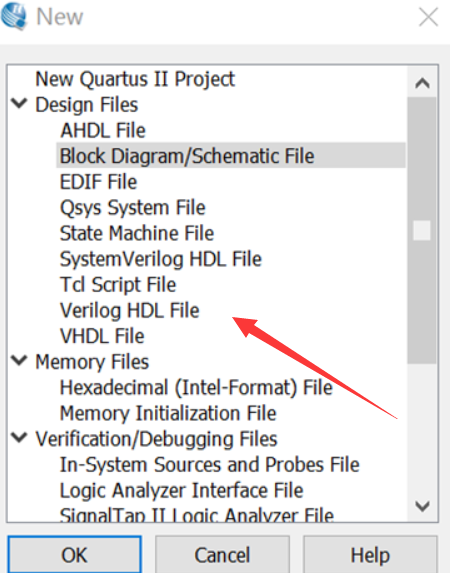

五.写一个D触发器并仿真

1.新建工程

方法如上

2.编写Verilog文件

代码块:

//dwave是文件名

module dwave(d,clk,q);

input d;

input clk;

output q;

reg q;

always @ (posedge clk)//我们用正的时钟沿做它的敏感信号

begin

q <= d;//上升沿有效的时候,把d捕获到q

end

endmodule

、

保存并编译

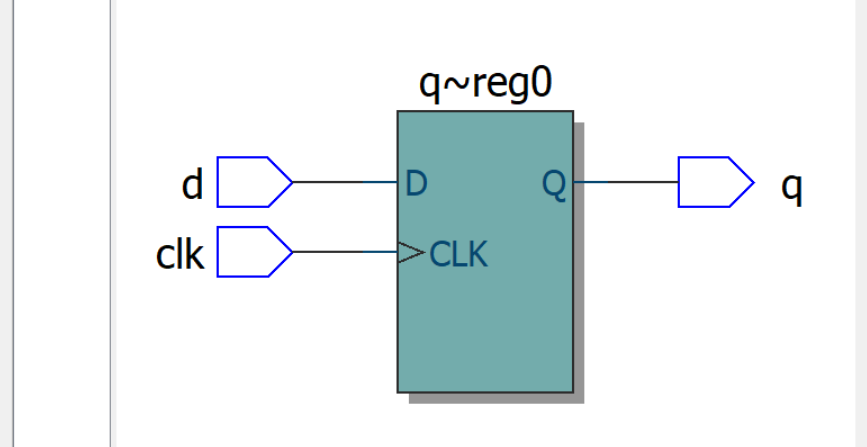

3.电路图

4.利用Verilog代码实现仿真

代码块

module test03_tb;

reg clk,rst,clr,d;

wire q;

initial

begin

clk=1'b0;

forever #10 clk=~clk;

end

initial

begin

clr=1'b0;

rst=1'b0; d=1'b0;

#10 rst=1'b1;clr=1'b0;d=1'b0;

#10 rst=1'b1;clr=1'b1;d=1'b1;

#10 rst=1'b0;clr=1'b0;d=1'b1;

#20 d=1'b0;

#20 d=1'b1;

end

test03 U1(.clk(clk),.clr(clr),.rst(rst),.d(d),.q(q));

endmodule

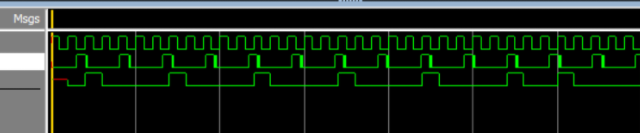

5.效果

如图

最后

以上就是昏睡蜗牛最近收集整理的关于安装Quartus-II的数字电路的仿真与验证一.Quartus-II 13 和Modelsim的安装二.什么是D触发器?三.D触发器de设计与仿真四.调用一个D触发器电路进行仿真五.写一个D触发器并仿真的全部内容,更多相关安装Quartus-II的数字电路的仿真与验证一.Quartus-II内容请搜索靠谱客的其他文章。

发表评论 取消回复