文章主要参考---FPGA数字逻辑设计教程,郑利浩、王荃等译,电子工业出版社.[p 140--p 147]

触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,可用做数字信号的寄存,移位寄存,分频和波形发生器等。

1. D触发器的构成原理及真值表

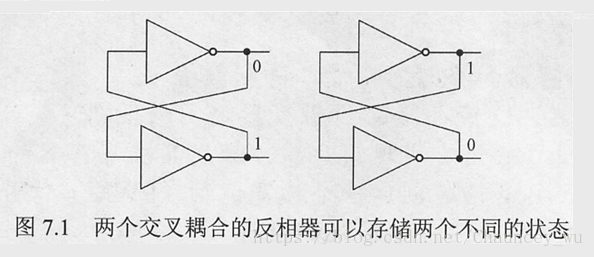

1.1 两个交叉耦合的反向器可以存储两个不同的状态

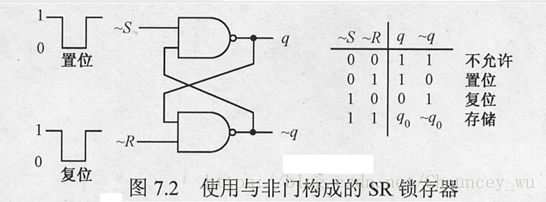

在此基础上,可以利用两个与非门构成SR锁存器

1.2 SR锁存器

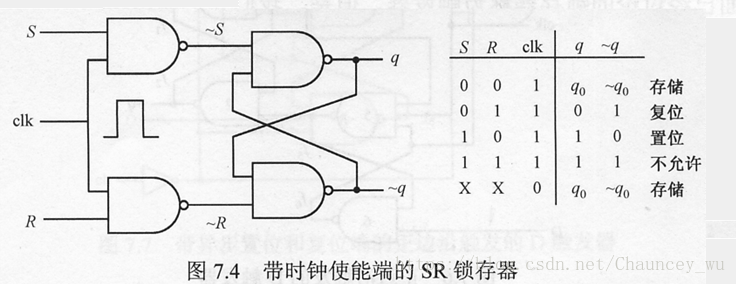

上面的SR锁存器增加两个与非门,可以构成时钟触发SR锁存器。

1.3 时钟触发SR锁存器的电路原理图以及真值表

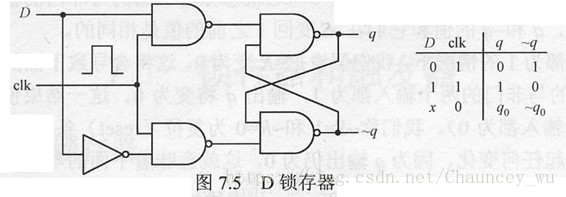

SR锁存器有个很明显的弊端,S和R不能同1,因为样会导致q和~q矛盾。若要消除这种不允许的状态,保证S和R总是取相反的逻辑值即可,于是变形成了D锁存器。

1.3 D锁存器

D锁存器只有当时钟信号为0时,才能进入存储状态。

通过分析我们可以知道,D锁存器是一种电平触发,但实际我们希望锁存器q在特定的时刻(如时钟信号的上升沿)所存D的值。这就导致了边沿触发器的产生。

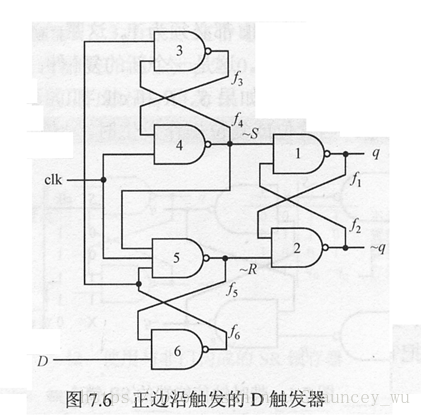

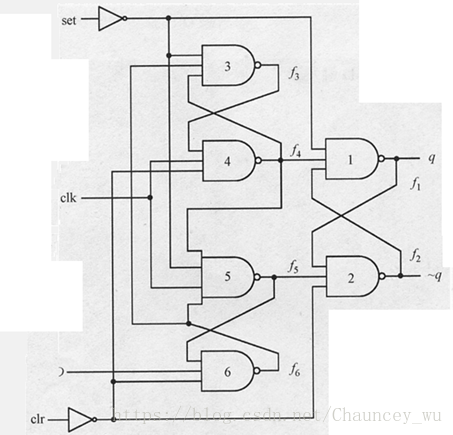

1.4 边沿触发的D触发器

在时钟信号clk的上升沿,D的值被锁存在q中。

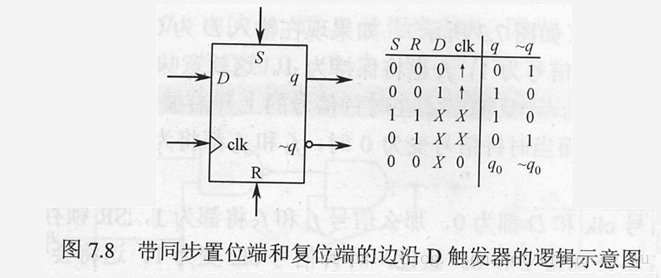

(上图是带异步置位和复位端的正边沿触发的D触发器,当输入SET(S)为1时,输出q立即变为1,而不用等到下了一个时钟上升沿的到来。同样地,当clr(R)为1时,输出q也立即变为0,而不用等到下一个时钟上升沿的到来。)

最后

以上就是动人乌龟最近收集整理的关于D触发器的工作原理以及Verilog代码(一/二)的全部内容,更多相关D触发器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复