初学FPGA第一天,一遍听课一边总结的笔记 分析不一定准确 若有错误请务必指出

来源:小明教IC-1天学会verilog(2)_哔哩哔哩_bilibili

Verilog HDL基础知识 - 百度文库

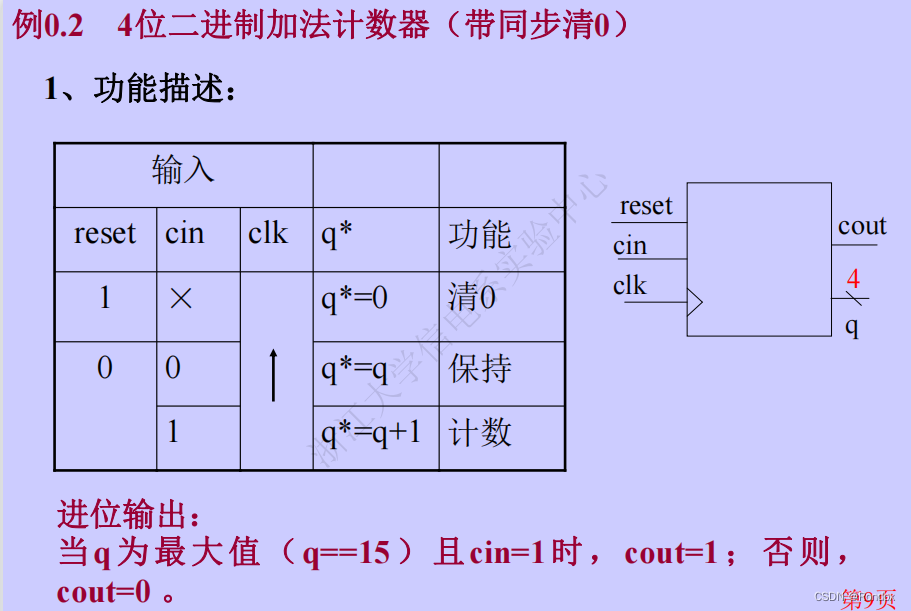

一.分析计数器:

从表中看出

1.q*应该是q的下一个数值 比如q^n+1和q^n的关系 clk的向上箭头表示时钟上升沿触发

2.reset为1时cin中的x意思是无论cin取何值,遇到时钟上升沿时,q*置0

3.reset为0且cin为0时,遇到时钟上升沿时,q*=q,保持计数

4.reset为0且cin为1时,遇到时钟上升沿时,q*=q+1,开始计数

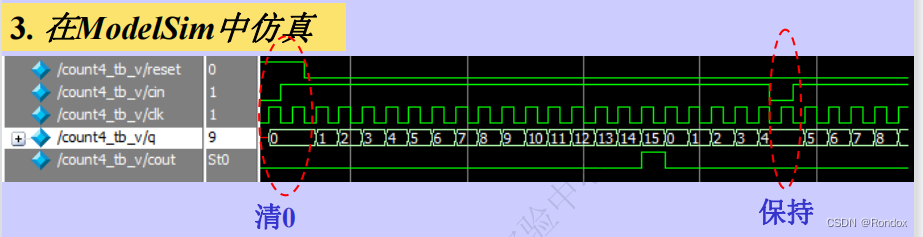

5.同步清0指的是 当4位达到最大值的时候(2进制的1111,也就是10进制的15),遇到上升沿之后并且再+1的情况下,会导致溢出此时溢出位cout变成1,此时遇到时钟上升沿的时候,q清0

(如果是异步清0,在+1后会在短暂时间后直接清0,而不会先经过上升沿再触发清0)

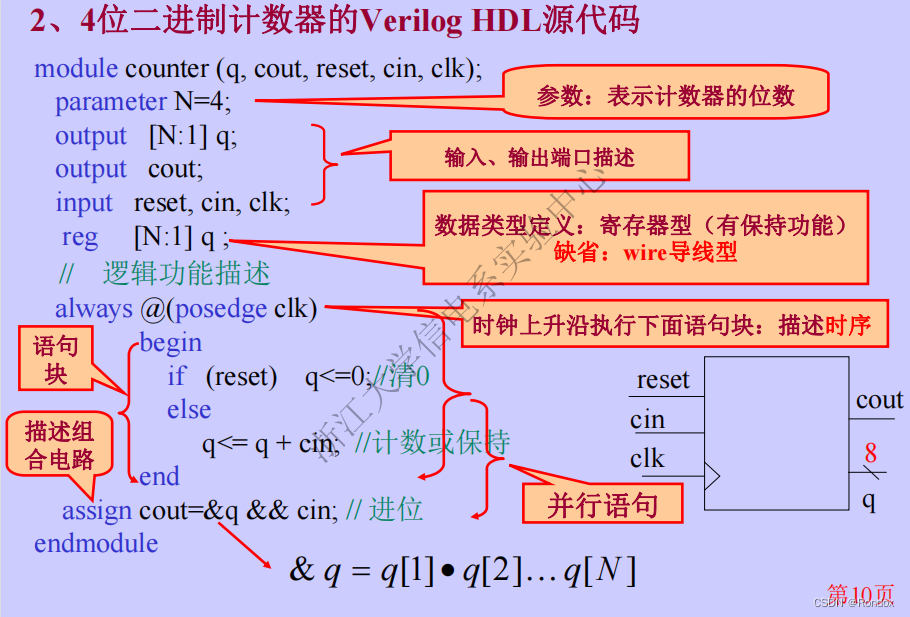

二.分析VerilogHDL源代码

module counter (q, cout, reset, cin, clk);

parameter N=4; //定义N用来复用这个值

output [N:1] q; //指明端口性质 位宽4到1 从1234,4比特 4bit 习惯性高位写在左边

//此处q没有显式声明而是output ,系统默认表示wire类型

output cout; //表示溢出 此处cout没有显式声明而是output ,系统默认表示wire类型

input reset, cin, clk;

reg [N:1] q ; //定义寄存器 4位宽 此处重申了q是reg类型,显式声明

//为什么定义寄存器?

//因为寄存器有储存功能,存储一个值,用于存储某一个时刻计算出来的值用于下一次累加

//计数器在计数过程中有q是在下一次上升沿来之前保持寄存状态

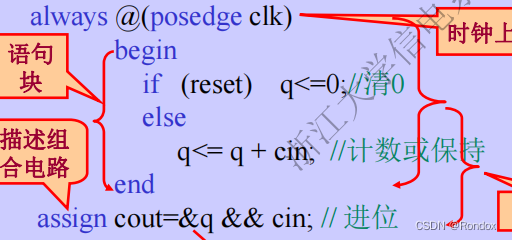

// 逻辑功能描述 clk时钟参与,所以时序逻辑

always @(posedge clk) //每来一次上升沿 就会执行一次 begin与end之间的语句块 并行

begin

if (reset) q<=0;//清 0

else

q<= q + cin; //计数或保持

end

assign cout=&q && cin; // 与q表示4比特的q各自相与,再与cin

//只有在q的4位全是1的时候&q才能为1 此时再与cin(若cin为0表示保持,此时就不加了,为1就会计数+1),

//满足两个是1的时候cout才会为1

//assign 没有时钟参与,叫做组合逻辑电路,里面没有存储,而且当前的值只与当前右边几个信号的值有关系,而时序逻辑中 q是根据与上一次q的值加上cin的输入得到的计数值

//wire表示一根导线没有储存功能,只能是组合逻辑assign 而组合逻辑表示表达式左边和表达式右边是实时对应的,只要右边变化左边马上发生变化

//而时序逻辑always这边是有触发条件的,上升沿触发的情况下这个逻辑才会执行,begin到end的代码块的执行

//此处类比于Vue的绑定数据(瞬时变化)和react/flutter的state(需要setState()方法触发后才会改变页面的内容)

endmodule

//弹幕内容:

//时序逻辑一定要用非阻塞<=.一旦看到敏感列表有posedge就用<=

//组合逻辑一定要用=,一旦敏感列表没有posedge就用=,看到assign就用=

//时序逻辑和组合逻辑分成不同的模块,即一个always模块里面只能出现非阻塞赋值<=或者=

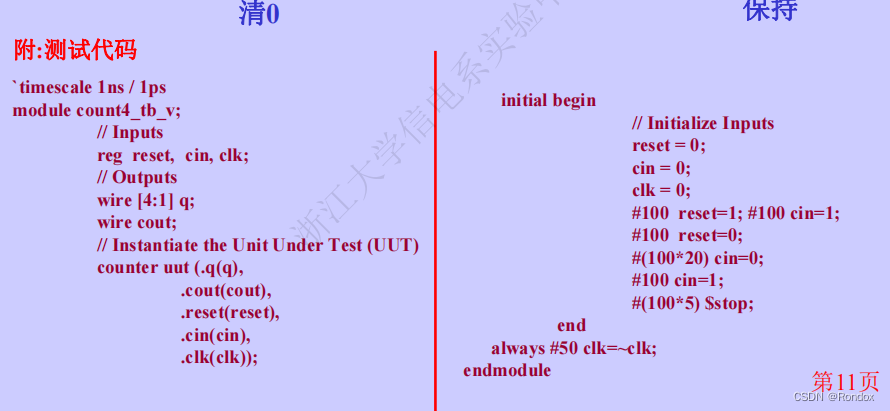

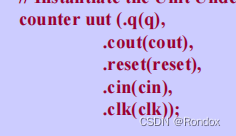

二.分析VerilogHDL TestBench测试源代码

`timescale 1ns / 1ps //1ns表示单位1ns 表示仿真频率1G,1ps指的是仿真的最大精度

module count4_tb_v; //包住测试模块 testbench简写tb

// Inputs

reg reset, cin, clk;

// Outputs

wire [4:1] q;

wire cout;

// Instantiate the Unit Under Test (UUT)

counter uut (.q(q),

.cout(cout),

.reset(reset),

.cin(cin),

.clk(clk));

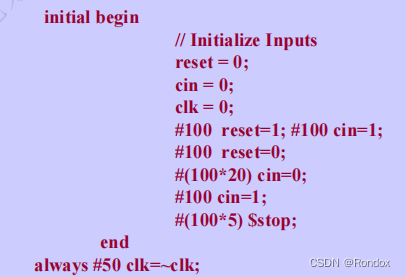

//此处开始初始化,上电,施加激励 不可综合部分

initial begin

// Initialize Inputs 初始resst,cin,clk都设置为0

reset = 0;

cin = 0;

clk = 0;

//强行指定,强加信号为了测试电路 导致不可综合 只是虚拟平台用于测试代码

#100 reset=1; #100 cin=1; //#100 与第一行有关,这时候是100ns,延迟100ns后执行后面的语句

#100 reset=0;

#(100*20) cin=0; //延迟2000ns

#100 cin=1;

#(100*5) $stop; //延迟500ns后仿真停止

end

always #50 clk=~clk;

endmodule最后Verilog分两部分

1.可综合部分

这部分代码用EDA工具做综合,生成具体的硬件电路,乃至于做板图然后最后加工成芯片

但是之后需要测试对不对 所以要用虚拟模块

2.不可综合部分

在上面虚拟模块在端口里面施加下面虚拟信号

之后看波形

最后

以上就是清秀柚子最近收集整理的关于Verilog与FPGA #1 入门:分析一个4位二进制加法计数器的全部内容,更多相关Verilog与FPGA内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复