仅供参考

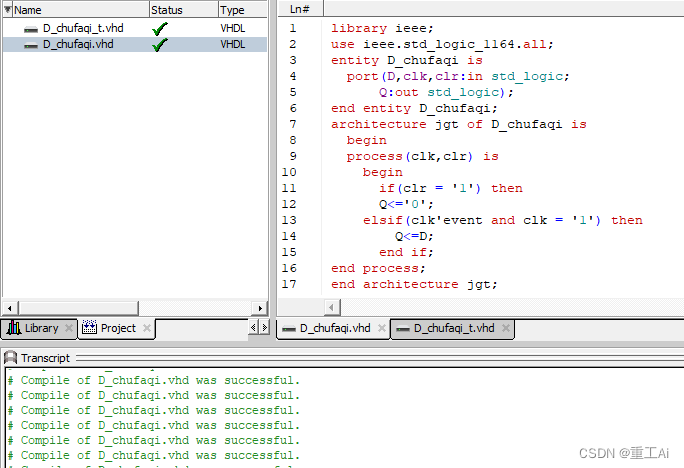

代码截图:

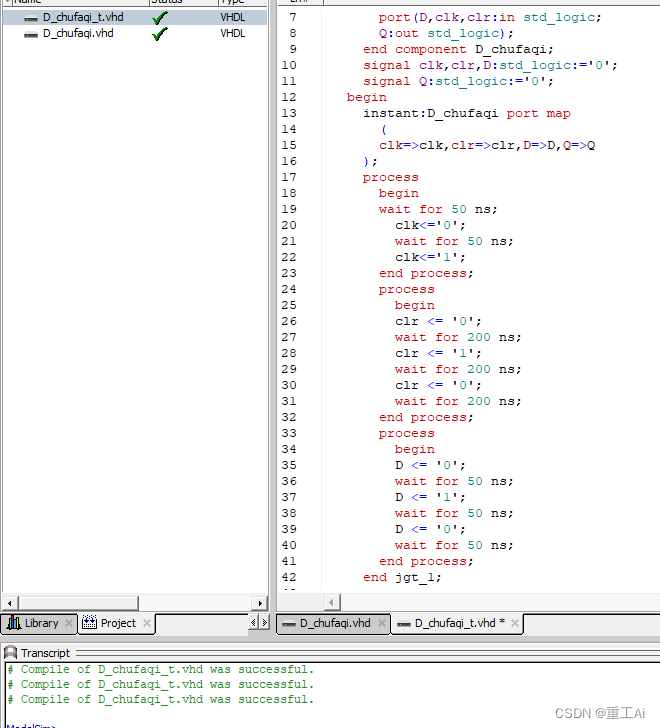

测试代码部分截图(完整代码在结尾):

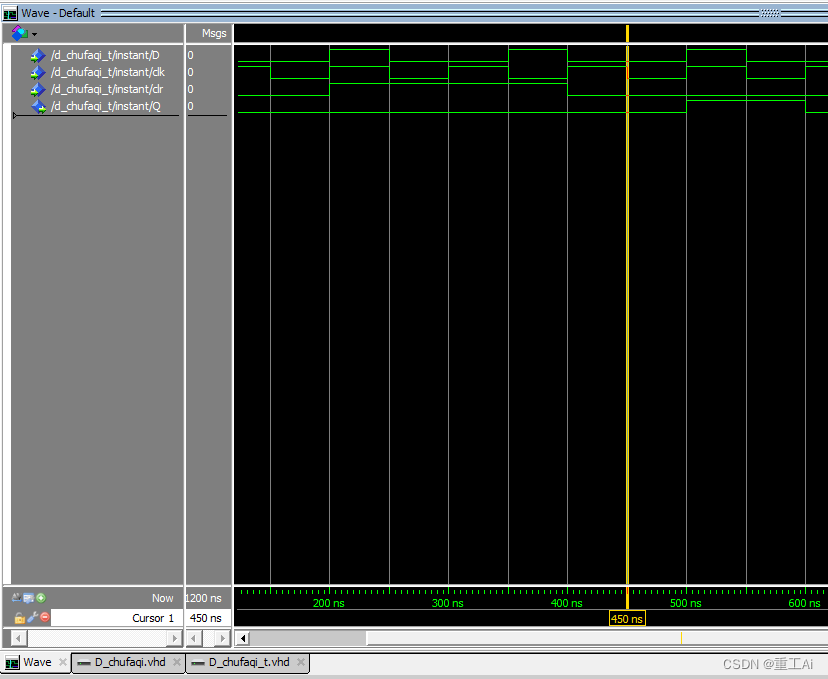

波形截图:

完整代码:

library ieee;

use ieee.std_logic_1164.all;

entity D_chufaqi is

port(D,clk,clr:in std_logic;

Q:out std_logic);

end entity D_chufaqi;

architecture jgt of D_chufaqi is

begin

process(clk,clr) is

begin

if(clr = '1') then

Q<='0';

elsif(clk'event and clk = '1') then

Q<=D;

end if;

end process;

end architecture jgt;

完整测试代码:

library ieee;

use ieee.std_logic_1164.all;

entity D_chufaqi_t is

end entity D_chufaqi_t;

architecture jgt_1 of D_chufaqi_t is

component D_chufaqi is

port(D,clk,clr:in std_logic;

Q:out std_logic);

end component D_chufaqi;

signal clk,clr,D:std_logic:='0';

signal Q:std_logic:='0';

begin

instant:D_chufaqi port map

(

clk=>clk,clr=>clr,D=>D,Q=>Q

);

process

begin

wait for 50 ns;

clk<='0';

wait for 50 ns;

clk<='1';

end process;

process

begin

clr <= '0';

wait for 200 ns;

clr <= '1';

wait for 200 ns;

clr <= '0';

wait for 200 ns;

end process;

process

begin

D <= '0';

wait for 50 ns;

D <= '1';

wait for 50 ns;

D <= '0';

wait for 50 ns;

end process;

end jgt_1;

最后

以上就是闪闪鸵鸟最近收集整理的关于Modelsim异步复位-D触发器仅供参考的全部内容,更多相关Modelsim异步复位-D触发器仅供参考内容请搜索靠谱客的其他文章。

发表评论 取消回复