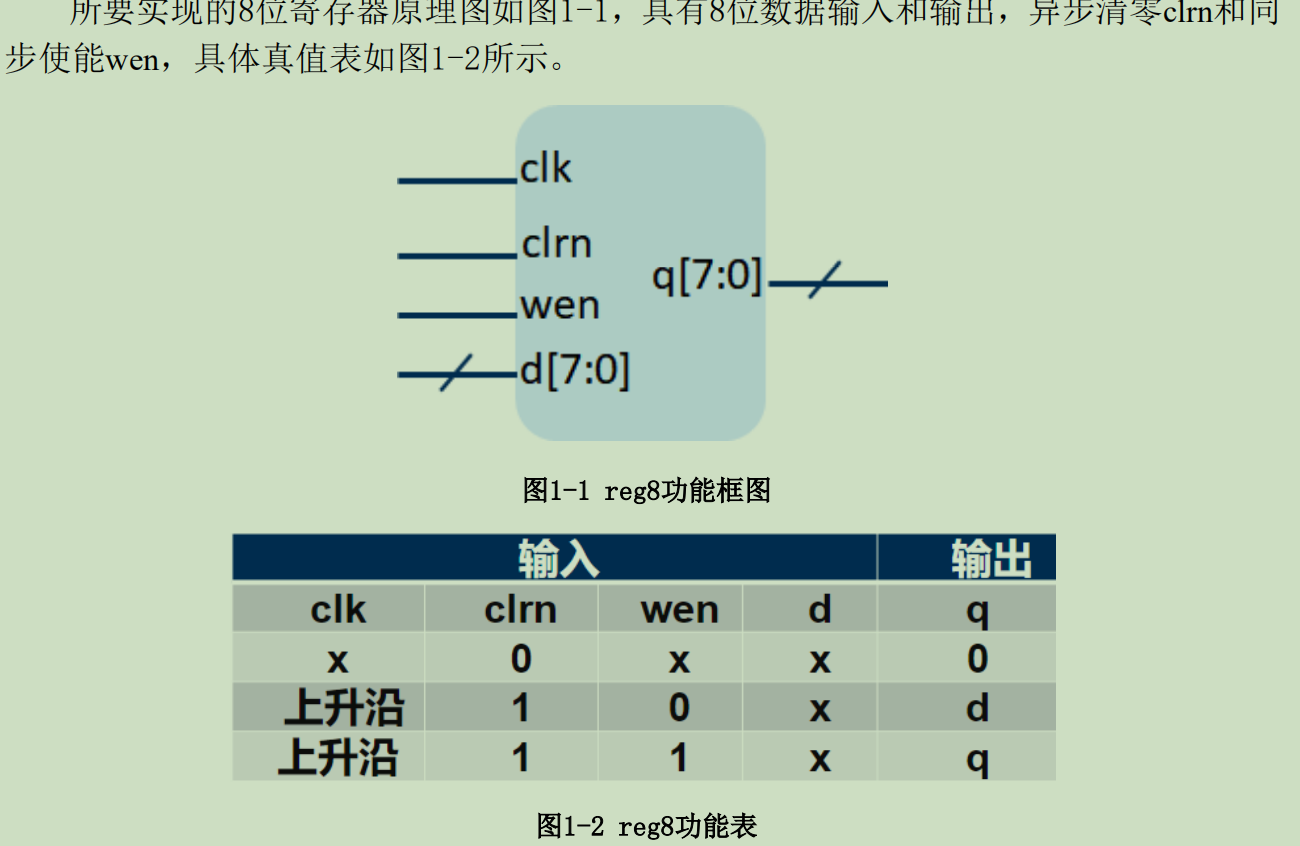

要求:

看到这个题,首先我们应该先考虑D触发器的实现:

`timescale 1ns / 1ps

module dffe(

input clk,

input clrn,wen,

input d,

output reg q

);

always@(posedge clk or negedge clrn) //因为是异步清零,也需要加到always中

begin

if(clrn == 1'b0) //如果是异步清零,直接将q赋值位0

q <= 1'b0;

else if(wen == 1'b0) //同步使能,需要跟随时钟周期

q <= d;

else //保持

q <= q;

end

endmodule

- 首先,这里开始涉及到时序电路,我们需要在always语句块中添加时钟信号的上升沿/下降沿

- 异步清零是不论时钟信号如何,只要是使能端有效(这里是低有效)就需要清零,所以我们必须将信号也加到always语句块中;并且因为always不能边缘触发和电平触发同时存在(也就是有的有posedge或negedge,有的没有),所以我们还需要为使能端加上一个边缘,因为是低有效,所以是下降沿触发。

- 同步使能就需要看时钟信号了,信号不到位,怎么都不行。

因为是八位寄存器,所以我们需要创建8个D触发器来构成一个寄存器,也就是需要调用我们写好的D触发器8次……

模块调用的细节

这样我们就只需要一个顶层模块将整体穿起来,就实现了我们的功能。

module reg8(

input clk,

input clrn,

input[7:0] d,

input wen,

output[7:0] q

);

dffe the_dffe0(clk,clrn,wen,d[0],q[0]);

dffe the_dffe1(clk,clrn,wen,d[1],q[1]);

dffe the_dffe2(clk,clrn,wen,d[2],q[2]);

dffe the_dffe3(clk,clrn,wen,d[3],q[3]);

dffe the_dffe4(clk,clrn,wen,d[4],q[4]);

dffe the_dffe5(clk,clrn,wen,d[5],q[5]);

dffe the_dffe6(clk,clrn,wen,d[6],q[6]);

dffe the_dffe7(clk,clrn,wen,d[7],q[7]);

endmodule

这个例子就属于比较经典的模块调用了,我们也要有对模块的定义,其实每一个模块之间本身是等价且是同时运行的,是需要我们人为规定谁是主模块,谁需要调用其他模块来实现功能的。

最后

以上就是爱笑芹菜最近收集整理的关于使用D触发器完成带有异步清零clrn和同步使能wen的8位寄存器的全部内容,更多相关使用D触发器完成带有异步清零clrn和同步使能wen内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复