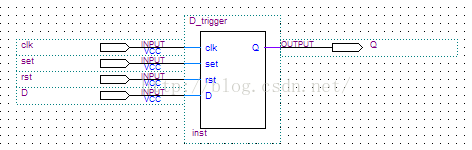

1、Verilog描述具有有异步清0、异步置1的D触发器

//同步复位、置位D触发器模块描述

module D_synctrigger(clk,rst,set,D,Q);

input clk,rst,set,D;

output Q;

reg Q;//寄存器定义

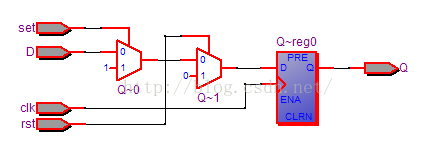

always @(posedge clk)

begin

if(rst) //同步清0,高有效

begin

Q <= 1'b0;

end

else if(set) //同步置1,高有效

begin

Q <= 1'b1;

end

else

begin

Q <= D;

end

end

endmodule

2、Testbench描述

//同步复位、置位D触发器Testbench描述

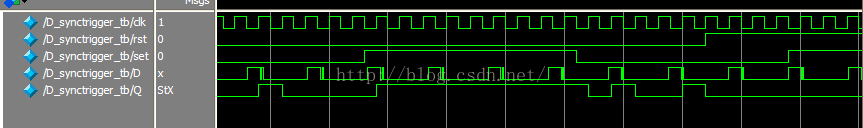

`timescale 1ns/1ns

module D_synctrigger_tb;

reg clk,rst,set,D;

wire Q;

D_synctrigger u1(.clk(clk),.rst(rst),.set(set),.D(D),.Q(Q));

initial

begin

clk = 0;

rst = 0;

set = 0;

forever

begin

#60 D <= 1;

#22 D <= 0;

#2 D <= 1;

#2 D <= 0;

#16 D <= 0;

end

end

always #940 rst <= ~rst;

always #360 set <= ~set;

always #20 clk <= ~clk;

endmodule

最后

以上就是耍酷冰棍最近收集整理的关于带有同步清0、同步置1的D触发器模块描述及其Testbench测试的全部内容,更多相关带有同步清0、同步置1内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复