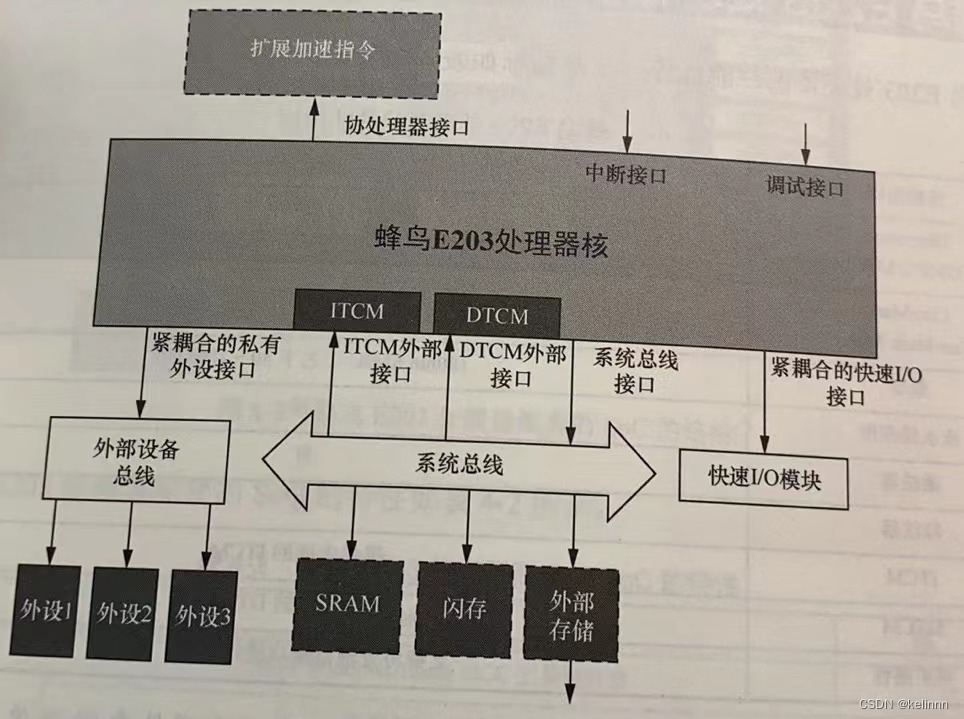

蜂鸟E203总体框架

蜂鸟E203处理器系统如下图所示

一、蜂鸟E203处理器核设计总览和顶层

1.1 蜂鸟E203处理器核的设计理念

- 模块化和可重用性:将处理器分成几个主体模块,每个单元之间的接口简单清晰。

- 面积最小化:追求低功耗和小面积,尽可能地服用数据通路以节省面积开销

- 结构简单化

- 性能不追求极端

1.2 蜂鸟E203处理器核的RTL代码风格

- 使用标准的DFF模块例化、生成寄存器

- 推荐使用Verilog中的assign语法替代if-else 和case语法

1.2.1 使用标准的DFF模块例化生成寄存器

wire flg_r

wire flg_nxt = ~flp_r;

wire flg_ena

sirv_gnrl_dfflr #(1) flg_dfflrs(flg_ena, flg_r, flg_nxt ,clk, rst_n);

实际上sirv_gnrl_dfflr 是一个使用Verilog语法的always块编写的DFF模块。

if else无法捕捉不定态,使用这个DFF模块还可以捕捉不定态,一旦输入是不定态就会退出仿真并且报错。

1.2.2 推荐使用assign 语法替代if else 和case语法

verilog的if else和case语法存在两大缺点:

- 不能传播不定态

- 会产生优先级的选择电路而非并行选择电路,从而不利于优化时序和面积

对于if-else不能传播不定态,以如下代码为例。假设a的值为X(不定态),按照Verilog语法它会将等效于 a==0 ,从而让out等于 in2 ,最终没有将X传播出去。这种情况可能会在仿真阶段掩盖某些致命的bug,造成芯片功能错误。

if (a)

out = in1;

else

out = in2;

使用assign语法的话,则会将X传播出去,从而让out也等于X。

aassign out = a ? in1:in2;

Veriog的case语句同样不会传播不定态,同时if-else和case也会形成优先级选择电路如

if(sel1)

out = in1[3:0];

else if (sel2)

out = in2[3:0];

else if (sel3)

out = in3[3:0];

else

out = in4[3:0];

使用assign的话,假如确实是生成一处有优先级的选择电路则

assign out = sel1 ? in1[3:0]:

sel2 ? in2[3:0]:

sel3 ? in3[3:0]:

in4[3:0];

而如果要生成并行的选择逻辑,则利用assign语法明确地写成"于或"的逻辑

assign out = ({4{sel1}} & in1[3:0])

|({4{sel2}} & in2[3:0])

|({4{sel3}} & in3[3:0])

{ }表示拼接,{第一位,第二位…};

{{ }}表示复制,{4{a}}等同于{a,a,a,a};

&是按位与 |是按位或

1.2.3 注意事项

- 带reset信号的寄存器面积略大,时序稍微差一些,因此在数据通路上可以使用补带reset的寄存器,而只在控制通路商使用带reset信号的寄存器

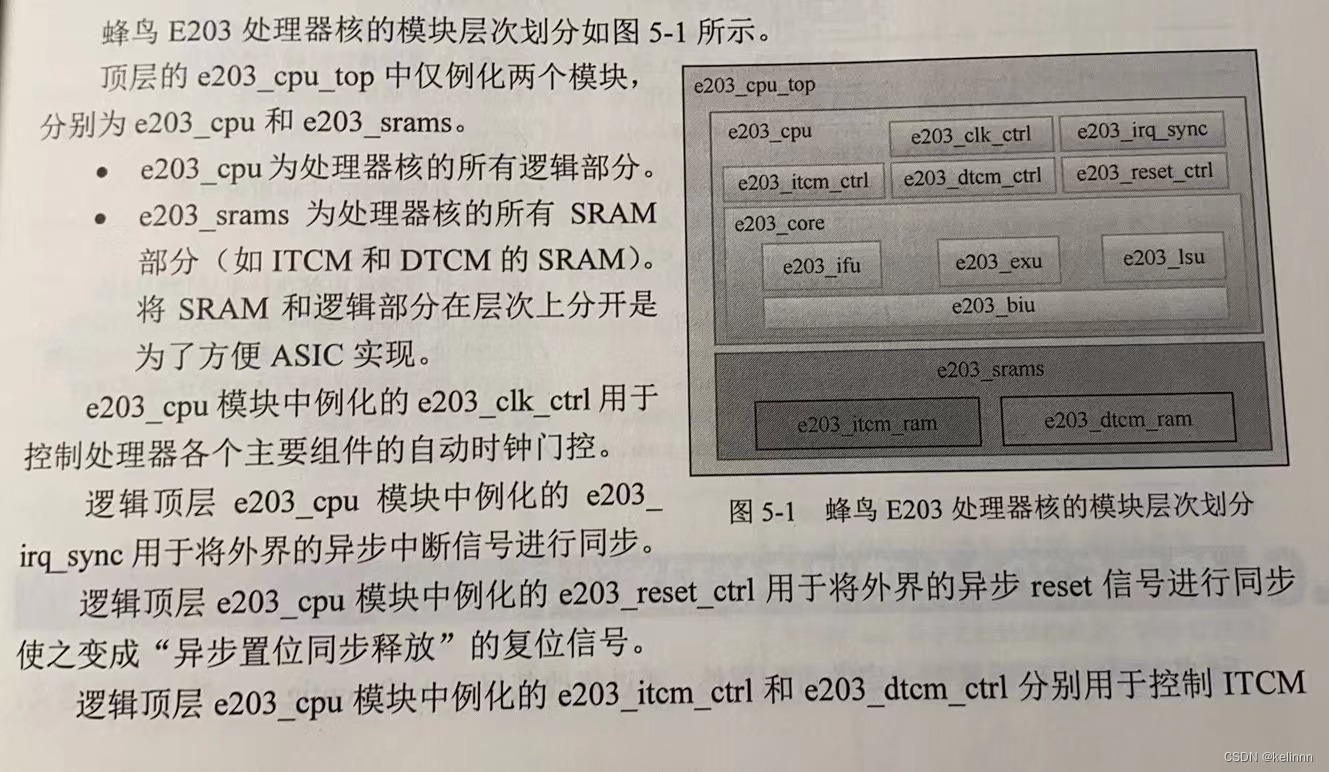

1.3 蜂鸟E203模块层次划分

最后

以上就是娇气楼房最近收集整理的关于蜂鸟E203学习笔记(二)--蜂鸟E203总体框架蜂鸟E203总体框架一、蜂鸟E203处理器核设计总览和顶层的全部内容,更多相关蜂鸟E203学习笔记(二)--蜂鸟E203总体框架蜂鸟E203总体框架一、蜂鸟E203处理器核设计总览和顶层内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复