| 嵌入式工程师成长之路 系列文章 总目录 |

|---|

| 系列文章总目录 |

| 希望本是无所谓有,无所谓无的,这正如脚下的路,其实地上本没有路,走的人多了,也便成了路 |

| 原创不易,文章会持续更新,欢迎微信扫码关注公众号 |

| 项目合作 或 技术培训 联系作者 |

1.简述

组合逻辑电路存在竞争冒险问题,系统不太稳定。时序逻辑电路则可以极大避免这种问题,系统更稳定。

时序逻辑电路的基本单元就是寄存器。寄存器具有存储功能,一般是由 D 触发器构成。D触发器由时钟脉冲控制,每个 D 触发器(D Flip

Flop , DFF)能够存储一位二进制码。

D 触发器功能:在一个脉冲信号/时钟的上升沿或下降沿的作用下,将信号从输入端 D 送到输出端 Q,如果边沿信号一直没有出现,即使输入信号改变,输出信号仍然保持原值。寄存器拥有复位清零功能,其复位又分为同步复位和异步复位。

组合逻辑和时序逻辑电路的区分方法:看数据的传递是不是在同一时钟源下进行的。

2.编写代码

需求:按键按下,led亮;按键谈起,led灭。

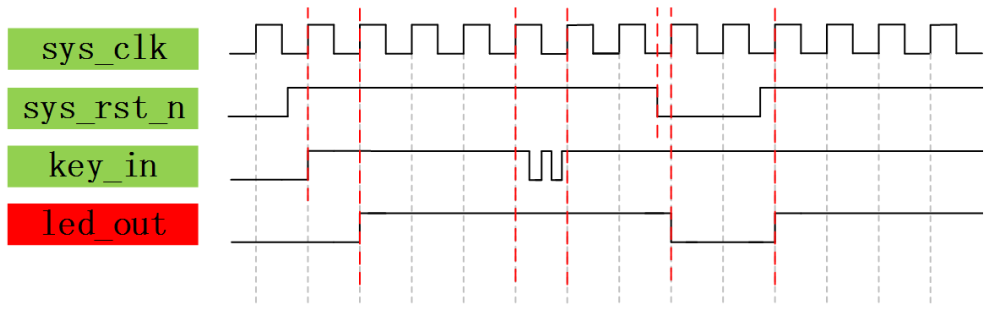

(1)同步复位D触发器

//只有当时钟沿来了,才能执行代码

module flip_flop

(

input wire sys_clk , //系统时钟50Mhz,时序电路一定要有时钟

input wire sys_rst_n , //全局复位,系统出现问题能够回到初始状态或一些信号初始化时需要进行复位

input wire key_in , //输入按键

output reg led_out //输出控制led灯

);

always@(posedge sys_clk) //当sys_clk上升沿时执行下面的语句

if(sys_rst_n == 1'b0) //当sys_clk的上升沿到来时,如果同时检测到sys_rst_n为低电平则复位有效

led_out <= 1'b0; //时序电路赋值符号一定要使用“<=”

else

led_out <= key_in;

endmodule

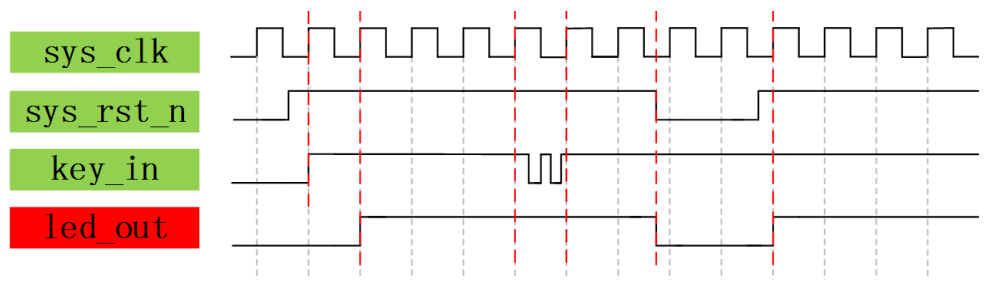

(2)异步复位

module flip_flop

(

input wire sys_clk , //系统时钟50Mhz,时序电路一定要有时钟

input wire sys_rst_n , //全局复位,系统出现问题能够回到初始状态或一些信号初始化时需要进行复位

input wire key_in , //输入按键

output reg led_out //输出控制led灯

);

always@(posedge sys_clk or negedge sys_rst_n) //当sys_clk上升沿或sys_rst_n下降沿时执行下面的语句

if(sys_rst_n == 1'b0) //sys_rst_n为低,并且检测到sys_rst_n下降沿时立刻复位,不需等待sys_clk上升沿到来后再复位

led_out <= 1'b0;

else

led_out <= key_in;

endmodule

最后

以上就是腼腆冬日最近收集整理的关于【专题3:Fpga详解】 之 【1.6.D触发器和寄存器】的全部内容,更多相关【专题3:Fpga详解】内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复