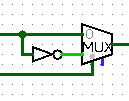

一、不要将信号和它取反的结果作为多路选择器(Multiplexer)的输入

可以用一个异或门代替

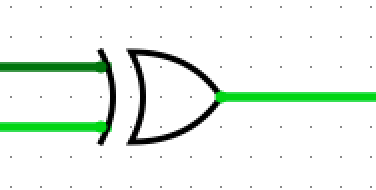

异或门

Logisim中多输入的异或门,运算时是按照顺序进行异或运算,最终得到最后的结果的。

符号相关

Verilog中wire、reg等数据类型默认为无符号数,当希望做符号数相关操作时,可以使用$signed().

应当注意当混合操作有符号数和无符号数时,Verilog会自动进行 数据类型匹配 ,将符号数向无符号类型转换,例如assign resu = a < $signed(b);仍然是看作两个无符号数比较assign resu = $signed(a) < $signed(b);才是有符号数的比较。

对于移位运算符,其右侧的操作数总是被视为无符号数,并且不会对运算结果的符号性产生任何影响。结果的符号由运算符左侧的操作数和表达式的其余部分共同决定。

p.s. 在Verilog中,若将一个变量赋值为负数,则该变量中存储的是该数的补码形式, 但是默认被作为无符号数看待 。

Register

Register中的en引脚使能是对于时钟信号的,当en有效或未定义则时钟信号有效,若en为低电平则忽略时钟信号(同时寄存器内的值保持不变)。

Register的自带复位信号是异步复位

MUX

当输入的选择端口有任何一位是x时,输出各个位都是x。

当Enable端口为0时,When 0, the multiplexer's output consists of all floating bits, regardless of the data and select inputs. 输出都是x,忽略输入数据和选择端口,When not 0, output is the selected input,当不是0(1或x)输出为选择的输出。

可选Disabled output 为 floating / Zero分别对应Enable为0时的输出

DMX

规则与MUX类似

最后

以上就是开朗酸奶最近收集整理的关于Logisim避坑指南的全部内容,更多相关Logisim避坑指南内容请搜索靠谱客的其他文章。

发表评论 取消回复