功能:

a,b输入8位有符号数;x1,x2,x3输出结果,若a>b,输出100;若a<b输出001,a=b输出010。

代码实现:

sign_compare.vhd

-------------------------------------------------------

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

use IEEE.STD_LOGIC_arith.ALL;

entity sign_compare is

GENERIC (N:INTEGER:=7);

PORT(a,b: IN SIGNED(n downto 0);

x1,x2,x3: OUT STD_LOGIC);

end sign_compare;

---------------------------------------------

architecture Behavioral of sign_compare is

begin

x1 <= '1' when a>b else '0';

x2 <= '1' when a=b else '0';

x3 <= '1' when a<b else '0';

end Behavioral;

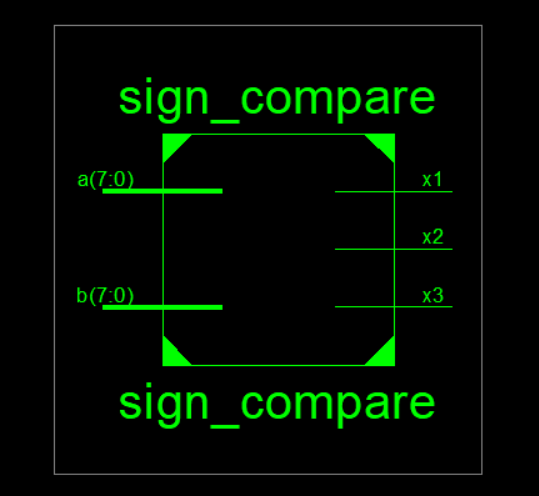

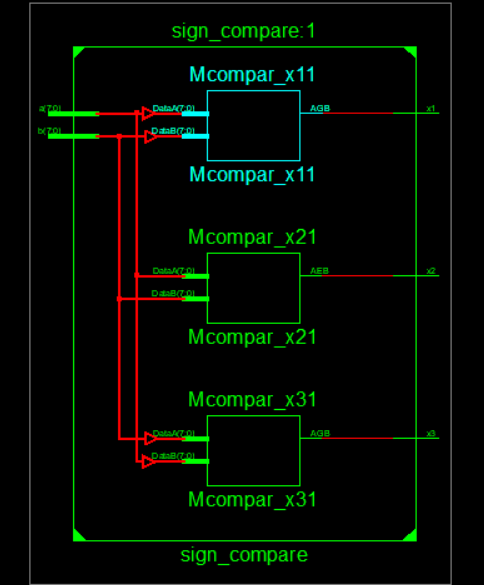

生成原理图:

testbench:

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

use IEEE.STD_LOGIC_arith.ALL;

ENTITY tb_sign IS

END tb_sign;

ARCHITECTURE behavior OF tb_sign IS

COMPONENT sign_compare

PORT(

a : IN SIGNED(7 downto 0);

b : IN SIGNED(7 downto 0);

x1 : OUT std_logic;

x2 : OUT std_logic;

x3 : OUT std_logic

);

END COMPONENT;

--Inputs

--signal a : SIGNED(7 downto 0) := (others => '0');

--signal b : SIGNED(7 downto 0) := (others => '0');

signal a : SIGNED(7 downto 0) := "01111111";

signal b : SIGNED(7 downto 0) := "11111110";

--Outputs

signal x1 : std_logic;

signal x2 : std_logic;

signal x3 : std_logic;

signal clk,rst : std_logic;

constant clk_period : time := 10 ns;

BEGIN

uut: sign_compare PORT MAP (

a => a,

b => b,

x1 => x1,

x2 => x2,

x3 => x3

);

clk_process :process

begin

clk <= '0';

wait for clk_period/2;

clk <= '1';

wait for clk_period/2;

end process;

stim_proc: process

begin

rst<='0';

wait for 10 ns;

rst<='1';

wait;

end process;

END;

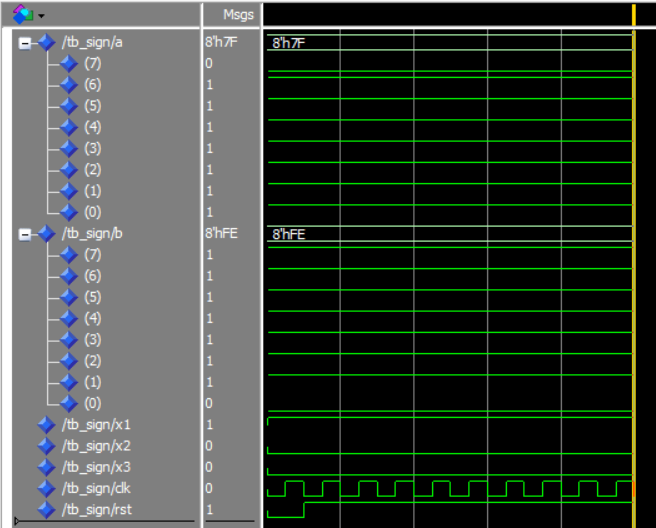

modelsim仿真波形如下:

最后

以上就是动听人生最近收集整理的关于VHDL有符号比较器的全部内容,更多相关VHDL有符号比较器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复