使用计数器实现n分频

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity div is

port(n: in std_logic_vector(7 downto 0);

clk: in std_logic;

clkout: out std_logic);

end div;

architecture rtl of divvv is

signal cnt: std_logic_vector(7 downto 0);

signal n_t,n_1: std_logic_vector(7 downto 0);

begin

n_1 <= n - 1;

n_t <= '0' & n(7 downto 1);

process(n, clk)

begin

if clk'event and clk = '1' then

if cnt = n_1 then

cnt <= "00000000" ;

else

cnt <= cnt + 1;

end if;

if cnt < n_t then

clkout <= '0';

else

clkout <= '1';

end if;

end if;

end process;

end rtl;

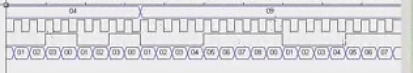

实现3.5分频

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY expp IS

PORT( clk: IN STD_LOGIC;

pout: out std_logic;

cont,cont1: buffer std_logic);

end expp;

architecture bhv of expp is

signal count: std_logic_vector(3 downto 0);

signal count1: std_logic_vector(3 downto 0);

begin

process(clk)

begin

if clk'event and clk = '1' then

if count1 < 4 then

count1 <= count + 1; cont <= '0';

else

count1 <= "0000"; cont <= '1';

end if;

end if;

end process;

process(clk)

begin

if clk'event and clk = '0' then

if count < 4 then

count <= count1 + 1; cont1 <= '0';

else

count <= "0000"; cont1 <= '1';

end if;

end if;

end process;

pout <= cont and cont1;

end bhv;

完成一个9分频器,分频后的输出信号,其频率为输入信号的1/9,且输出信号占空比为1/2。

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY exp4 IS

PORT( clk: IN STD_LOGIC;

pout: out std_logic);

end exp4;

architecture bhv of exp4 is

signal count: std_logic_vector(3 downto 0);

signal count1: std_logic_vector(3 downto 0);

signal cont,cont1: std_logic;

begin

process(clk)

begin

if clk'event and clk = '1' then

if count < 8 then

count <= count + 1;

else

count <= "0000";

end if;

if count < 5 then

cont1 <= '0';

else

cont1 <= '1';

end if;

end if;

if clk'event and clk = '0' then

if count1 < 8 then

count1 <= count1 + 1;

else

count1 <= "0000";

end if;

if count1 < 5 then

cont <= '0';

else

cont <= '1';

end if;

end if;

pout <= cont or cont1;

end process;

end bhv;

最后

以上就是务实苗条最近收集整理的关于VHDL分频的全部内容,更多相关VHDL分频内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复