--移位相加型乘法器的VHDL表述

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

USE IEEE.STD_LOGIC_ARITH.ALL;

ENTITY MULT4B is

GENERIC (S: INTEGER := 4); --使用GENERIC语句,将常量S定义为整数4

PORT(

R : OUT STD_LOGIC_VECTOR(2*S DOWNTO 1); --8位的R作最终输出

A, B: IN STD_LOGIC_VECTOR(S DOWNTO 1)); --4位的A、B作为输入

END ENTITY MULT4B;

ARCHITECTURE ONE of MULT4B is

SIGNAL A0: STD_LOGIC_VECTOR(2*S DOWNTO 1); --8位的信号A0

begin

A0 <= CONV_STD_LOGIC_VECTOR(0,S) & A ; --通过转换函数生成4位的0000与A拼成8位数据

PROCESS(A,B,A0) --进程敏感信号A,B,A0

VARIABLE R1 : STD_LOGIC_VECTOR(2*S DOWNTO 1); --8位的中间变量R1

BEGIN

R1 := (others => '0'); --R1初始化为零

FOR i IN 1 TO S LOOP --4位二进制数A,B乘法循环判断4次,i=1:4

IF(B(i) ='1') then --若检测到B的某一位为1,说明乘法有效(见二进制乘法原理)

R1 := R1 + TO_STDLOGICVECTOR(TO_BITVECTOR(A0) SLL(i-1)); --移位相加

END IF;

END LOOP;

R <= R1; --返回输出值R

END PROCESS;

END ARCHITECTURE ONE;

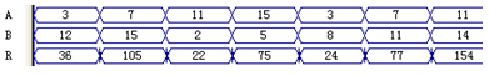

效果:

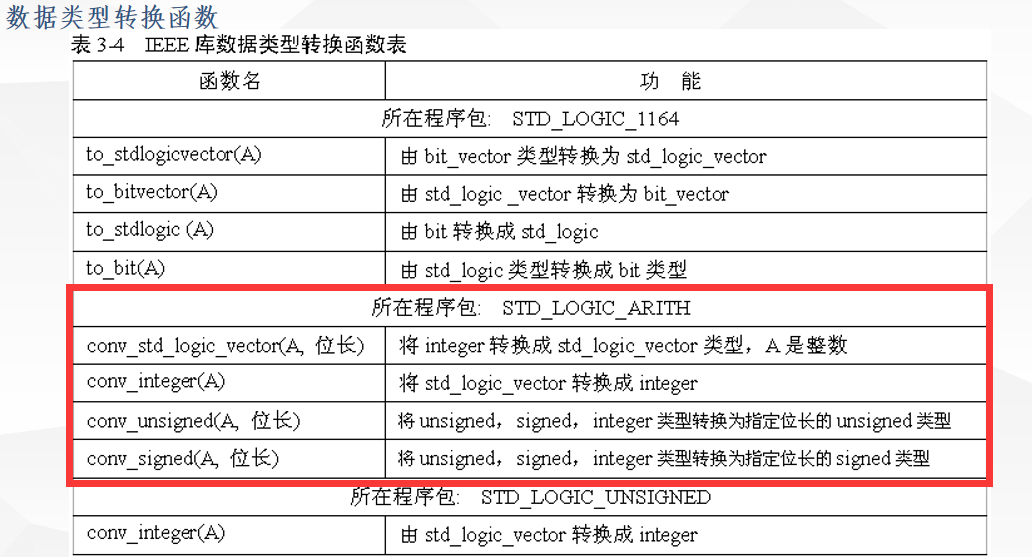

问题1. CONV_STD_LOGIC_VECTOR()函数

该函数位于IEEE.STD_LOGIC_ARITH程序包中:

std_logic_arith程序包里定义的数据转换函数:

conv_std_logic_vector(A,位长)–INTEGER,SINGER,UNSIGNED转换std_logic_vector。

该函数的转换结果是将被转换的数据先转换成2进制补码形式,然后取其低“位长”,作为输出。

如:

a<=conv_std_logic_vector(100,6)-----100的二进制取低6位

二进制100 = 01100100

输出结果:a = 100100

问题2. 二进制移位相加问题

二进制A=0011 ---A=3

左移1位A=0110 ---A=6

左移2为A=1100 ---A=12

左移1位相当于乘2,

左移n位相当于乘

2

n

2^n

2n.

二进制A=0011 ---A=3

左移1位A1=0110 ---A1=6

左移2为B=1100 ---B=12

二进制加法:带进位相加,

A1+B=0110+1100=10010 --即二进制的18

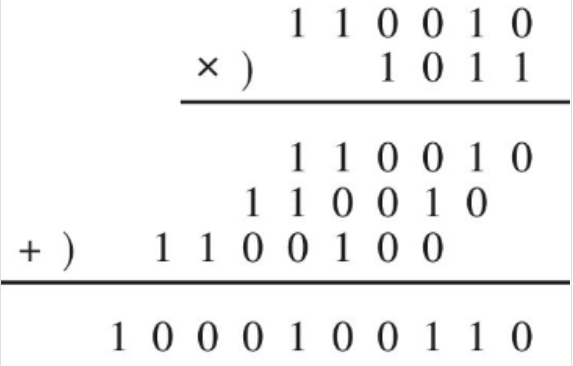

问题3. 移位相加即二进制乘法原理

A=110010

B=1011

当检测到B的某一位为1时,A乘B有效(为0时无效,因为0乘任何数都为0),记录下当前乘积的值,继续移位判断到B的下一位为1时,将上一次的乘积值与当前乘积值累加,即实现了循环移位的乘法原理。

VHDL进程实现:

PROCESS(A,B,A0) --进程敏感信号A,B,A0

VARIABLE R1 : STD_LOGIC_VECTOR(2*S DOWNTO 1); --8位的中间变量R1

BEGIN

R1 := (others => '0'); --R1初始化为零

FOR i IN 1 TO S LOOP --4位二进制数A,B乘法循环判断4次,i=1:4

IF(B(i) ='1') then --若检测到B的某一位为1,说明乘法有效(见二进制乘法原理)

R1 := R1 + TO_STDLOGICVECTOR(TO_BITVECTOR(A0) SLL(i-1)); --移位相加

END IF;

END LOOP;

R <= R1; --返回输出值R

END PROCESS;

最后

以上就是过时盼望最近收集整理的关于VHDL程序设计——移位相加型乘法器的全部内容,更多相关VHDL程序设计——移位相加型乘法器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复