**记录学习,记录成长

1.VHDL中元件的例化可分为两部分

第一部分:元件声明,声明要例化的元件。

第二部分:元件例化,声明结束之后就可以对元件进行例化或者说是调用了。

其中声明部分在结构体的说明语句部分(即architecture和begin之间)。而调用部分同一个结构体的电路描述部分(即begin之后)。

2.元件声明格式:

Component 元件名称 is

Port(元件端口信息);

End component;

提示:元件声明和实体声明一致,元件就是一个实体。

3.元件例化语句

例化名 :元件名称 port map 元件端口列表;

提示:port map为端口映射的意思。相互连接的两个端口,状态和数据类型必须一致。

端口连接方式有两种:一种是位置关联方式。一种是端口信号名称关联方式。

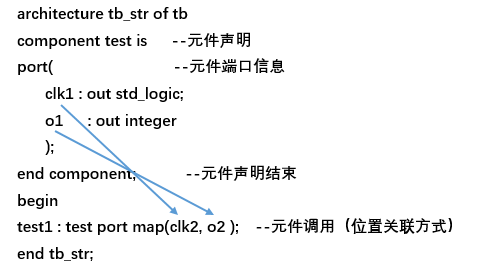

3.1 位置关联方式

位置关联方式下,端口的连接与端口列表中的顺序是一一对应的。

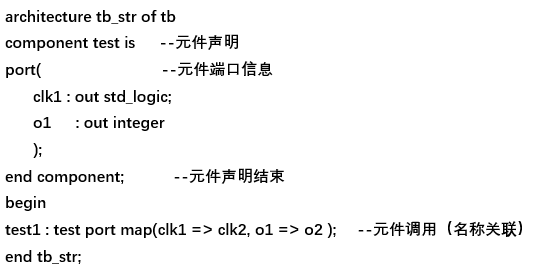

3.2 端口信号名称关联方式

端口信号名称关联方式比较直观,一般推荐使用此种关联方式。

此外,通过查找发现还有事先不进行声明也可进行例化的方式:

例化格式:

例化名 : entity work . 元件名(端口列表)

(https://blog.csdn.net/wyf100/article/details/8616491)

test1 :entity work.test port map(clk2, o2 );

#学习代码1

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity test is

port(

clk1 : out std_logic := '0';

o1 : out integer := 2

);

end test;

architecture teststr of test is

begin

process

begin

wait for 10 ns;

clk1 <= '1';

wait for 10 ns;

clk1 <= '0';

end process;

end teststr;

#学习代码2

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity tb is

port(

clk2 : out std_logic;

o2 : out integer

);

end tb;

architecture tb_str of tb is

component test is

port(

clk1 : out std_logic;

o1 : out integer

);

end component;

begin

test1 : test port map(clk2, o2 );

end tb_str;

#学习代码3

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all;

use ieee.std_logic_unsigned.all;

entity tb is

port(

clk2 : out std_logic;

o2 : out integer

);

end tb;

architecture tb_str of tb is

begin

test1 :entity work.test port map(clk2, o2 );

end tb_str;

最后

以上就是斯文大地最近收集整理的关于VHDL中元件(模块)的例化的全部内容,更多相关VHDL中元件(模块)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复