VHDL组合逻辑-时序逻辑练习

- 一、在QuartusII 中用原理图输入法设计 4 位加法器

- (一)新建项目

- (二)创建原理图

- (三)仿真

- (四)硬件下载测试

- 1.引脚绑定

- 2.硬件测试

- 二、应用QuartusII 完成基本组合电路设计

- (一)二选一多路选择器mux21a

- 1.Verilog语言

- 2.VHDL语言

- 3.硬件仿真

- (二)双二选一多路选择器muxk

- 1.Verilog语言

- 2.VHDL语言

- 3.硬件仿真

- 三、QuartusII 完成基本时序电路的设计

- (一)设计触发器

- 1.新建项目

- 2.创建VHDL文件

- 3.编译仿真

- 4.硬件仿真

- (二)设计锁存器

- 1.新建项目

- 2.创建VHDL文件

- 3.编译仿真

- 4.硬件仿真

- 四、总结

- 五、参考资料

一、在QuartusII 中用原理图输入法设计 4 位加法器

(一)新建项目

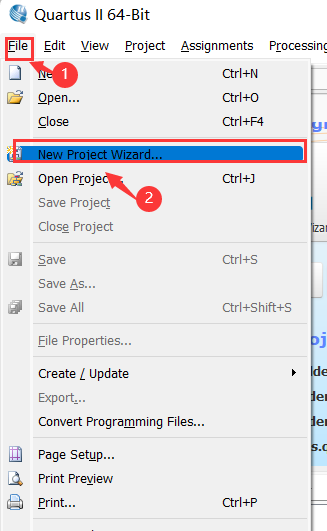

1.File->New Project Wizard

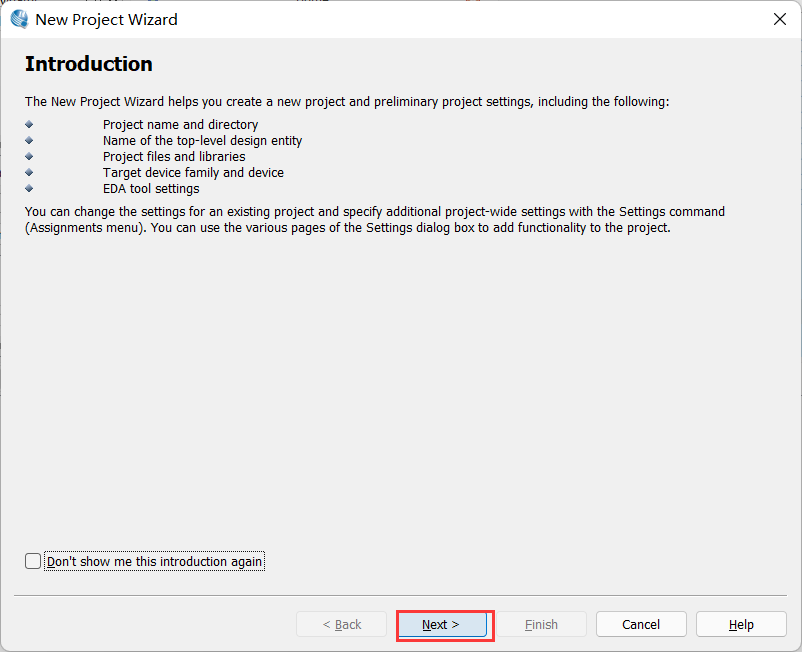

2.点击Next

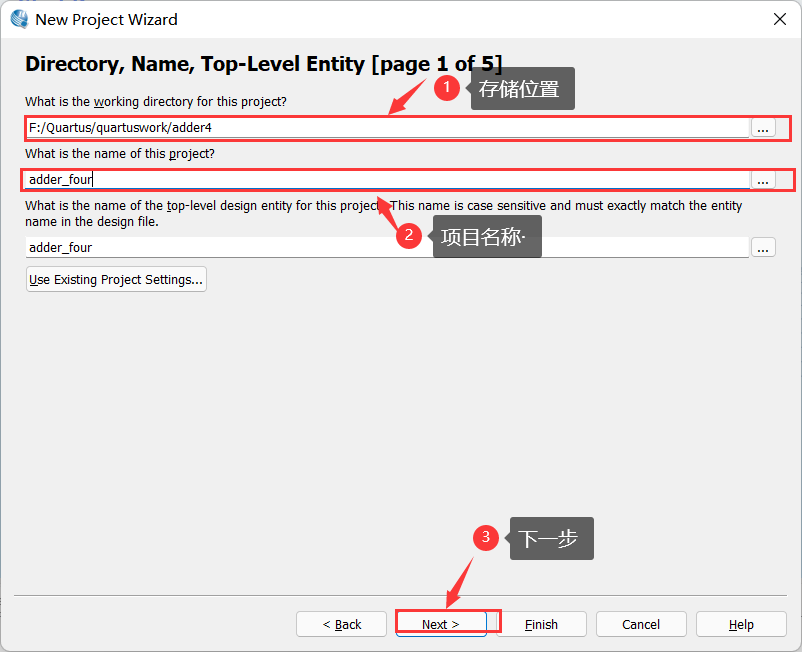

3.设置工程的存储位置和项目名称

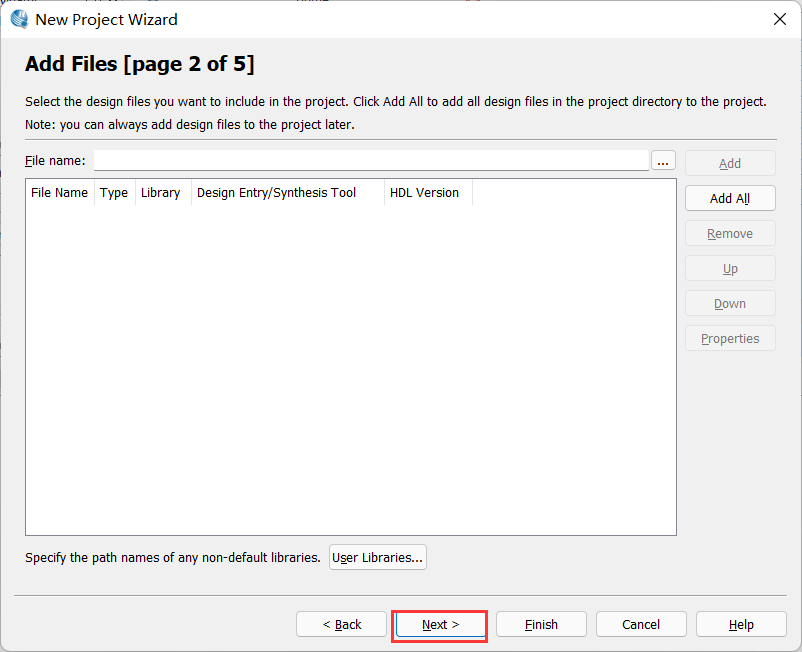

4.选择Next

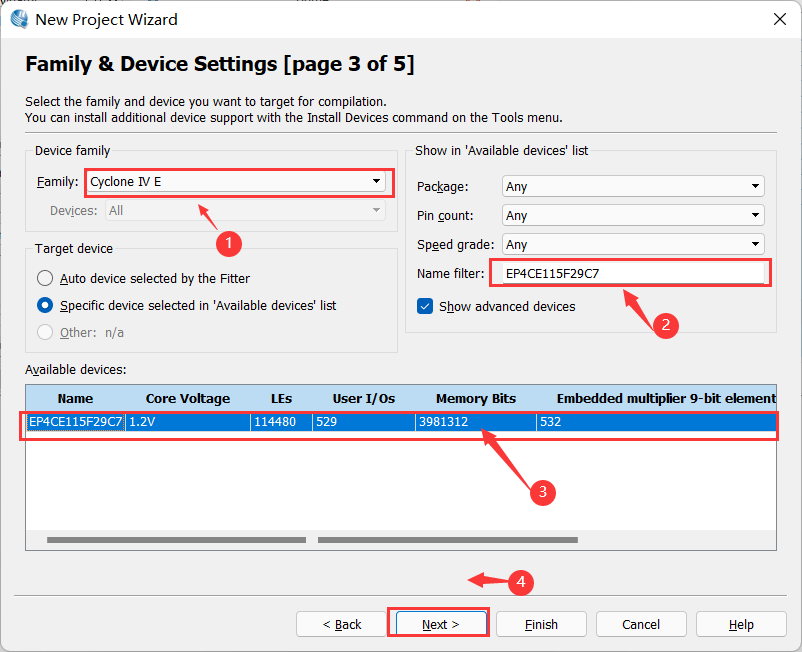

5.选择目标芯片:cyclone IV E系列的EP4CE115F29C7

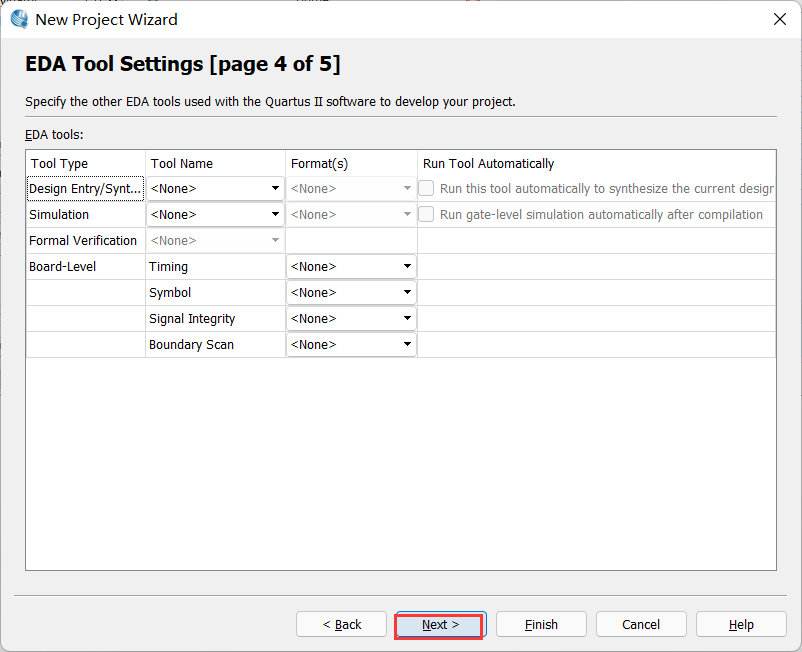

6.EDA Tool Setting设置,直接Next

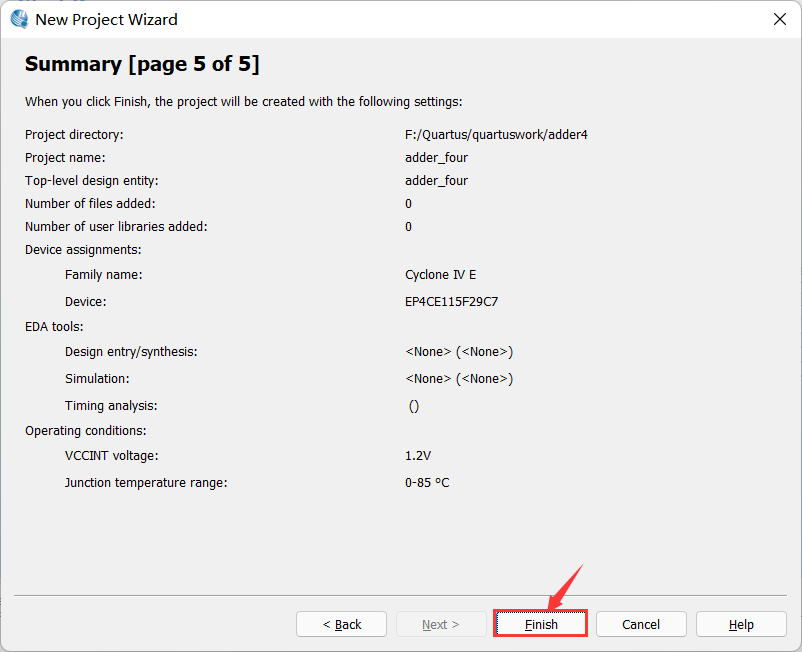

7.点击finish

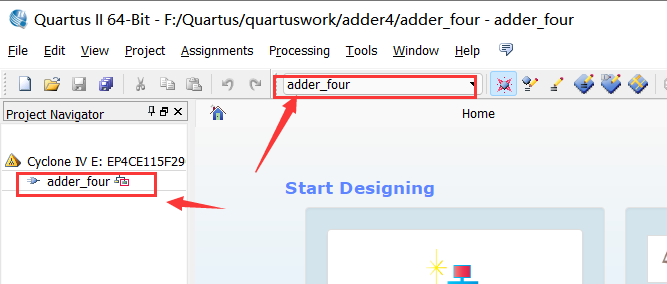

之后界面上会出现顶层文件名和项目名:

(二)创建原理图

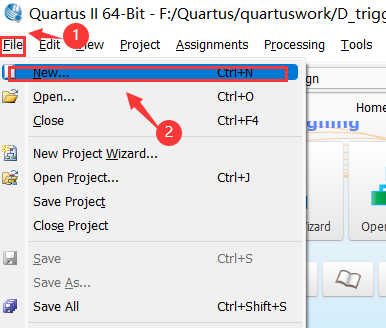

1file->new

2.Design Files->Block Diagram/Schematic File ->OK

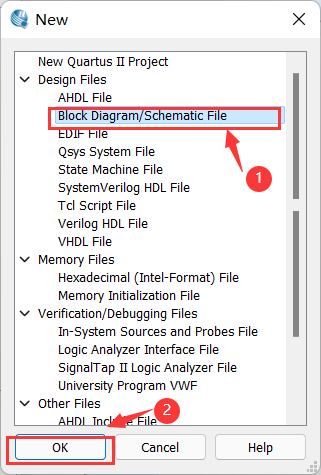

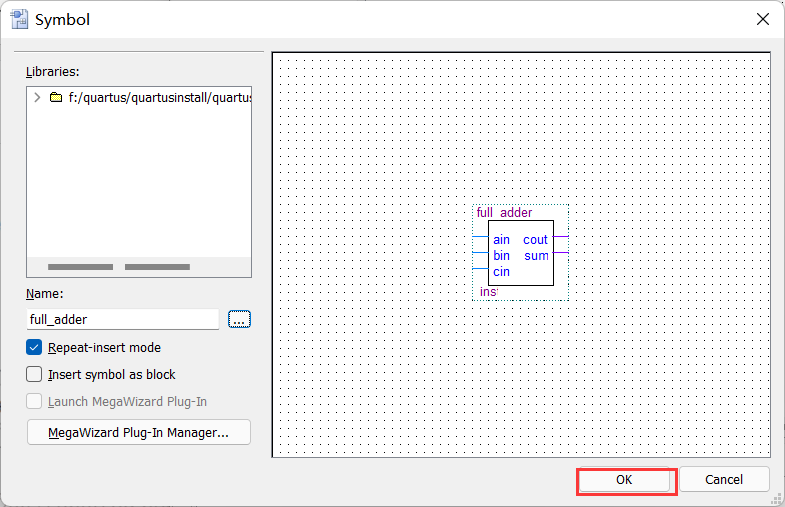

3.点击按纽 Symbol Tool或直接双击原理图空白处

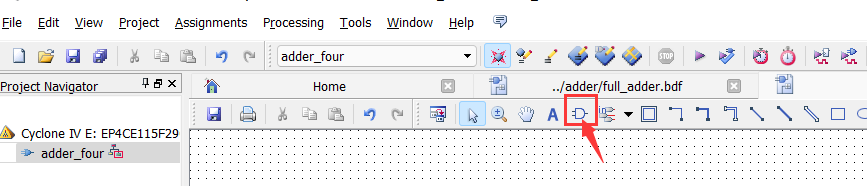

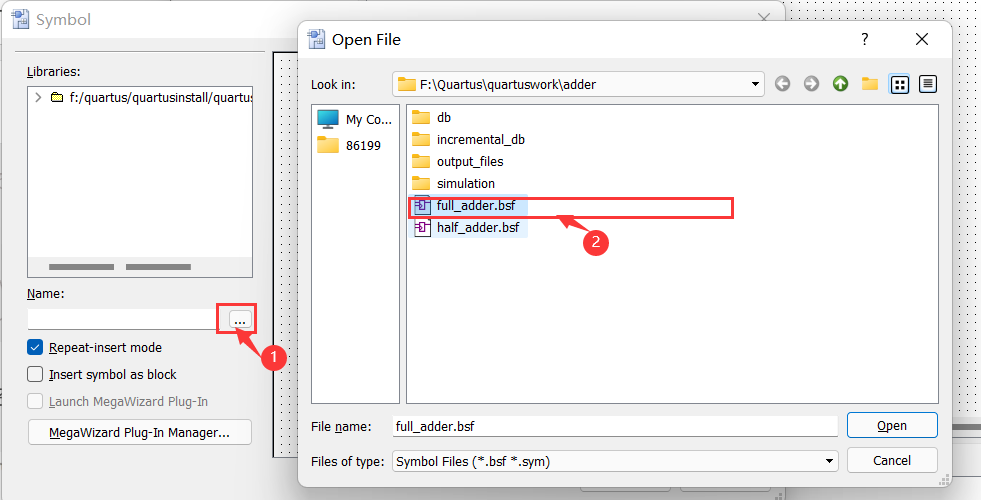

4.从Symbol窗中选择需要的符号,或者直接在name文本框中选择上次实验生成的一位全加器(.bsf文件)元件

注意:这里添加半加器和1位全加器的源文件到当前目录下,否则会报错

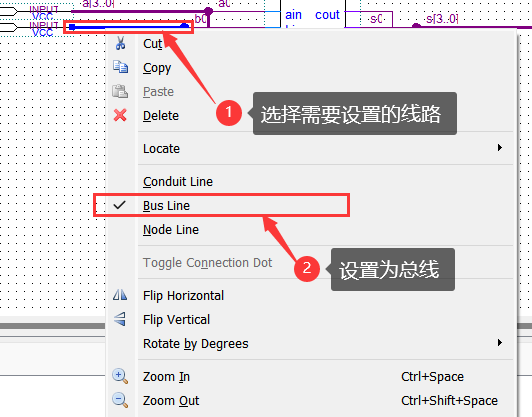

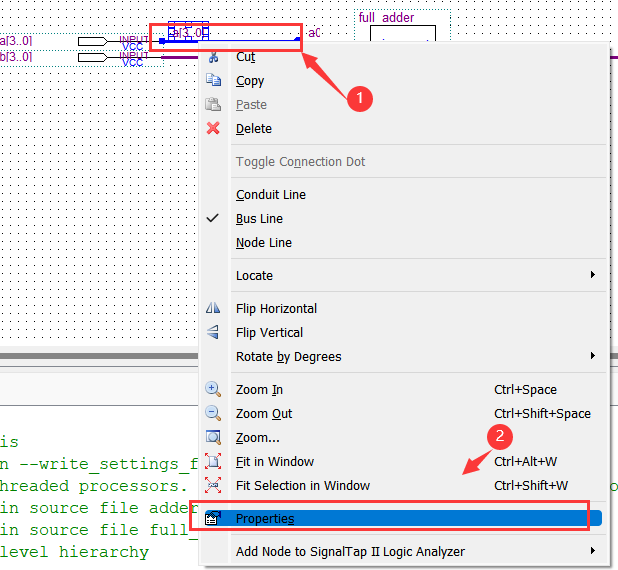

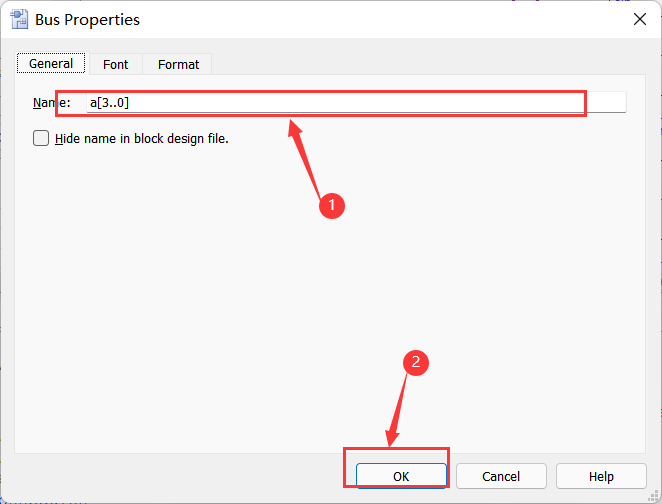

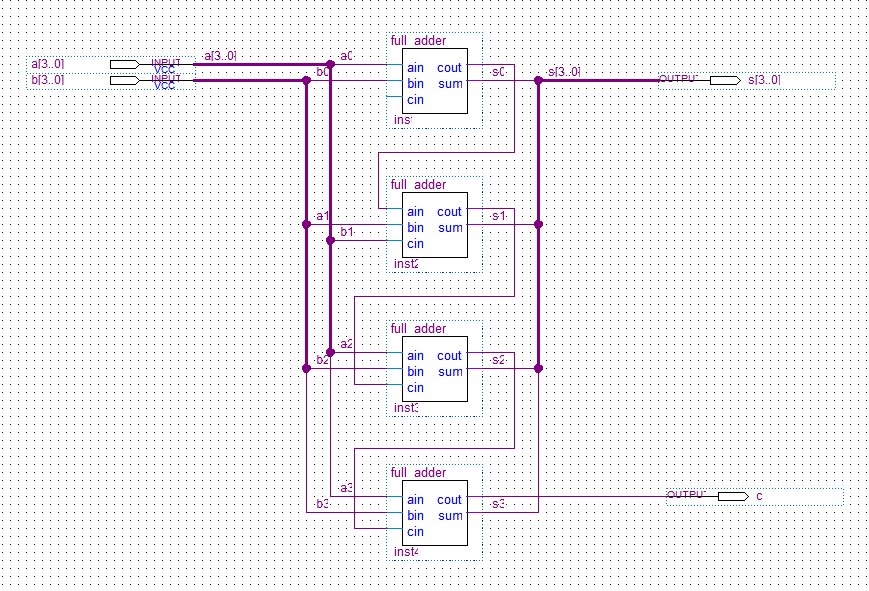

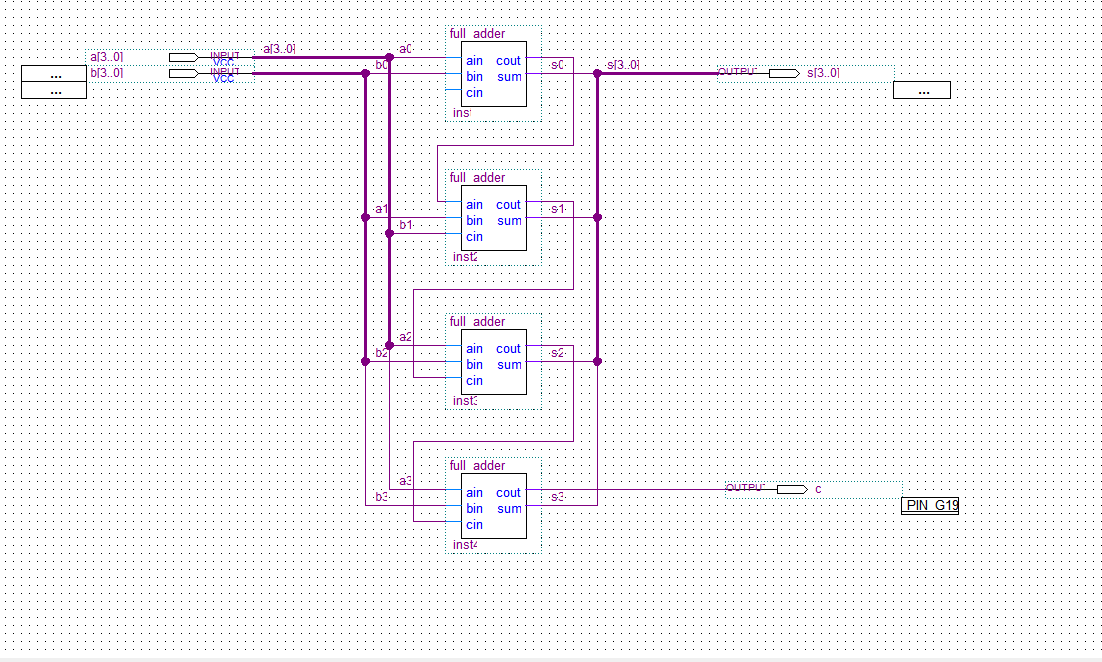

5.分别调入元件full_adder和输入输出引脚input和output。并如图用点击拖动的方法连接好电路。输入各引脚名:a[3…0]、b[3…0], c和s[3…0],并设置总线和命名线路。

(1)设置总线

(2)命名,点击需要命名的线,Properties

(3)最终原理图

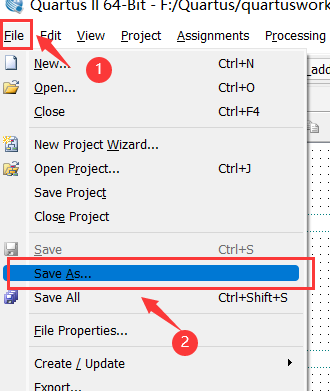

6.保存文件,选择菜单File - Save As,选择刚才为自己的工程建立的目录…adder下,将已设计好的原理图文件取名为:half_adder.bdf(注意默认的后缀是.bdf),并存盘在此文件夹内

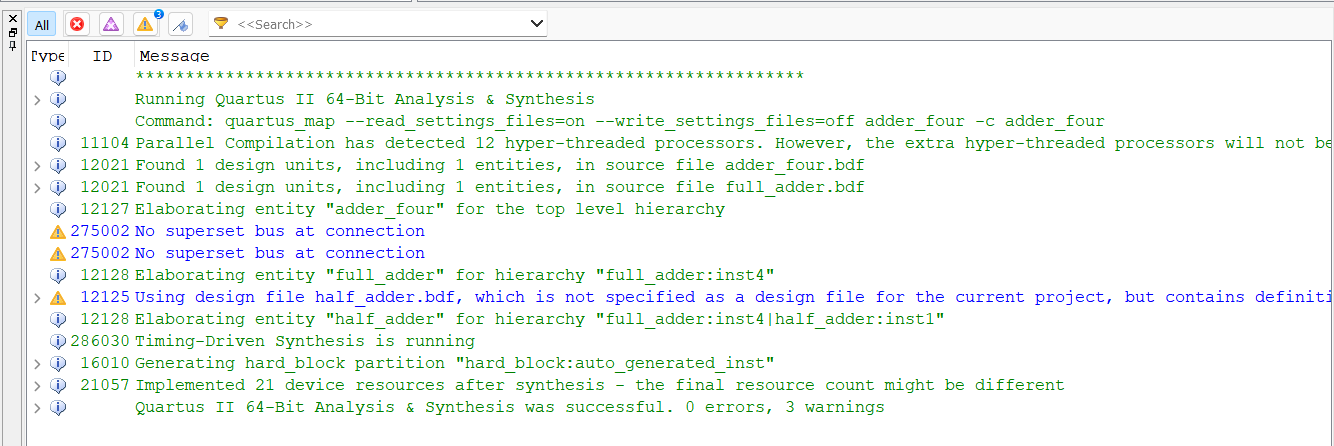

7.编译,点击图标进行编译,若无错误则可进行下一步,若有错进行原理图修改

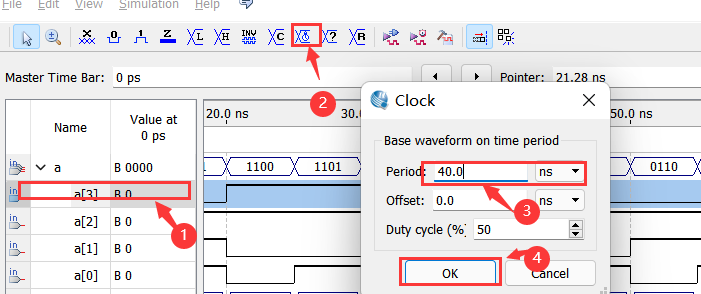

(三)仿真

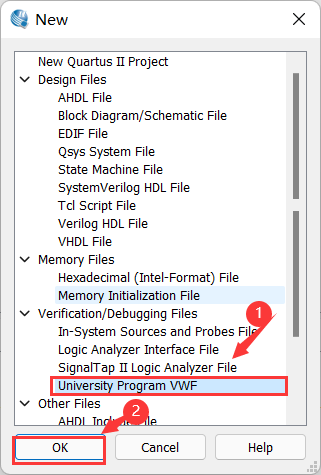

1.新建波形文件file→new→university program VWF,选择后点击OK

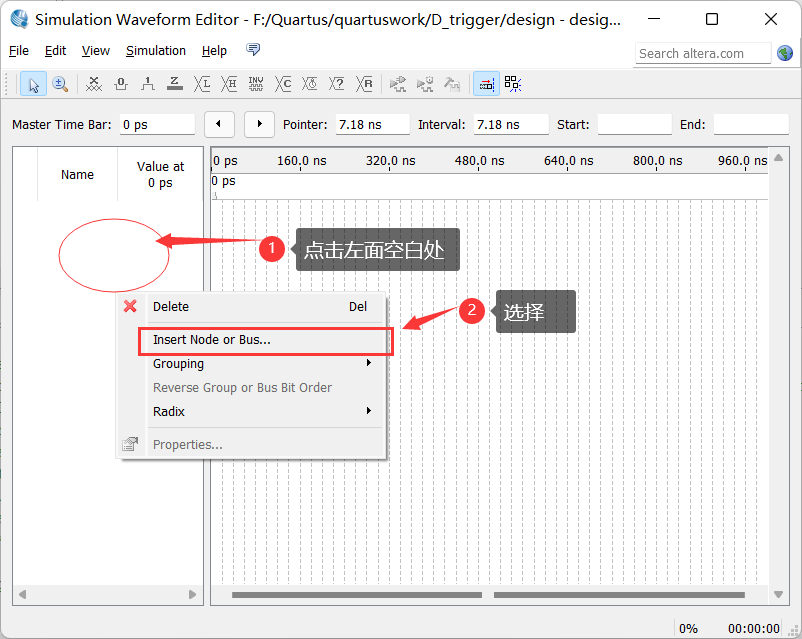

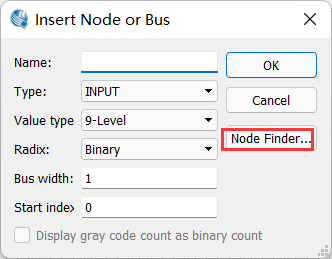

2.点击空白处,选择insert node or bus→node finder

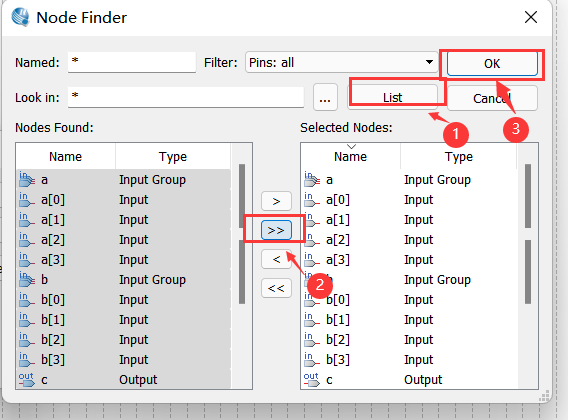

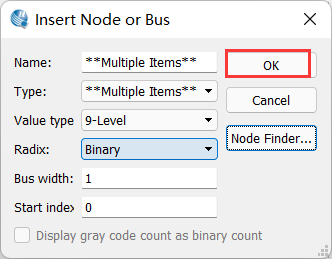

3.点击List,左面出现则触发器中所有的输入输出引脚。再在该界面上点击>>,则把左边所有的端口都选择到右边,点击两次OK,进入波形,

4.设置波形后保存

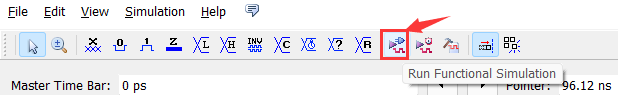

5.点击仿真编译按钮

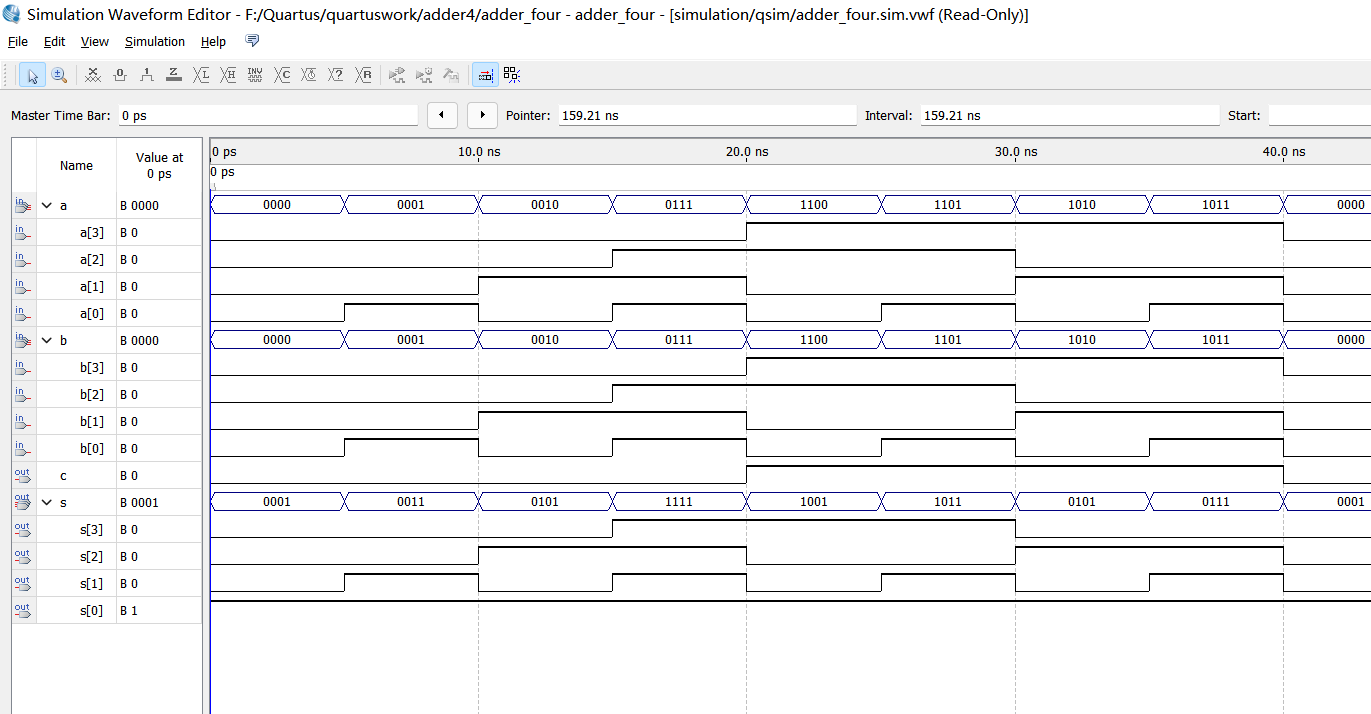

最终结果如图

输入输出满足表达式

S=A+B+CI,C1=‘1’(‘0001’)

S>15时进位C为‘1’

| a[3…0] | b[3…0] | c | s[3…0] |

|---|---|---|---|

| 0000 | 0000 | 0 | 0001 |

| 0001 | 0001 | 0 | 0011 |

| 0010 | 0010 | 0 | 0101 |

| 0111 | 0111 | 0 | 1111 |

| 1100 | 1100 | 1 | 1001 |

| 1101 | 1101 | 1 | 1011 |

| 1010 | 1010 | 1 | 0101 |

| 1011 | 1011 | 1 | 0111 |

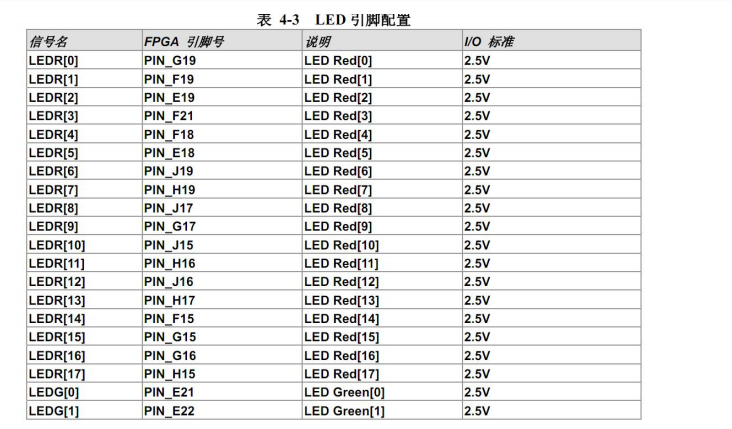

(四)硬件下载测试

1.引脚绑定

(1)硬件设计好后,还需要查引脚图(引脚图见附录)进行引脚绑定。

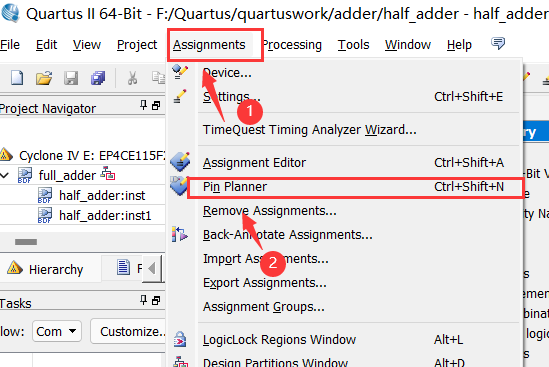

(2)从菜单中选择assignments→pin planner

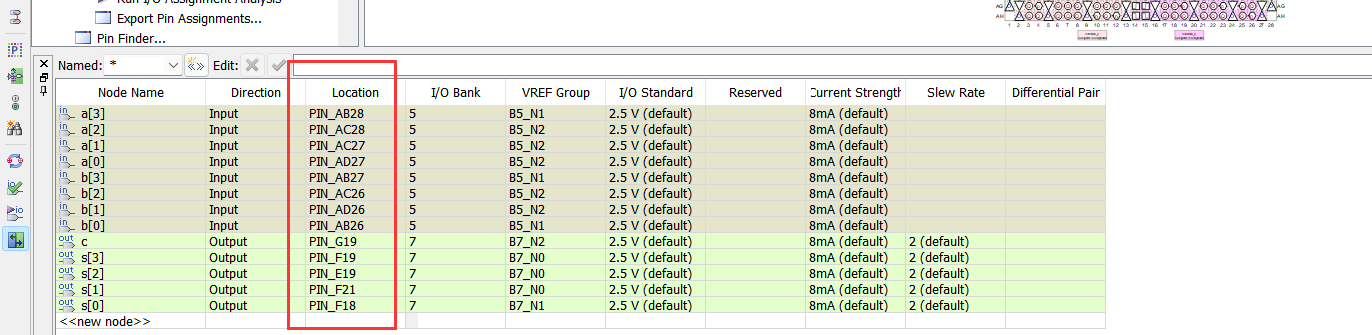

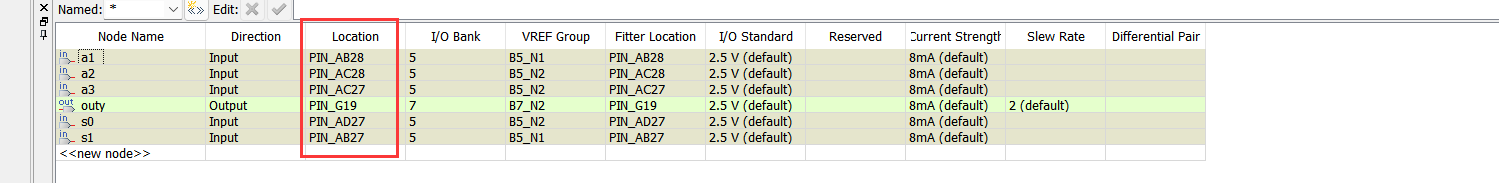

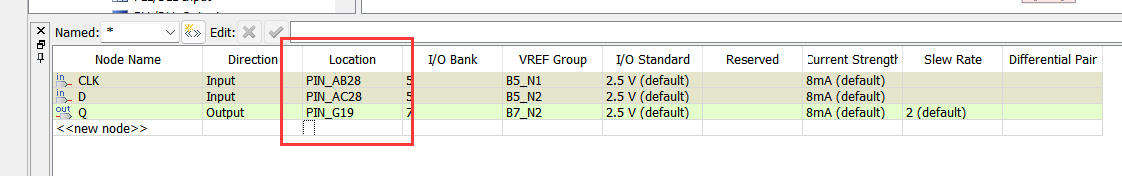

(3)调出引脚绑定窗口,然后从下拉窗口中选择相应的输入输出端口,再在location栏填入对应的 FPGA 引脚即可,如图

(4)选定了引脚之后原理图文件一定要再编译一次,才能真正把引脚绑定上。引脚绑定好并编译过的文件如图:

2.硬件测试

(1)下载到硬件

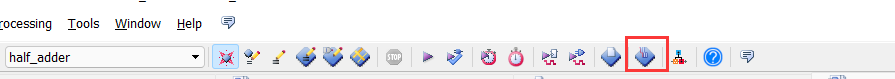

把开发板接上电源,USB 接口接电脑。打开电源开关(注意不用下载时请一定关闭开关,以免烧坏板子)。点击软件工具栏上的按钮

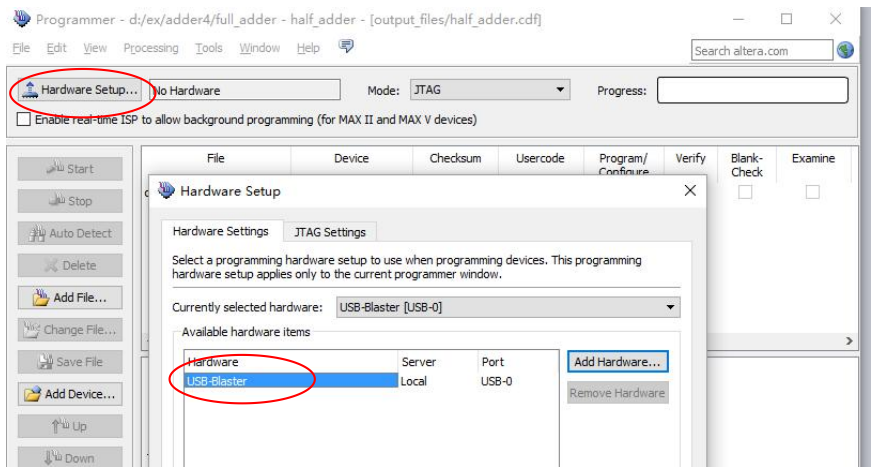

(2)则出现下载界面。第一次下载需安装硬件。即在下载界面中点击按钮“hardware setup…”,然后在弹出的对话框中选择“USB blaster”,再点击“ok”,则硬件被安装上

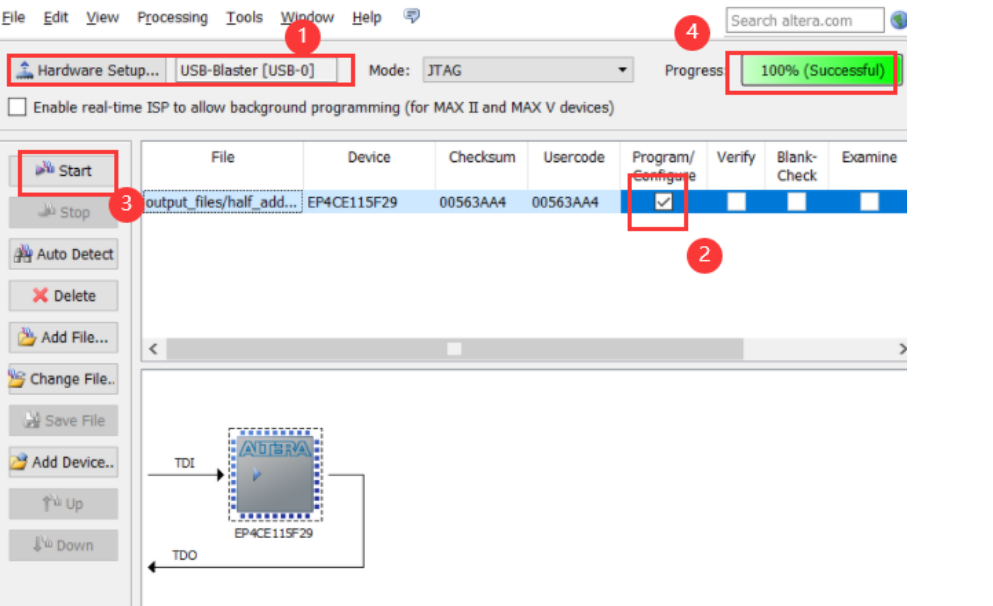

(3)安装好硬件的界面如图。然后在下载的.sof 文件后面的复选框中打勾,再点击”start”,

当进度条达到 100%时,即下载成功,可以进行硬件观测

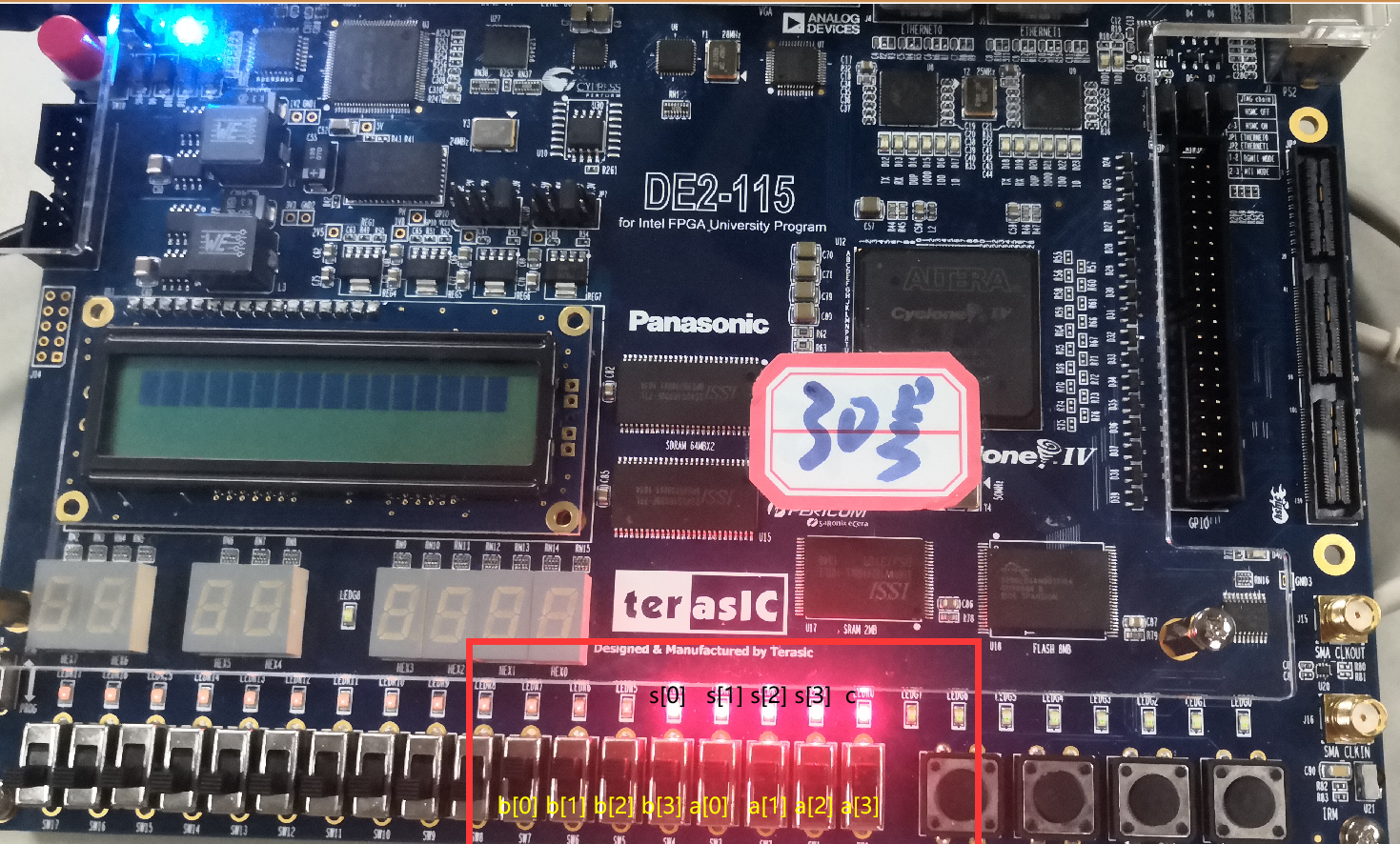

4.硬件观测图

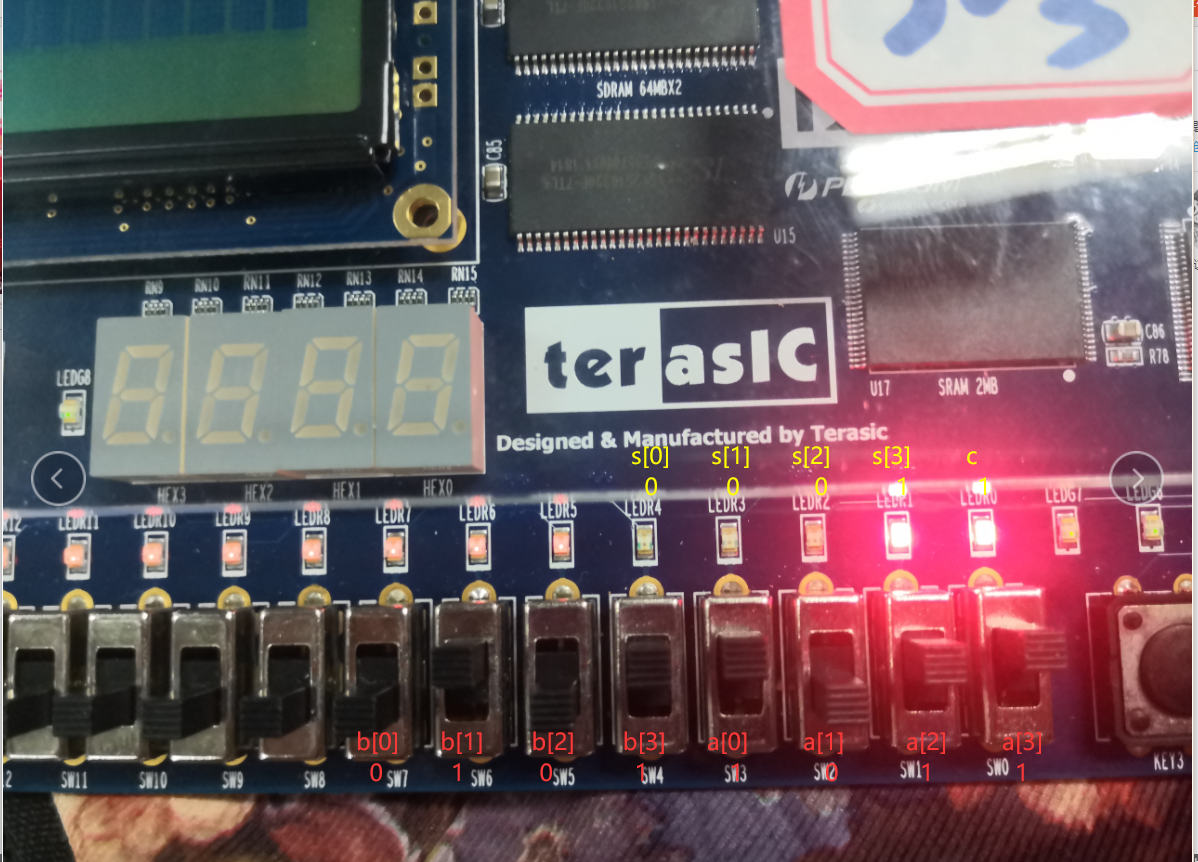

(1)观察图一

| a[3…0] | b[3…0] | c | s[3…0] |

|---|---|---|---|

| 1001 | 0010 | 0 | 1100 |

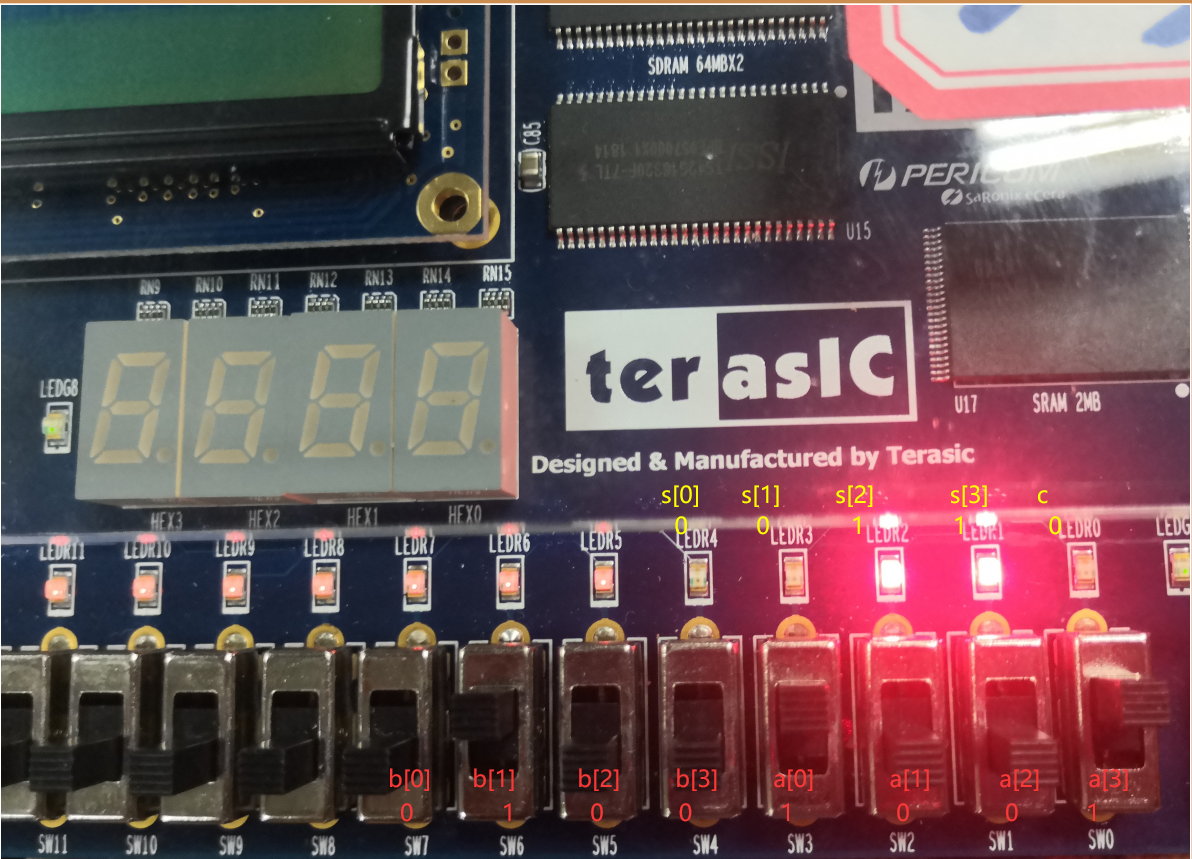

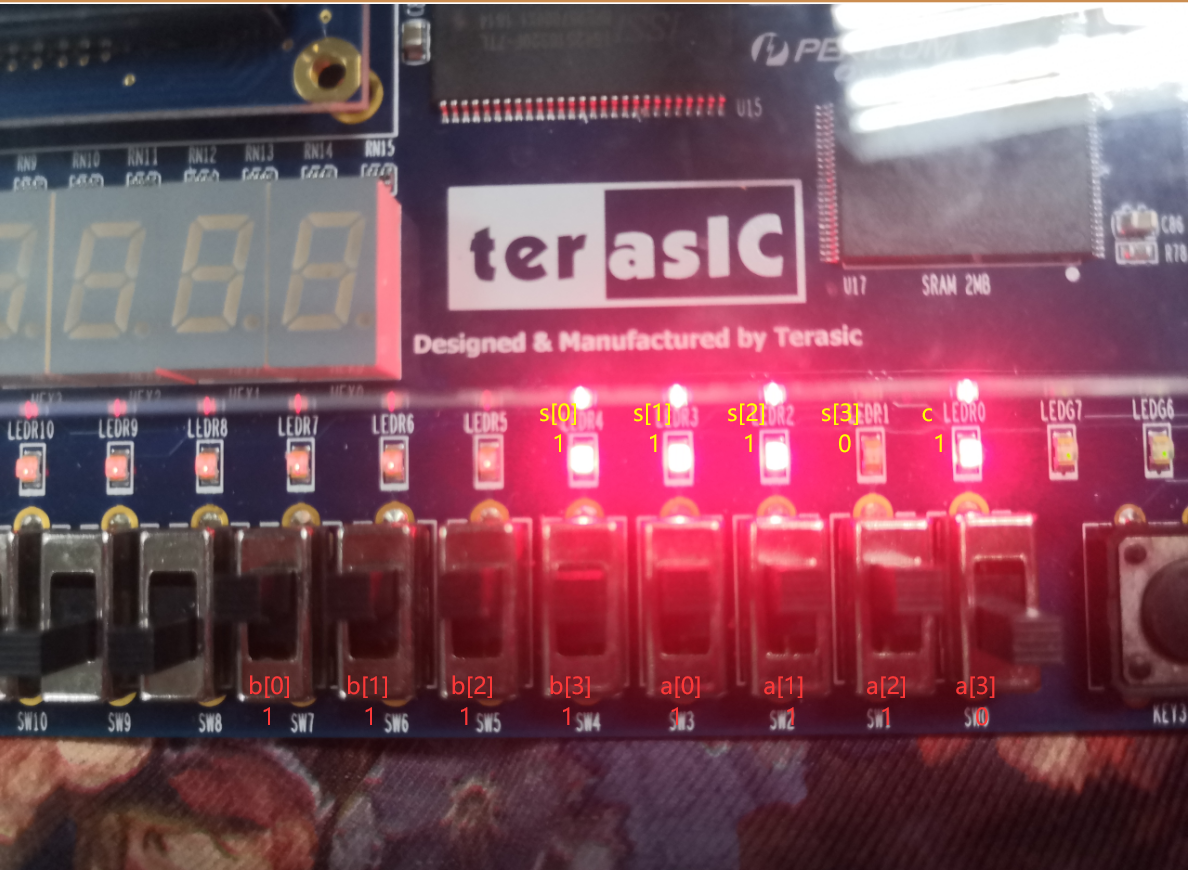

(2)观察图二·

| a[3…0] | b[3…0] | c | s[3…0] |

|---|---|---|---|

| 1101 | 1010 | 1 | 1000 |

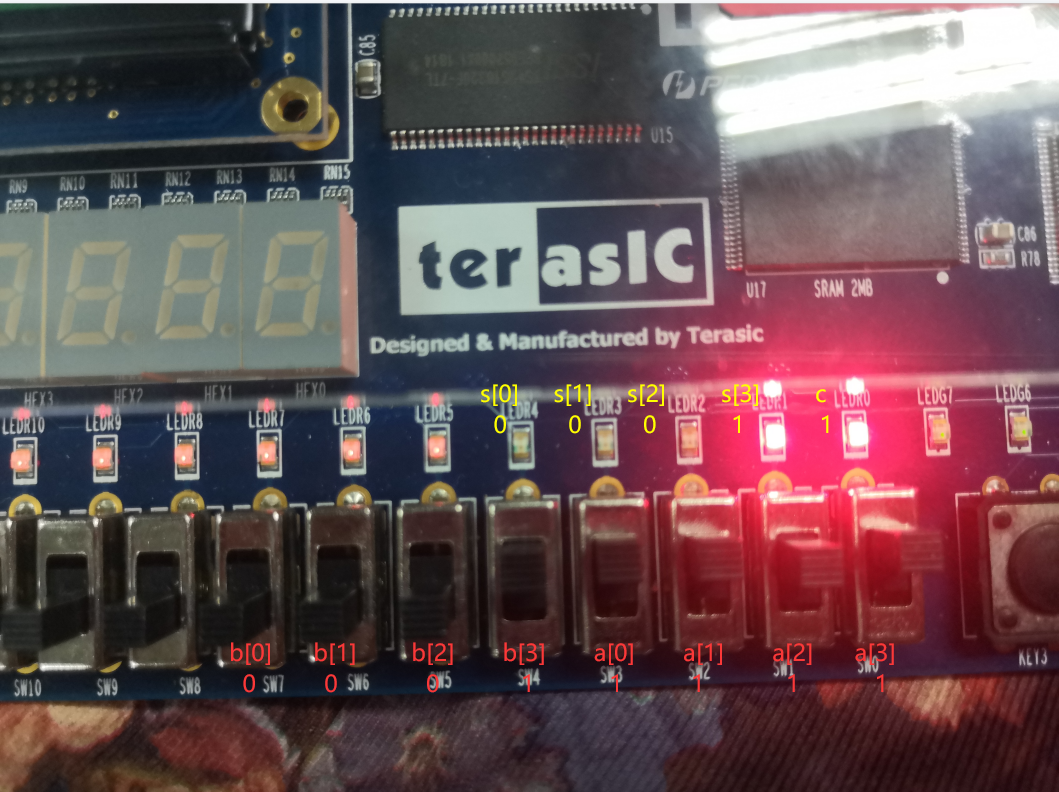

(3)观察图三

| a[3…0] | b[3…0] | c | s[3…0] |

|---|---|---|---|

| 0111 | 1111 | 1 | 0111 |

| |||

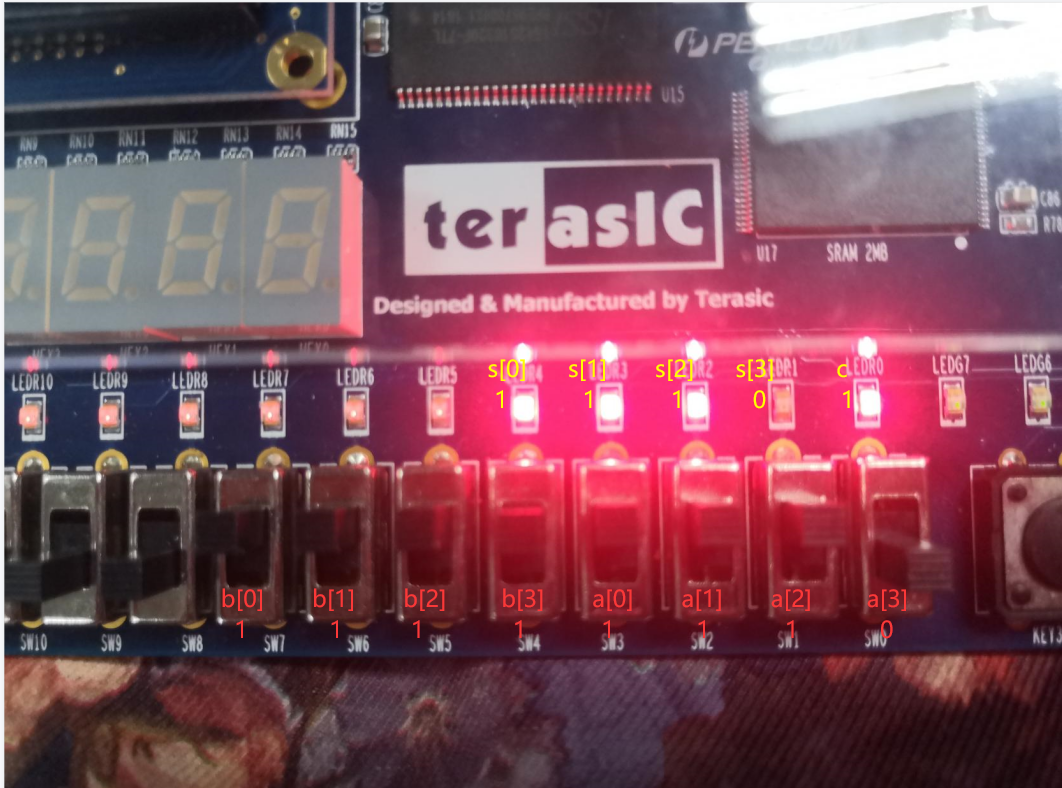

| (4)观察图四 | |||

| a[3…0] | b[3…0] | c | s[3…0] |

| – | – | – | — |

| 1000 | 1111 | 1 | 1000 |

|

(5)观察图五

| a[3…0] | b[3…0] | c | s[3…0] |

|---|---|---|---|

| 0111 | 1111 | 1 | 0111 |

|

二、应用QuartusII 完成基本组合电路设计

(一)二选一多路选择器mux21a

1.Verilog语言

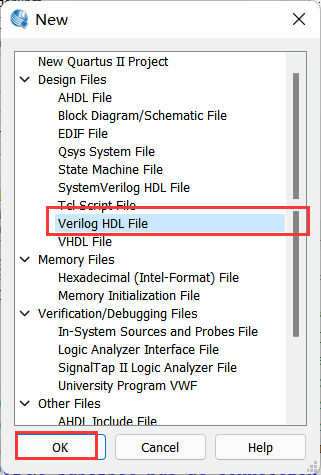

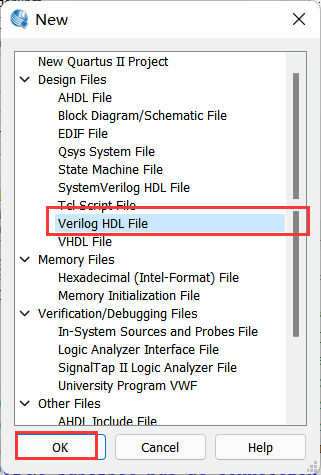

(1)File->New->Verilog HDL File

(2)写入代码后保存

module mux21a(a,b,s,y);

input a,b,s;

output y;

assign y=(s?a:b);

endmodule

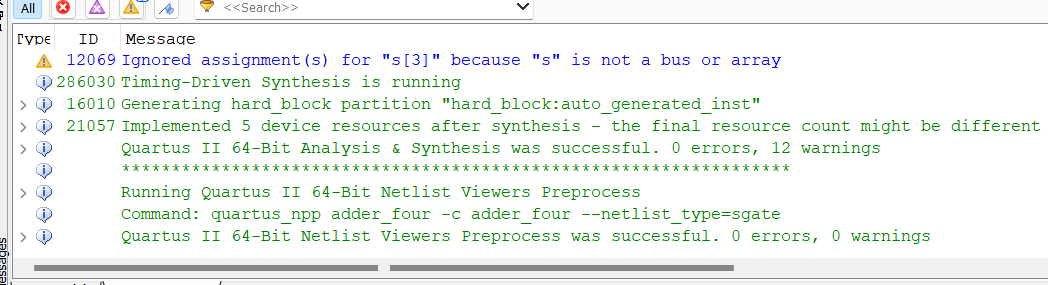

(3)编译,点击图标进行编译,若无错误则可进行下一步,若有错进行修改

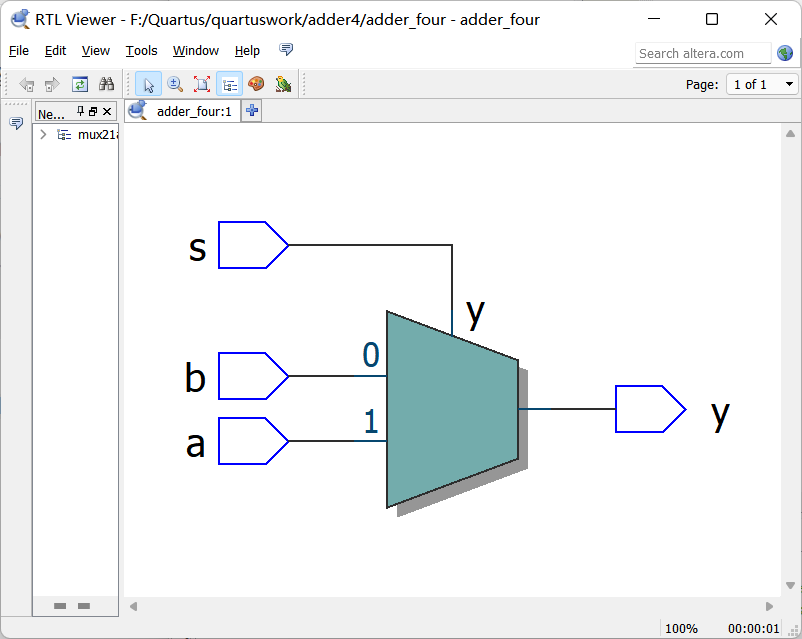

(4)查看硬件电路图,Tools→Netlist Viewers→RTL Viewer

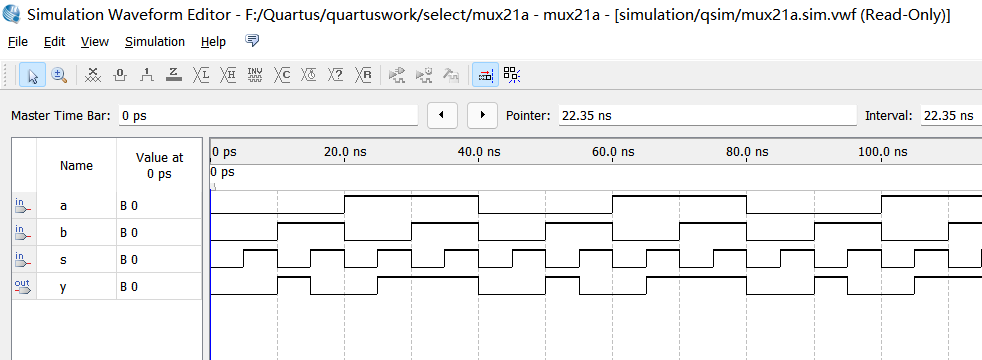

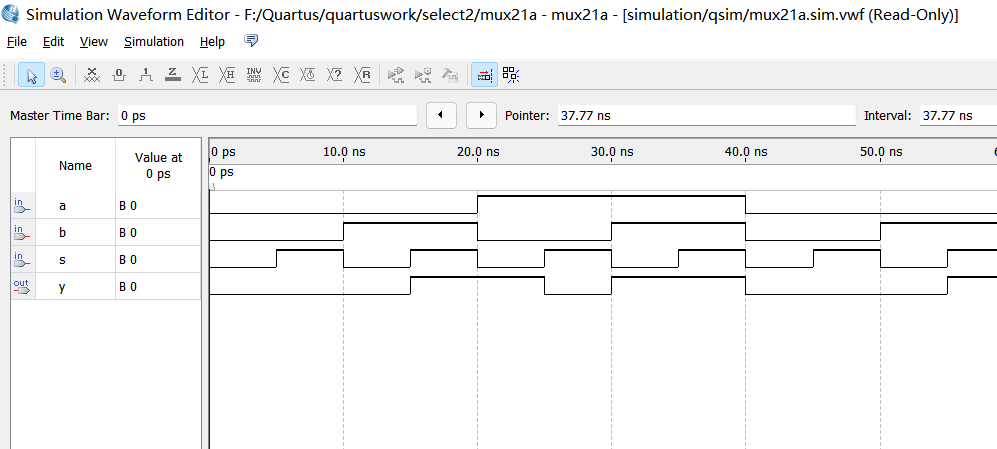

(5)波形仿真图

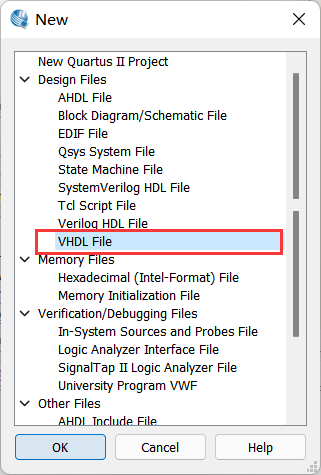

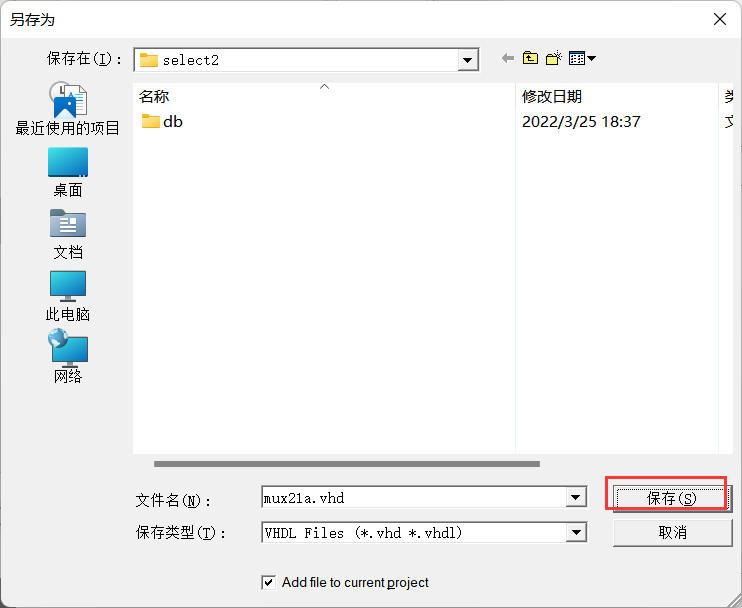

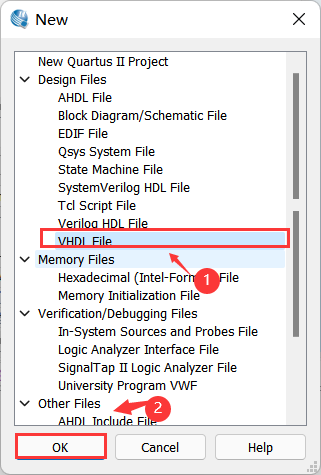

2.VHDL语言

(1)新建VHDL文件,FIle->New ->VHDL File

(2)写入文本语言后保存

Entity mux21a is

port (a , b : in bit;

s : in bit;

y : out bit);

end entity mux21a;

architecture one of mux21a is

begin

y<=a when s ='0' else b;

end architecture one;

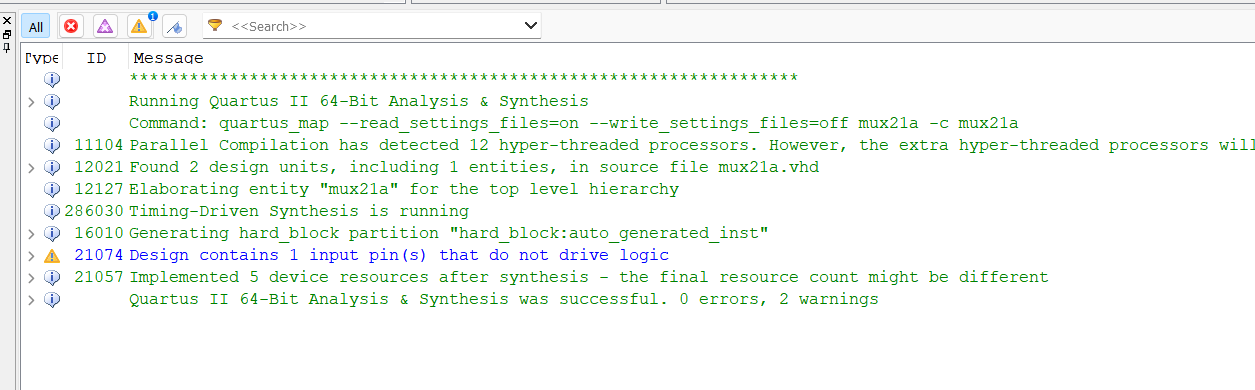

(3)编译

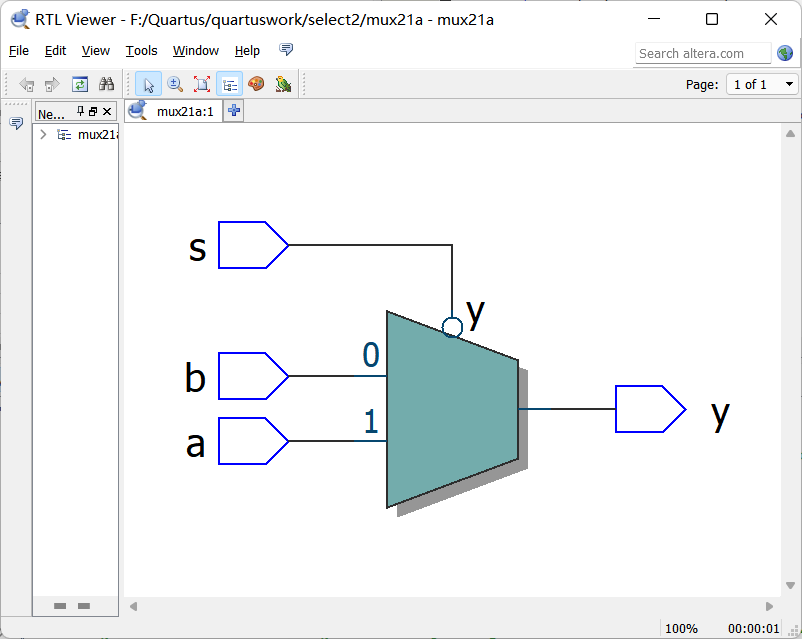

(4)原理图

(5)波形图

3.硬件仿真

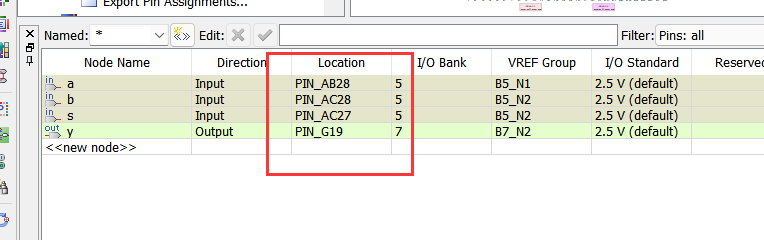

(1)管脚绑定

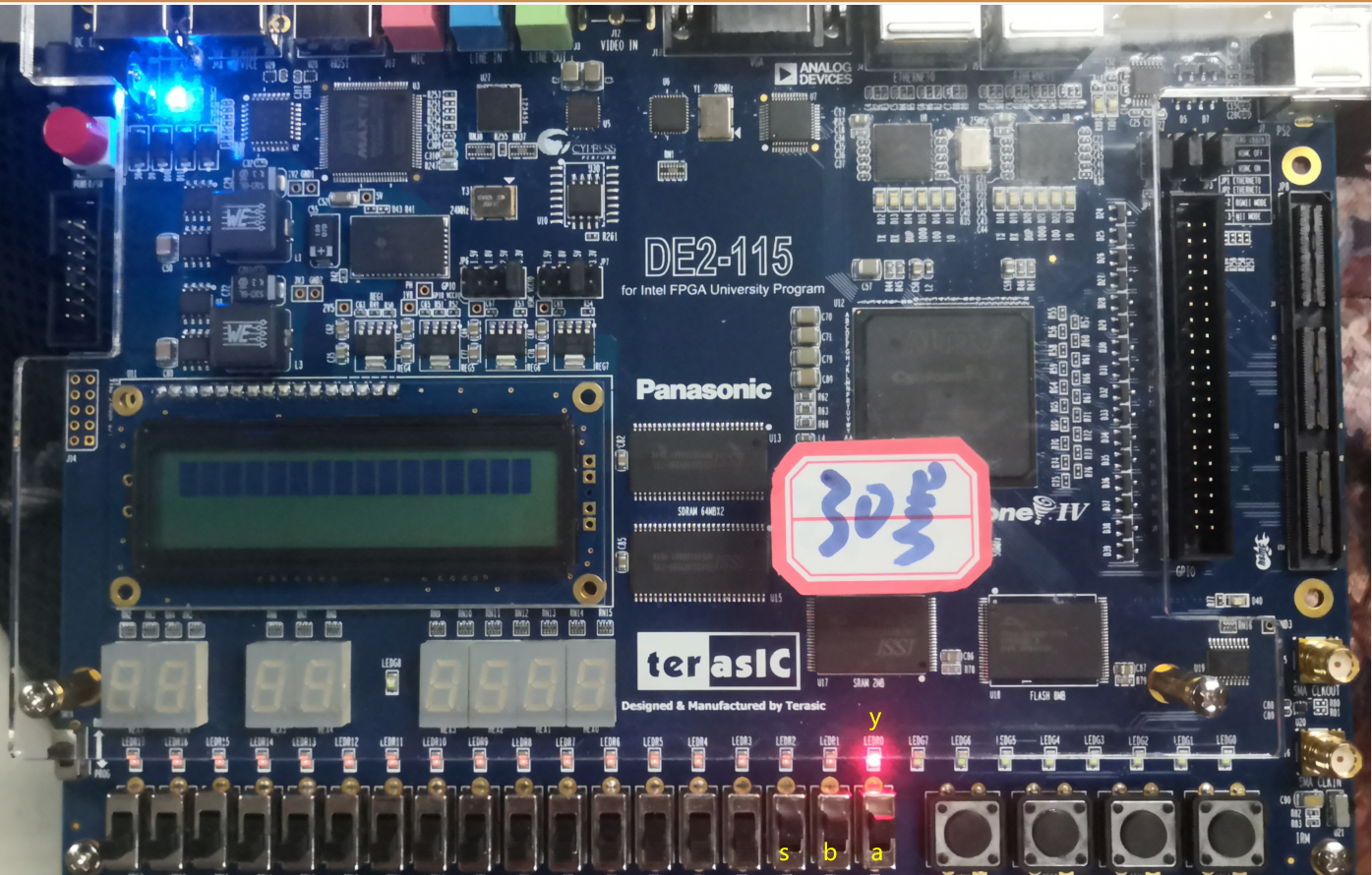

(2)测试结果

s为0时,a路导通; s为1时,b路导通

A。观察图一

| a | b | s | y |

|---|---|---|---|

| 1 | 1 | 0 | 1 |

B。观察图二

| a | b | s | y |

|---|---|---|---|

| 1 | 0 | 1 | 1 |

|

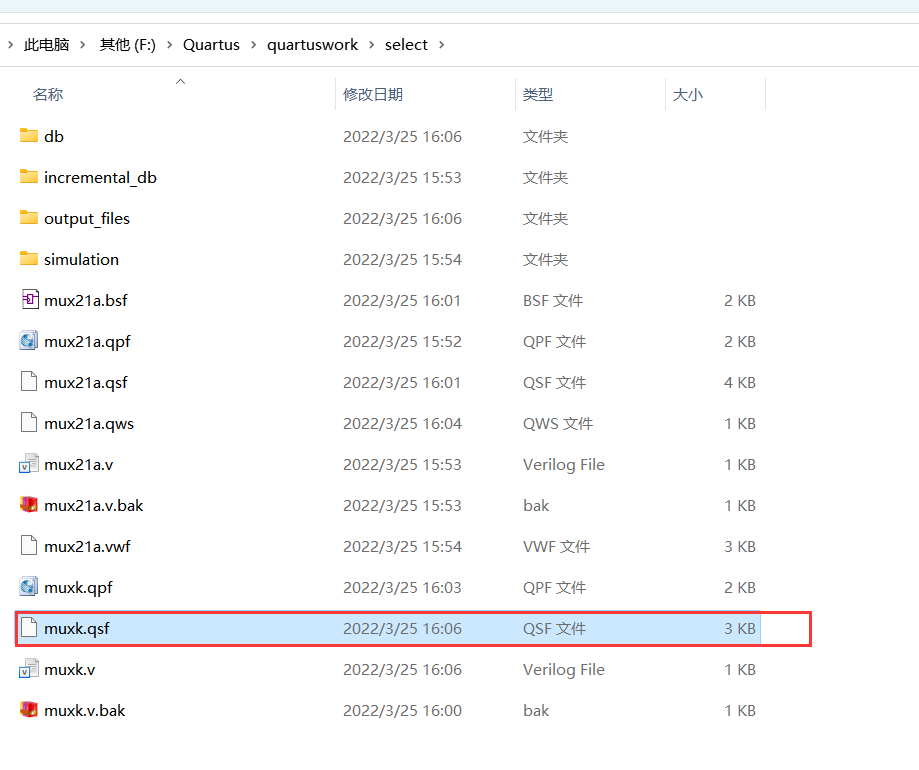

(二)双二选一多路选择器muxk

在当前目录下新建项目同上

1.Verilog语言

.(1)新建文件File->New->Verilog HDL File

(2)写入代码后保存

module muxk(a1,a2,a3,s0,s1,outy);

input a1,a2,a3;

input s0,s1;output outy;

wire tmp;

mux21a u1(.a(a2),.b(a3),.s(s0),.y(tmp));

mux21a u2(.a(a1),.b(tmp),.s(s1),.y(outy));

endmodule

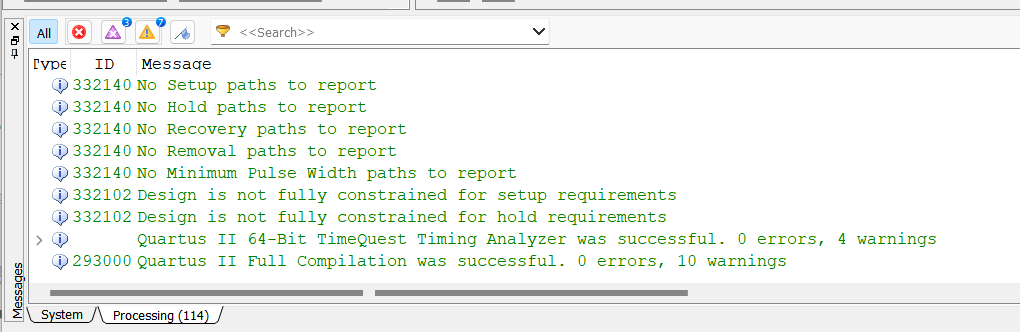

(3).编译仿真

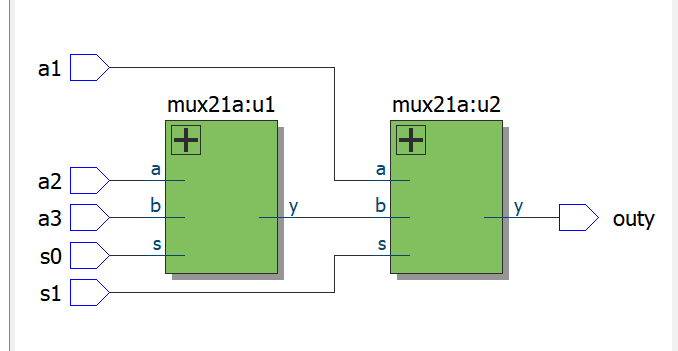

(4)查看硬件电路图,Tools→Netlist Viewers→RTL Viewer

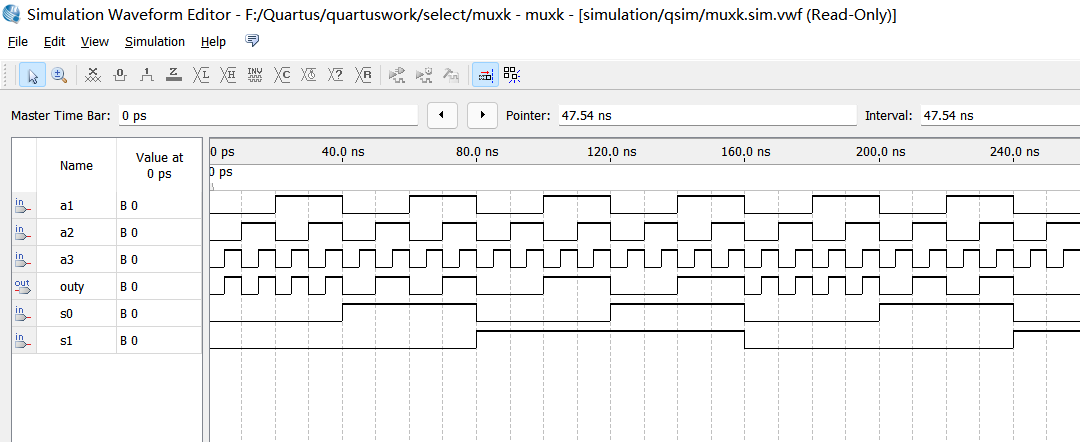

(5)波形仿真图

2.VHDL语言

(1)新建VHDL文件后,写入代码

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY muxk IS

PORT ( a1,a2,a3,S0,S1:in STD_LOGIC;

outy : OUT STD_LOGIC);

END muxk;

ARCHITECTURE BHV OF muxk IS

COMPONENT mux21a

PORT(a,b,s:IN STD_LOGIC;

y :OUT STD_LOGIC);

END COMPONENT;

SIGNAL tmp : STD_LOGIC;

BEGIN

u1 : mux21a PORT MAP(a2, a3, S0, tmp);

u2 : mux21a PORT MAP(a1, tmp, S1, outy);

END BHV;

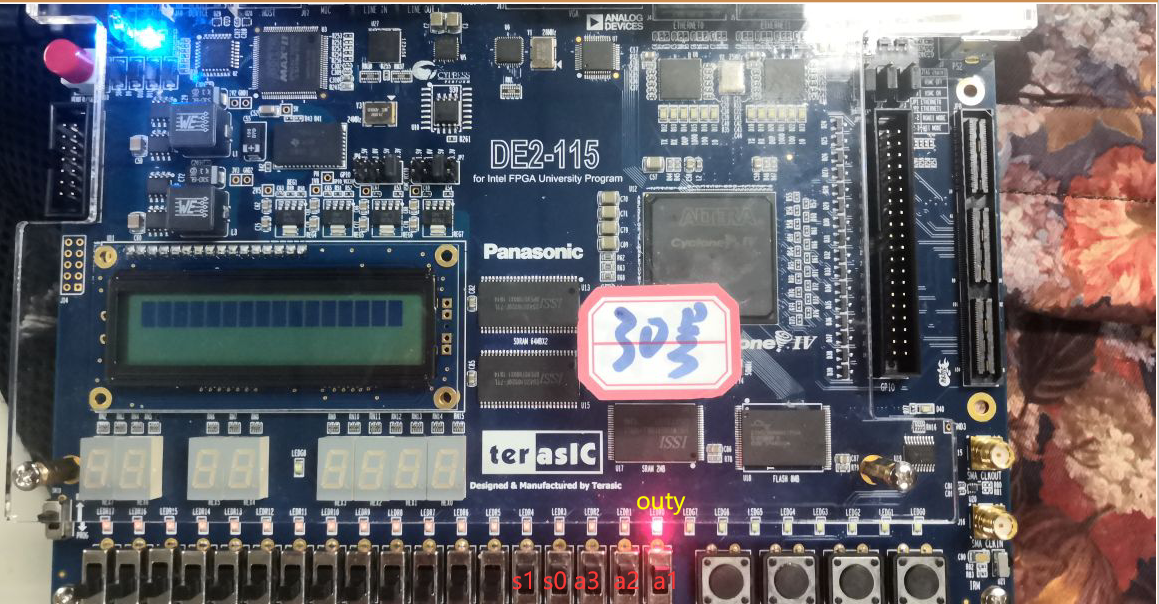

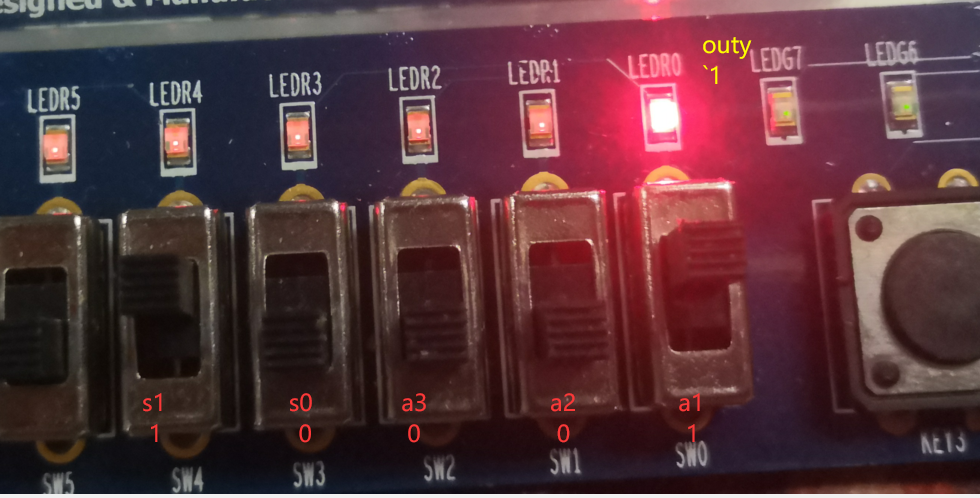

3.硬件仿真

(1)绑定引脚

(2)测试结果

s0为0时,a2路导通; s1为1时,a3路导通

s1为0时,上一个选择器的输出结果作为a路导通; s1为1时,a1路导通

A.观察图一

| a1 | a2 | a3 | s0 | s1 | outy |

|---|---|---|---|---|---|

| 1 | 1 | 1 | 1 | 1 | ! |

B.观察图二

| a1 | a2 | a3 | s0 | s1 | outy |

|---|---|---|---|---|---|

| 1 | 0 | 0 | 0 | 1 | ! |

|

三、QuartusII 完成基本时序电路的设计

(一)设计触发器

1.新建项目

同上新建项目

2.创建VHDL文件

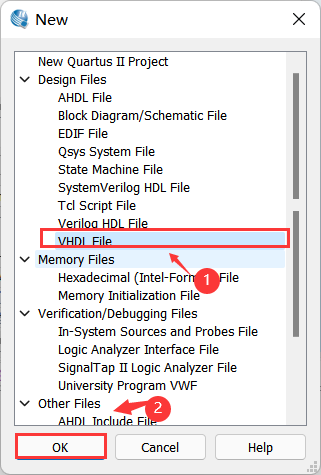

(1)File->New ->VHDL File

(2)添加如下’

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY trigger IS

PORT (CLK : IN STD_LOGIC ;

D : IN STD_LOGIC ;

Q : OUT STD_LOGIC );

END trigger;

ARCHITECTURE bhv OF trigger IS

SIGNAL Q1 : STD_LOGIC ;

BEGIN

PROCESS (CLK,Q1)

BEGIN

IF CLK'EVENT AND CLK = '1' THEN Q1 <= D ; END

IF;

END PROCESS ;

Q <= Q1 ; END

bhv;

(3)保存

4yqCu-4jw==,size_15,color_FFFFFF,t_70,g_se,x_16)

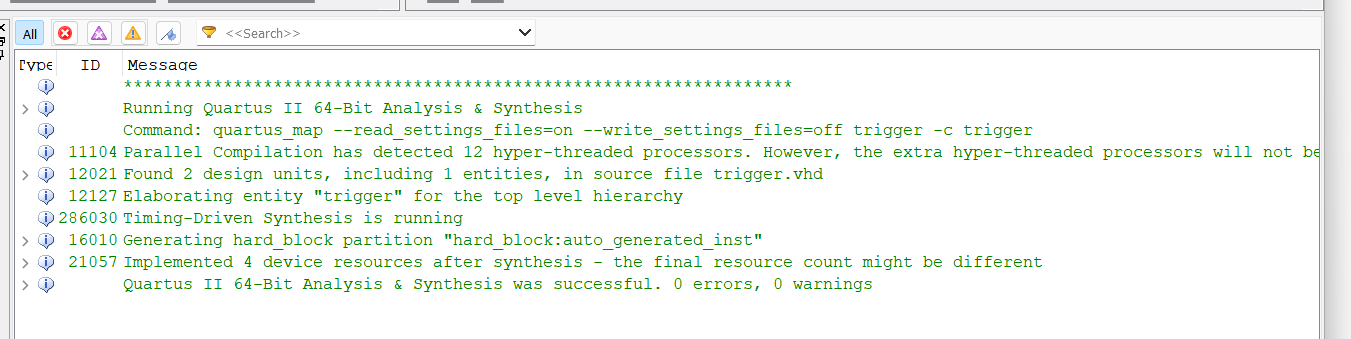

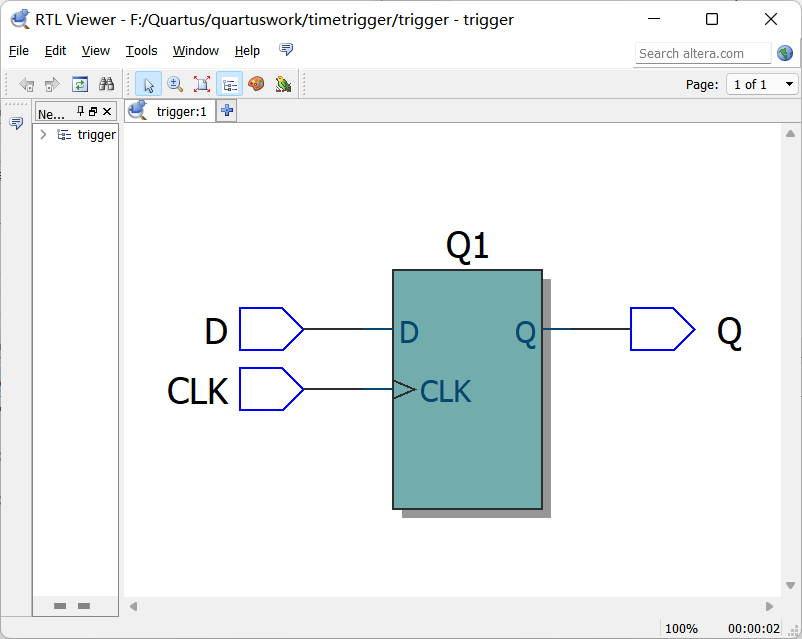

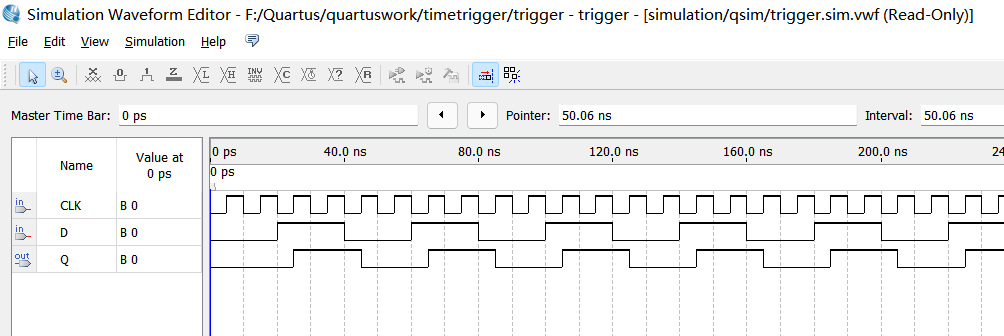

3.编译仿真

(1)编译

(2)原理图

(3)波形仿真

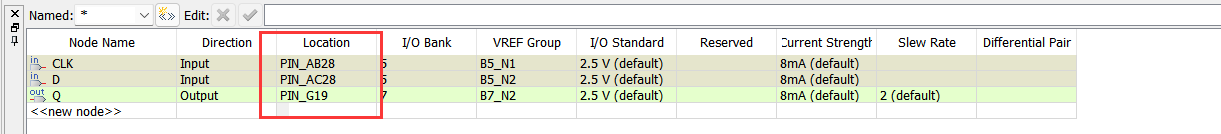

4.硬件仿真

(1)绑定引脚

(2)仿真结果

(二)设计锁存器

1.新建项目

同上新建项目

2.创建VHDL文件

(1)File->New ->VHDL File

(2)添加如下’

LIBRARY IEEE ;

USE IEEE.STD_LOGIC_1164.ALL ;

ENTITY lock IS

PORT (CLK : IN STD_LOGIC ;

D : IN STD_LOGIC ;

Q : OUT STD_LOGIC );

END lock;

ARCHITECTURE bhv OF lock IS

BEGIN

PROCESS (CLK, D) BEGIN

IF CLK = '1'

THEN Q <= D ;

END IF;

END PROCESS ;END

bhv;

(3)保存

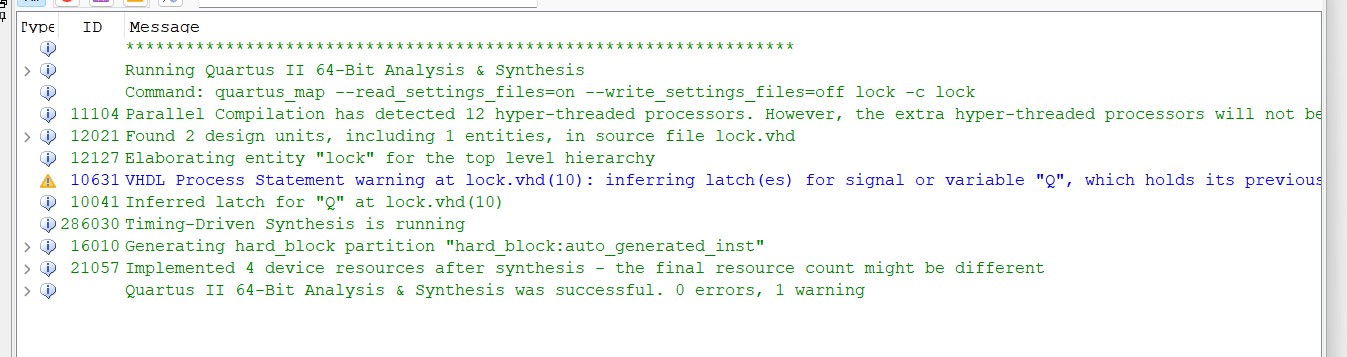

3.编译仿真

(1)编译

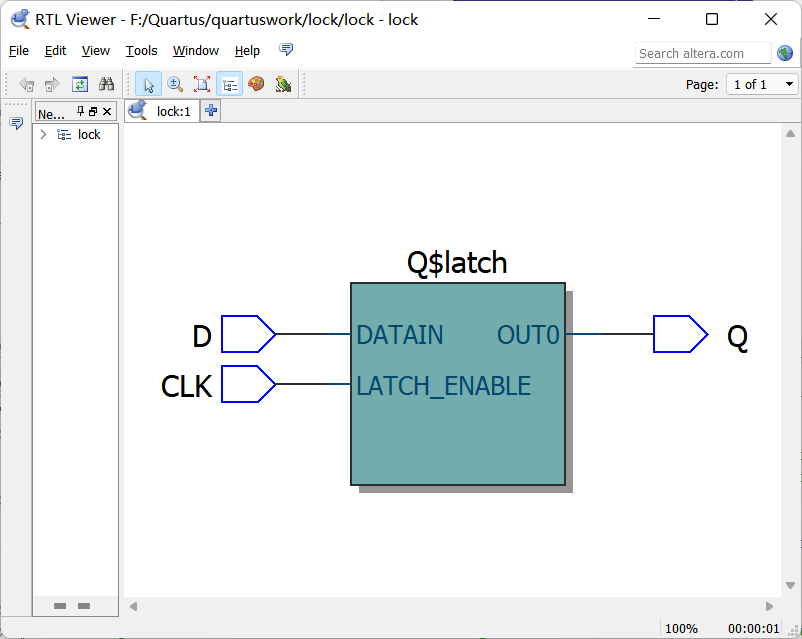

(2)原理图

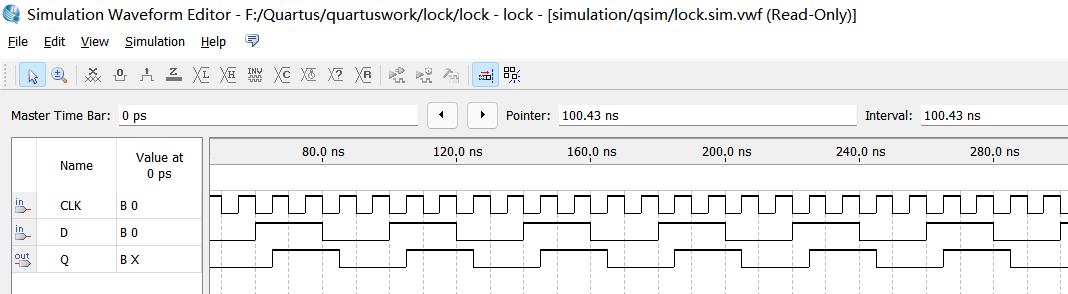

(3)波形仿真

4.硬件仿真

(1)绑定引脚

(2)仿真结果

四、总结

本次实验用到了上传1位全加器的内容,了解了四位全加器的工作原理。理解了二选一多路选择器和和双多路选择器的工作原理。认识了D触发器和锁存器各自的功能特点。也学会了VHDL语言的基本用法。

五、参考资料

实验1 应用QuartusII完成基本组合电路设计

最后

以上就是陶醉雪碧最近收集整理的关于VHDL组合逻辑-时序逻辑练习一、在QuartusII 中用原理图输入法设计 4 位加法器二、应用QuartusII 完成基本组合电路设计三、QuartusII 完成基本时序电路的设计四、总结五、参考资料的全部内容,更多相关VHDL组合逻辑-时序逻辑练习一、在QuartusII内容请搜索靠谱客的其他文章。

发表评论 取消回复