目录

实验目的:

实验预习:

实验讲解1:

D触发器和锁存器的VerilogHDL描述:

实验讲解2:

D触发器的设计

实验内容:十进制加法计数器设计

实验总结

实验目的:

- 熟悉QuartusⅡ软件的使用方法,掌握EDA流程;

- 掌握基本时序逻辑电路的设计方法;

- 学会十进制加法计数器设计,为复杂时序逻辑电路的设计打基础。

实验预习:

- 掌握十进制加法计数器的设计原理;

- 同步、异步电路的实现;

- if语句的用法。

实验讲解1:

D触发器和锁存器的VerilogHDL描述:

module D_ff(D,clk,q); //D触发器

input D,clk;

output reg q;

always@(posedge clk)

q<=D;

end

endmodule

module latchl(D,clk,q); //锁存器

input D,clk;

output reg q;

always@(D or clk)

if(clk)

q<=D;

end

endmodule

锁存器与触发器的共同点:具有0 和1两个稳定状态,一旦状态确定,就能自行保持。一个锁存器/触发器能存储一位二进制码。

锁存器与触发器的不同点:锁存器---对脉冲电平敏感的存储电路,在特定输入脉冲电平作用下改变状态。触发器---对脉冲边沿敏感的存储电路,在时钟脉冲的上升沿或下降沿的变化瞬间改变状态。

语法点1:

时序标志性描述posedge clk:凡是边沿触发性质的时序元件必须使用posedge (negedge) clk,而不用此表述产生的时序电路都是电平敏感性时序电路。其中posedge clk 表示上升沿触发,而negedge clk 表示下降沿触发。

实验讲解2:

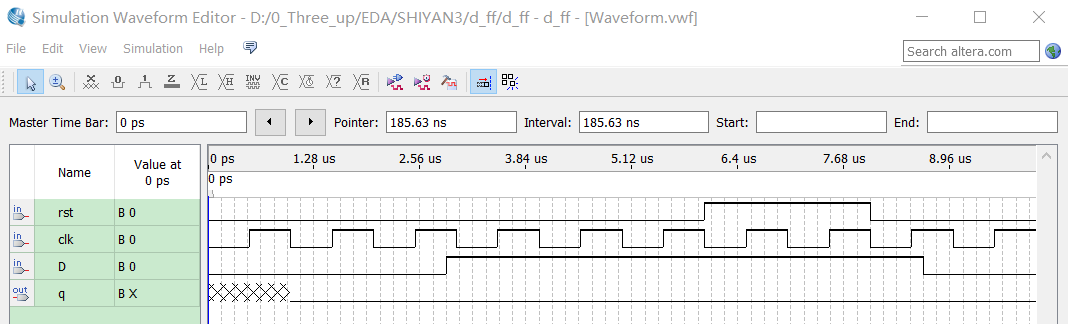

D触发器的设计

module d_ff(rst,D,clk,q);//异步

input rst,D,clk;

output reg q;

always@ (posedge clk or posedge rst)

begin

if(rst)

q<=0;

else

q<=D;

end

endmodule

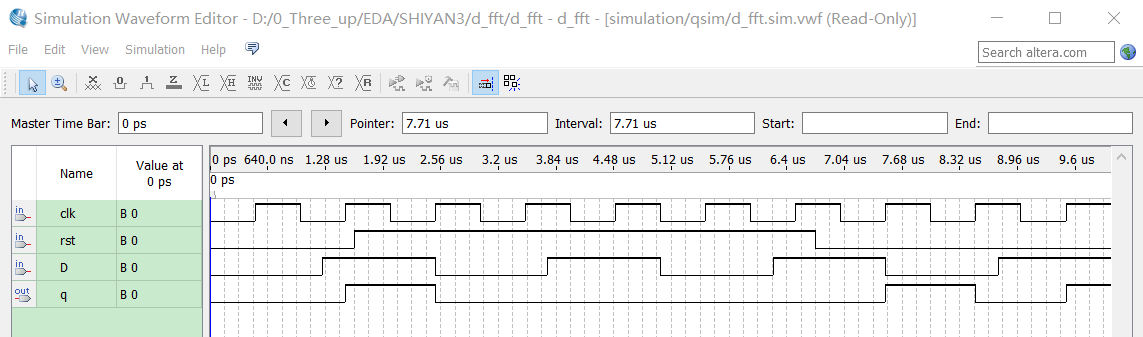

module d_fft(rst,D,clk,q);//同步

input rst,D,clk;

output reg q;

always@ (posedge clk )

begin

if(rst)

q<=0;

else

q<=D;

end

endmodule

语法点2:异步与同步

异步:指独立于时钟控制的复位控制端。即在任何时刻,只要rst=1或0,触发器的输出端立刻被清0,与时钟的状态无关。

使用的语句:

always@(posedge clk or posedge rst)

begin

if(rst) q<=0;

else q<=D;

end

同步:不仅rst有效,且必须时钟上升沿到来,触发器的输出端才清0;

使用的语句

always@(posedge clk )

begin

if(rst) q<=0;

else q<=D;

end

Verilog的时钟过程描述注意要点:当敏感信号表中没有关键词posedge或negedge时,试图通过改变敏感信号的放置来改变逻辑功能是无效的。当敏感信号表中含有关键词posedge或negedge时,通过改变敏感信号的放置可以影响综合结果。

语法点3:条件语句( if语句)

条件语句就是根据判断条件是否成立,确定下一步的运算。if后面的条件表达式一般为逻辑表达式或关系表达式,且必须放在括号内。

执行if语句时,首先计算表达式的值,若结果为0、x或z,按“假”处理;若结果为1,按“真”处理,并执行相应的语句。

Verilog语言中有3种形式的if语句:

格式1为不完整的条件语句,用于产生时序电路,如下所示:

if (condition_expr) true_statement;

格式2为完整的条件语句,产生组合逻辑电路;特定情况产生时序电路,比如posedge CLK等表述的边沿敏感信号,如下所示:

if (condition_expr) true_statement;

else fault_ statement;

格式3为多重嵌套式条件语句,可以产生比较丰富的条件描述,既可产生时序电路,也可产生组合电路。

if (condition_expr1) true_statement1;

else if (condition_expr2) true_statement2;

else if (condition_expr3) true_statement3;

……

else default_statement;

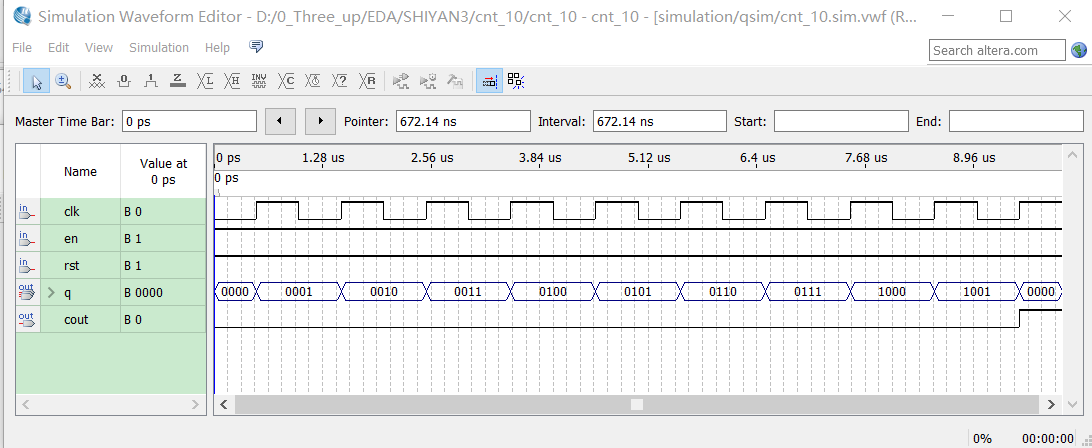

实验内容:十进制加法计数器设计

实验设计要求:设计带异步复位,同步使能的十进制加法计数器。其中,RST为异步复位信号,EN为同步使能信号,CLK为时钟信号。CQ为计数输出,COUT为进位输出。

十进制加法计数器设源程序:

module cnt_10(rst,en,clk,q,cout);//十进制加法器

input rst,en,clk;

output reg[3:0] q;

output reg cout;

always@(posedge clk or negedge rst)

begin

if(~rst) begin q<=4'b0000; cout<=1'b0;end//是0就执行此行

else if(en)

if(q==4'b1001) begin q<=4'b0000;cout<=1'b1; end

else begin q<=q+1'b1; cout<=1'b0;end

end

endmodule语法点4:过程赋值语句(相当于VHDL中的变量赋值)

过程赋值语句出现在initial和always块语句中,赋值符号是“=”,格式为:

赋值变量 = 表达式;

在过程赋值语句中,赋值号“=”左边的赋值变量必须是reg(寄存器)型变量,其值在该语句结束即可得到。如果一个块语句中包含若干条过程赋值语句,那么这些过程赋值语句是按照语句编写的顺序由上至下一条一条地执行,前面的语句没有完成,后面的语句就不能执行,就象被阻塞了一样。因此,过程赋值语句也称为阻塞赋值语句。

在Verilog程序的过程结构中,阻塞式赋值是一种理想化的数据传输,是立即发生的,不存在任何延时行为。

在同一过程结构中,允许对同一目标变量多次赋值,即对于同一目标变量允许有多个驱动源。

具有顺序赋值的特点,即过程中的阻塞式赋值语句的先后顺序位置将直接影响最后的结果或综合结果。

语法点5:非阻塞赋值语句(相当于VHDL中的信号赋值)

非阻塞赋值语句也是出现在initial和always块语句中,赋值符号是“<=”,格式为:

赋值变量 <= 表达式;

在非阻塞赋值语句中,赋值号“<=”左边的赋值变量也必须是reg型变量,其值不象在过程赋值语句那样,语句结束时即刻得到,而在该块语句结束才可得到。

建议:在时序逻辑电路的设计中,采用非阻塞型赋值语句。

在Verilog程序的过程中,非阻塞赋值语句比较接近真实的电路赋值和输出,其有一个特殊的延时操作,而且在赋值过程中不影响其它同类语句的赋值操作。同阻塞式赋值一样,允许对同一目标信号多次赋值或驱动。Verilog规定,被赋值的目标变量接受最接近过程结束的那一个驱动源的数据。

例如,在下面的块语句中包含4条赋值语句

always @(posedge clock)

m = 3;

n = 75;

n <= m;

r = n;

语句执行结束后,r的值是75,而不是3,因为第3行是非阻塞赋值语句“n <= m”,该语句要等到本块语句结束时,n的值才能改变。

实验任务1:

学生实现十进制加法计数器的代码输入、综合、软件仿真;对软件仿真结果进行认真的分析,并通过软件仿真的结果来修改设计;

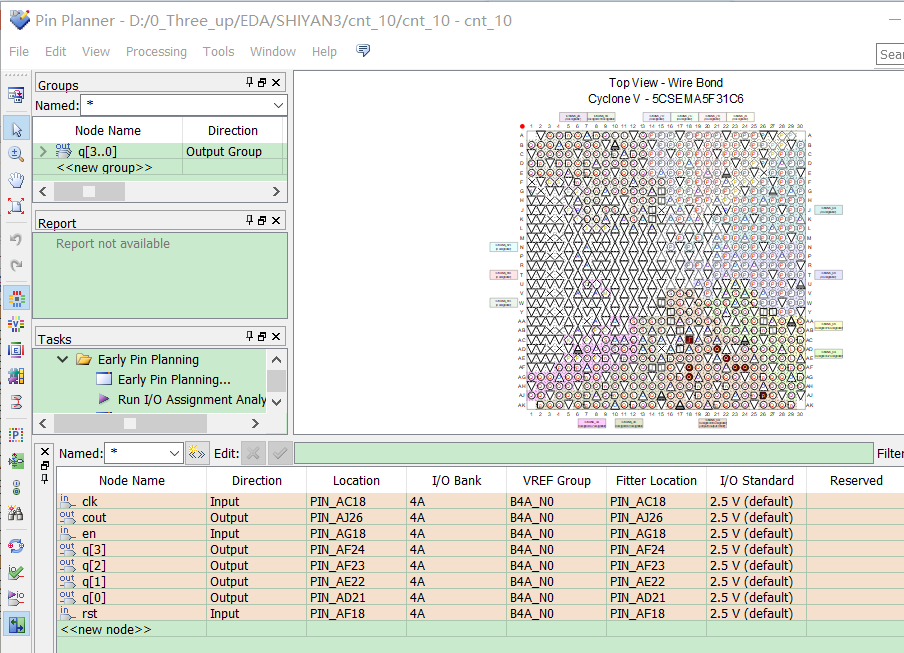

实验任务2:

学生根据十进制加法计数器的输入输出端口选择电路模式,并进行相应的引脚锁定、编程下载和硬件验证。

【时钟由系统的clkB0或者B1输入,使能信号、复位信号则由按键输入,输出cout则由led灯显示,其余由数码管显示数值】

实验总结

最后

以上就是爱笑吐司最近收集整理的关于EDA(Quartus II)——十进制加法计数器设计实验目的:实验预习:实验总结的全部内容,更多相关EDA(Quartus内容请搜索靠谱客的其他文章。

发表评论 取消回复