目的

1. 掌握VHDL语言的时序逻辑电路的设计方法;

2. 掌握计数器的设计方法。

内容

设计并实现一个带有异步复位、同步时钟使能的十进制计数器。要求根据计数器的设计原理编写出十进制计数器的VHDL语言程序,并利用开发工具软件对其进行编译和仿真,最后通过实验开发系统对其进行硬件验证。

原理

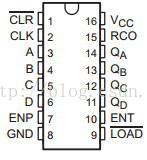

CD54HC160是具有异步复位的BCD同步十进制计数器。其引脚图如图2-30所示。其中,CLR为计数器复位端,CLR=0时,QDQCQBQA=0000;LOAD是计数器的预置端,DCBA是预置数据输入端。当LOAD=0时,在CLK的上升沿作用下,QDQCQBQA=DCBA;ENP和ENT是计数器的功能控制端,ENP和ENT均为高电平时计数器才能计数,它们中有任何一个为低电平时,计数器的装备不会发生变化,而是处于保持状态。RCO是计数器的进位输出,RCO=ENT× QDQA。

图2-30 CD54HC160引脚图

步骤

1.根据十进制计数器的原理和特点,利用VHDL语言的基本描述语句编写出十进制计数器的VHDL语言程序。

2.对所设计的十进制计数器的VHDL程序进行编译,然后利用波形编辑器对其进行仿真,初步验证程序设计的正确性。

3.利用开发工具软件,选择所用可编程逻辑器件,并对十进制计数器进行管脚配置。

4.通过下载电缆将编译后的*.sof文件下载到目标器件之中,并利用实验开发装置对其进行硬件验证。

程序

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CD54HC160 IS

PORT(

CLK,D,C,B,A, CLR, LOAD,ENP,ENT: IN STD_LOGIC;

QD,QC,QB,QA,RCO: BUFFER STD_LOGIC);

END CD54HC160;

ARCHITECTURE behave OF CD54HC160 IS

SIGNAL EN: STD_LOGIC_VECTOR(1 DOWNTO 0);

SIGNAL D_SIGNAL: STD_LOGIC_VECTOR(3 DOWNTO 0);

SIGNAL Q_SIGNAL: STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

PROCESS(LOAD,D,C,B,A,CLK,CLR, ENP,ENT)

BEGIN

EN<=(ENP&ENT);

D_SIGNAL<=(D&C&B&A);

IF (CLR='0') THEN

Q_SIGNAL<=(OTHERS=>'0');

ELSE IF CLK'EVENT AND CLK='1' THEN

IF (LOAD='0') THEN Q_SIGNAL<=D_SIGNAL;

ELSIF (EN="11") THEN

IF Q_SIGNAL<"1001" THEN

Q_SIGNAL<=Q_SIGNAL+1;

ELSE

Q_SIGNAL<=(OTHERS=>'0');

END IF;

ELSE

Q_SIGNAL<=Q_SIGNAL;

END IF;

END IF;

END IF;

QD<=Q_SIGNAL(3);

QC<=Q_SIGNAL(2);

QB<=Q_SIGNAL(1);

QA<=Q_SIGNAL(0);

RCO<=ENT AND QD AND QA;

END PROCESS;

END behave;

问题及解决

注释1.0V那行,文件名与实体名一致

总结:虽然在功能上完全实现了课题的要求,即实现了十进制计数器的设计的全部要求,但是相应的不足之处还应该考虑到。虽然是细节问题,但往往可以决定成败,试着理解程序。

最后

以上就是霸气小懒虫最近收集整理的关于十进制计数器的设计的全部内容,更多相关十进制计数器内容请搜索靠谱客的其他文章。

发表评论 取消回复