计数器不仅能用于对时钟脉冲计数,还可以用于分频,定时,产生节拍脉冲序列以及进行数字运算等,分为同步计数器和异步计数器,在同步计数器中,当时钟脉冲的输入时,触发器的翻转是同时发生的。而在异步计数中,触发器的翻转有先有后,不是同时发生的。

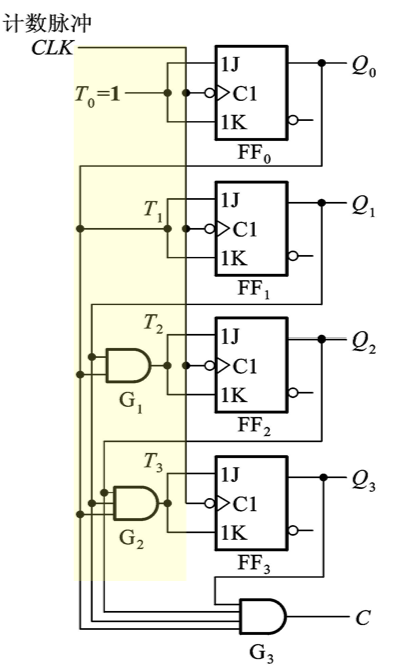

1.同步四位二进制加法计数器:

各触发器的驱动方程:

T0 = 1;

T1 = Q0

T2 = Q0Q1

T3 = Q0Q1Q2

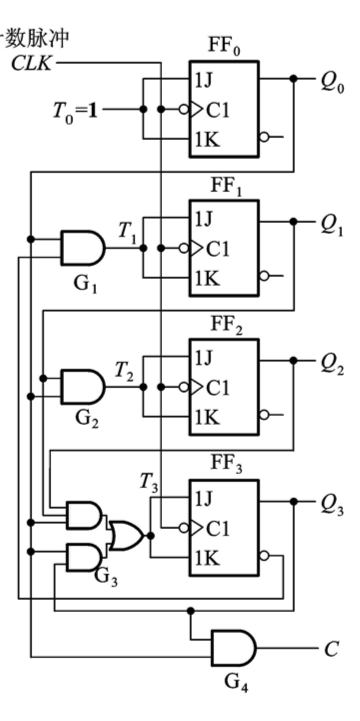

2.四位10进制的计数器

在四位二进制计数器的基础上修改,当计算到1001时,则下一个clk状态回到0000

驱动方程:

T0 = 1;

T1 = Q0Q3`

T2 = Q0Q1

T3 = Q0Q1Q2 + Q0Q3`

其verilog编程比较简单:用一个always块即可实现:

`timescale 1ns/10ps

module counter10(clk,rst,count);

input clk,rst;

output [3:0] count;

reg [3:0] q;

assign count = q;

always@(posedge clk)

begin

if(!rst)

q <= 0;

else if(q >= 4'd9)

q <= 0;

else

q <= q + 1;

end

endmodule

编写一个testbench

module counter10_tb();

reg rst;

reg clk;

wire [3:0] count;

counter10 wt(.clk(clk),.rst(rst), .count(count));

initial

begin

rst <= 0;

clk <= 0;

#50 rst <= 1;

#2000 rst <= 0;

end

always

#10 clk = ~clk;

endmodule

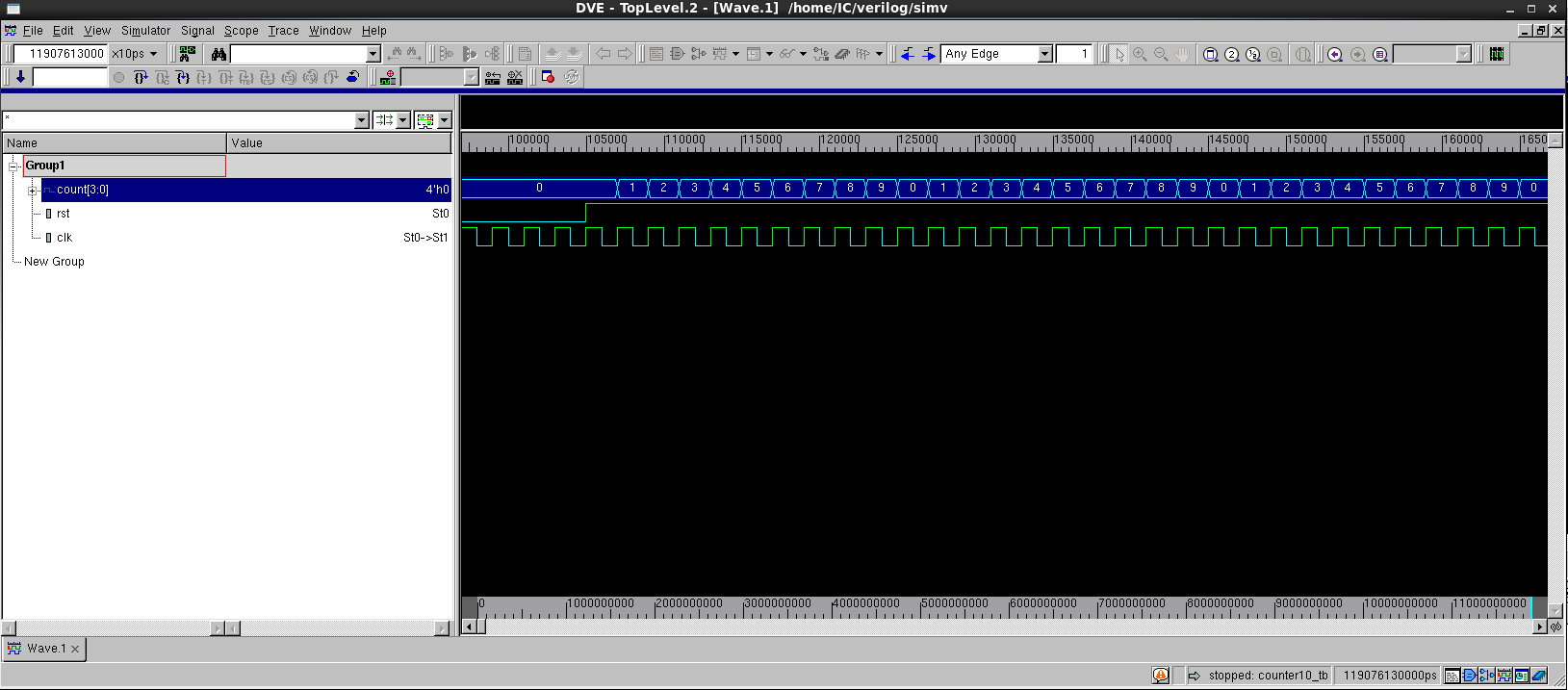

通过vcs仿真:vcs add10 -R -gui +v2k

得到的波形:

最后

以上就是优秀溪流最近收集整理的关于10进制计数器Verilog编程的全部内容,更多相关10进制计数器Verilog编程内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复