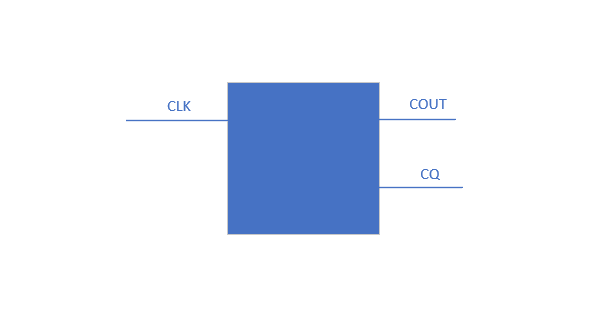

在进行十进制计数器设计时,首先逢十进一即0,1,2,3,4,5,6,7,8,9,计数器进位1,然后重新计数。由此我们可以得到,每当时检测钟信号的上升沿时计数器计数一次,当计数器记到9时计数器输出进位。于是我们大致可以画出一个十进制计数器的示意图

其中CLK代表时钟信号,COUT代表进位,CQ代表计数。

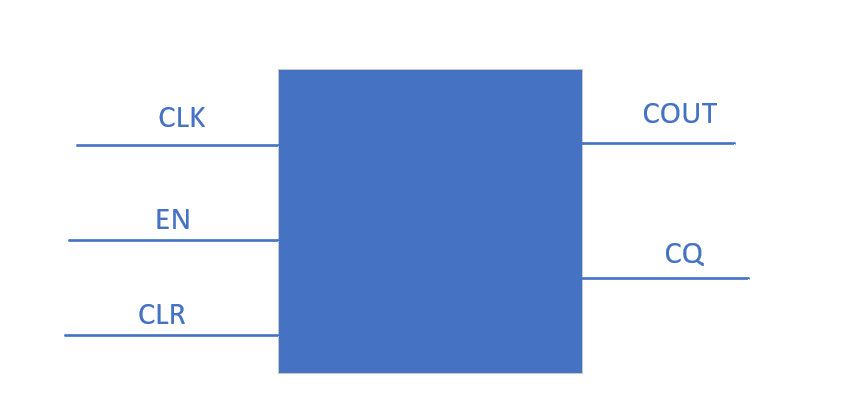

在实际使用我们常常需要对计数器进行复位,同时控制计数器是否计数。这两个信号都为输入信号

所以一个标准的十进制计数器应该为

接下来编写代码

具体思路大概为,定义一个数据暂存点,利用CQX<=CQX+1来进行计数,在再将CQX指向CQ。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity jz10 is

port(CLK,RST,EN : in std_logic;

CQ : out std_logic_vector(3 downto 0);--定义端口名

COUT : out std_logic);

end jz10;

architecture behav of jz10 is

signal CQX : std_logic_vector(3 downto 0);--类似于一个在芯片内部的数据暂存点

begin

process(CLK,RST,EN)

begin

if RST ='1' then CQX<=(OTHERS=>'0');--计数器异步复位

elsif clk'event and CLK='1' then--检测时钟上升延

if EN='1' then--检测是否允许计数

if CQX<9 then--允许计数,同时检测是否小于9

CQX<=CQX+1;--计数

else CQX<=(OTHERS=>'0');--大于9计数值清零

end if;

end if;

end if;

if CQX=9 then COUT<='1';--进位

else COUT<='0';

end if;

end process;

CQ<=CQX;--将计数值指向输出端口

end behav;其中CQX<=CQX+1表示两个不同的时刻,右边为当前时刻,CQX若先要+1则需要等到下一个时钟上升沿。

最后

以上就是幸福故事最近收集整理的关于十进制计数器的设计(vhdl)的全部内容,更多相关十进制计数器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复