一 .4位加器的门级建模

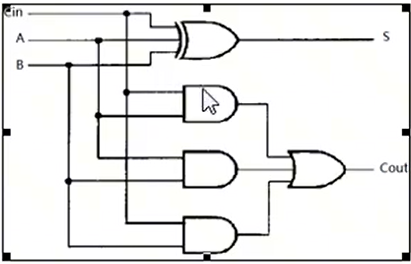

1.电路结构如图:

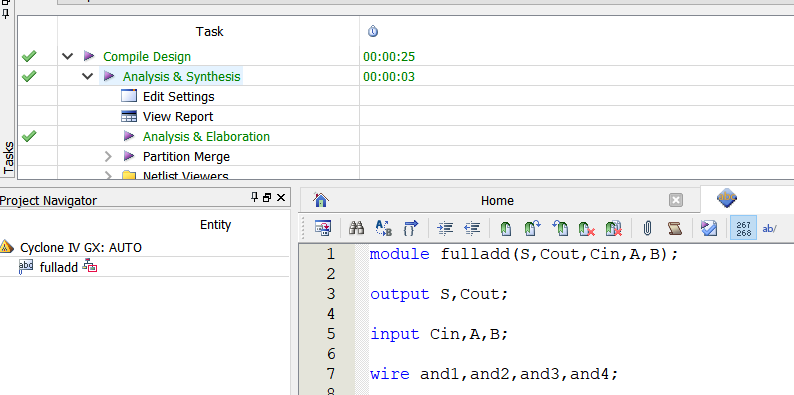

2.编写代码:module fulladd(S,Cout,Cin,A,B);

output S,Cout;

input Cin,A,B;

wire and1,and2,and3,and4;

xor (S,Cin,A,B);

and (and1,Cin,A);

and (and2,A,B);

and (and3,Cin,B);

or (Cout,and1,and2,and3);

endmodule

module add4a(S3,S2,S1,S0,COUT,CIN,X3,X2,X1,X0,Y3,Y2,Y1,Y0);

output COUT,S3,S2,S1,S0;

input CIN, X3,X2,X1,X0,Y3,Y2,Y1,Y0;

wire c0,c1,c2;

fulladd add0(.S(S0), .Cout(c0), .Cin(CIN), .A(X0), .B(Y0));

fulladd add1(.S(S1), .Cout(c1), .Cin(c0), .A(X1), .B(Y1));

fulladd add2(.S(S2), .Cout(c2), .Cin(c1), .A(X2), .B(Y2));

fulladd add3(.S(S3), .Cout(COUT), .Cin(c2), .A(X3), .B(Y3));

endmodule

module add4(S,COUT,CIN,X,Y);//ËÄλȫ¼ÓÆ÷

output COUT;

output [3:0] S;

input CIN;

input [3:0]X,Y;

wire c0,c1,c2;

fulladd add0(.S(S[0]), .Cout(c0), .Cin(CIN), .A(X[0]), .B(Y[0]));

fulladd add1(.S(S[1]), .Cout(c1), .Cin(c0), .A(X[1]), .B(Y[1]));

fulladd add2(.S(S[2]), .Cout(c2), .Cin(c1), .A(X[2]), .B(Y[2]));

fulladd add3(.S(S[3]), .Cout(COUT), .Cin(c2), .A(X[3]), .B(Y[3]));

endmodule

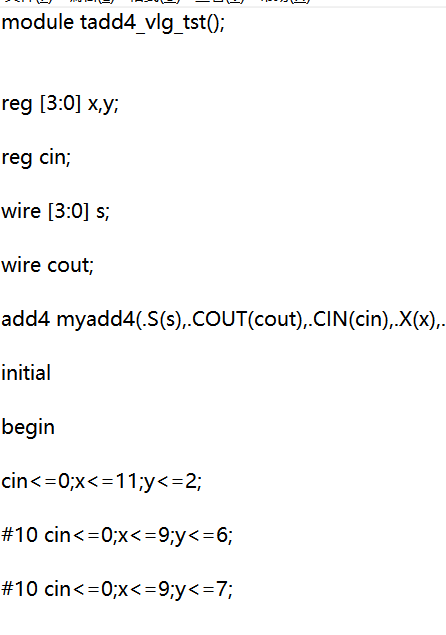

3.测试代码:module tadd4;

reg [3:0] x,y;

reg cin;

wire [3:0] s;

wire cout;

add4 myadd4(.S(s),.COUT(cout),.CIN(cin),.X(x),.Y(y));

initial

begin

cin<=0;x<=11;y<=2;

#10 cin<=0;x<=9;y<=6;

#10 cin<=0;x<=9;y<=7;

#10 cin<=1;x<=11;y<=2;

#10 cin<=1;x<=9;y<=6;

#10 cin<=1;x<=9;y<=7;

#10 $stop;

end

endmodule

4.用quartus II 进行编译代码并生成测试文件,改写测试文件,调用modelsim进行仿真。

5.

6.点击star,生成Test bench文件,并改写。

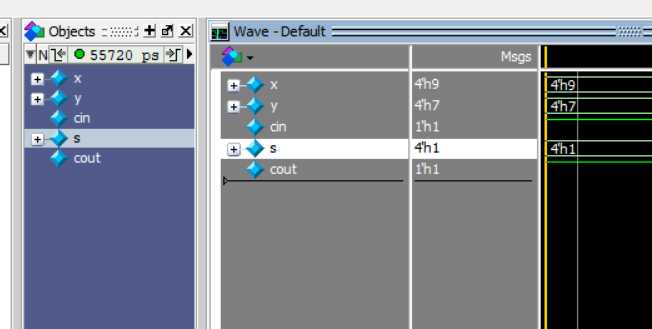

7.调用modelsim开始仿真,仿真结果如图:

二.quartus ii 和modelsim联合仿真

1.测试代码:

module fulladd(sum,c_out,a,b,c_in);

output sum,c_out;

input a,b,c_in;

wire s1,c1,c2;

xor (s1,a,b);

and (c1,a,b);

xor (sum,s1,c_in);

and (c2,s1,c_in);

or (c_out,c2,c1);

endmodule

2.测定代码编写:

module fulladd(sum,c_out,a,b,c_in);

output sum,c_out;

input a,b,c_in;

wire s1,c1,c2;

xor (s1,a,b);

and (c1,a,b);

xor (sum,s1,c_in);

and (c2,s1,c_in);

or (c_out,c2,c1);

endmodule

3.用quartus ii编译代码成功后,并点击star生成test bench。

4.编写test bench文件,代码如上。

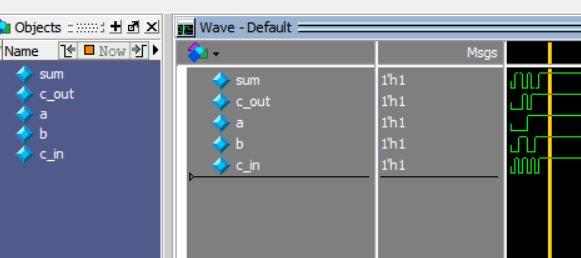

5.调用modelsim进行仿真

6.仿真结果如下:

最后

以上就是细腻铅笔最近收集整理的关于4位加器的门级建模和quartus ii和modelsim联合仿真的全部内容,更多相关4位加器的门级建模和quartus内容请搜索靠谱客的其他文章。

发表评论 取消回复