概念

寄存器具有存储功能,一般是由D触发器构成,由时钟脉冲控制,每个D触发器能存储一位二进制码。

工作原理

在一个脉冲信号上升沿或者是下降沿作用下,将信号从输入端D送到输出端Q。若时钟脉冲的边沿信号未出现,即使输入信号改变,输出信号仍然保持原值,且寄存器有复位清零功能,其复位分为同步复位和异步复位。

同步复位

“同步”是和工作时钟同步的意思。当时钟的上升沿(下降沿)来到时检测到按键的复位操作才有效,否则无效。

异步复位

“异步”是和工作时钟不同步的意思。寄存器的复位不关心时钟的上升沿(下降沿)来不来,只要检测到有按键按下,就立刻执行操作。

代码

同步复位

//同步复位的D触发器

module flip_flop(

input wire sys_clk,

input wire sys_rst,

input wire key_in,

output reg led_out

);

always @ (posedge sys_clk ) begin

if(sys_rst == 1'b1) begin

led_out <= 1'b0;//赋初始值为0

end

else begin

led_out <= key_in;

end

end

endmodule

异步复位

//异步复位的D触发器

module flip_flop2(

input wire clk,

input wire rst,

input wire key_in,

output reg led_out

);

always @ (posedge clk or posedge rst) begin

if(rst == 1'b1)begin

led_out <= 1'b0;

end

else begin

led_out <= key_in;

end

end

endmodule

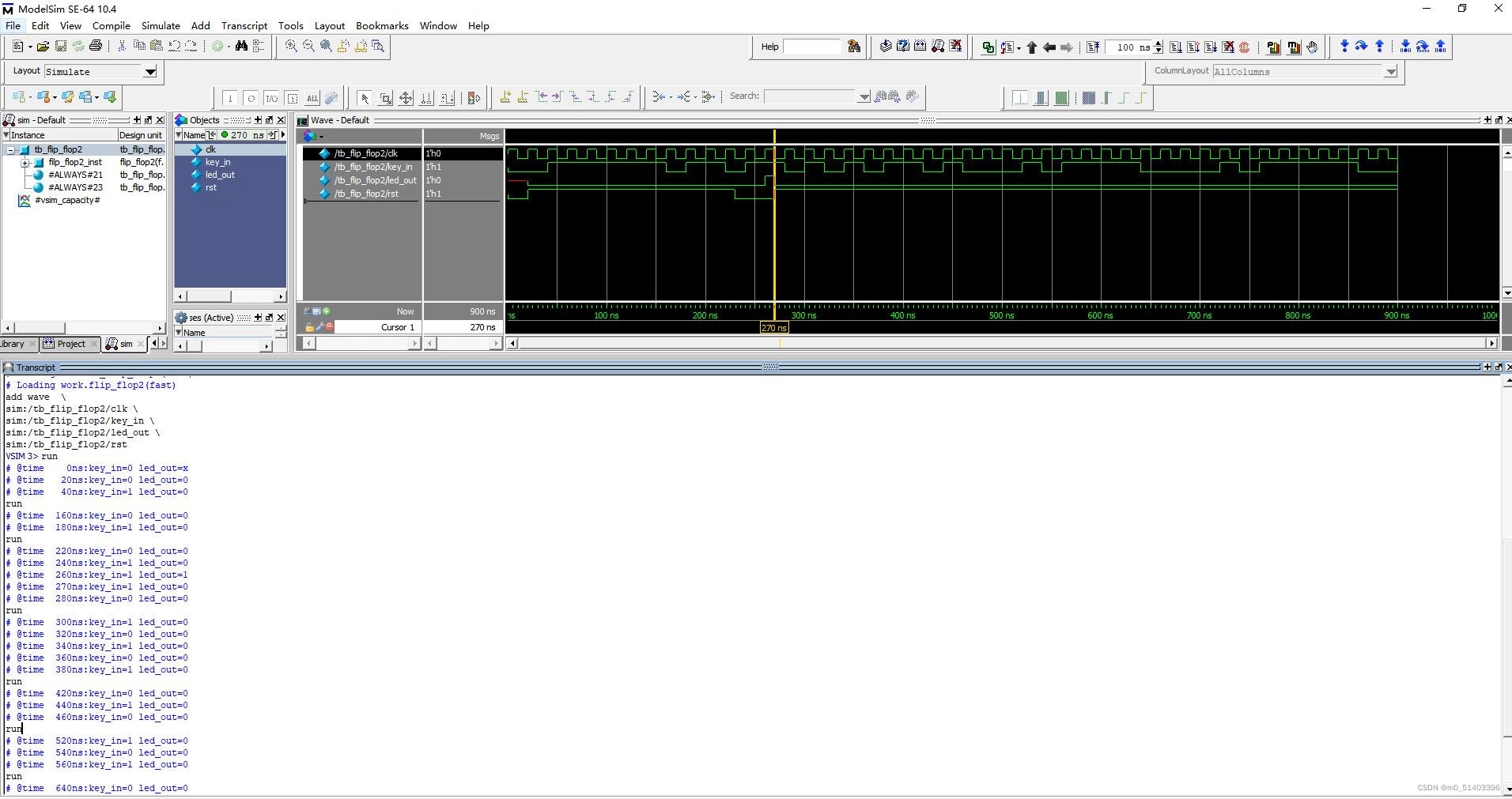

异步复位的测试文件

//tb_flip_flop2.v

module tb_flip_flop2();

reg clk;

reg rst; //复位信号高电平有效

reg key_in;

wire led_out;

initial

begin

clk = 1'b1;

rst <= 1'b0;//先让复位信号无效

key_in <= 1'b0;

#20

rst <= 1'b1;//延时20s后,让复位信号有效

#210

rst <= 1'b0;

#40

rst <= 1'b1;

end

always #10 clk = ~clk;

always #20 key_in <= {$random}%2;

initial

begin

$timeformat(-9,0,"ns",6);

$monitor("@time %t:key_in=%b led_out=%b",$time,key_in,led_out);

end

flip_flop2 filp_flop2_inst(

.clk(clk),

.rst(rst),

.key_in(key_in),

.led_out(led_out)

);

endmodule

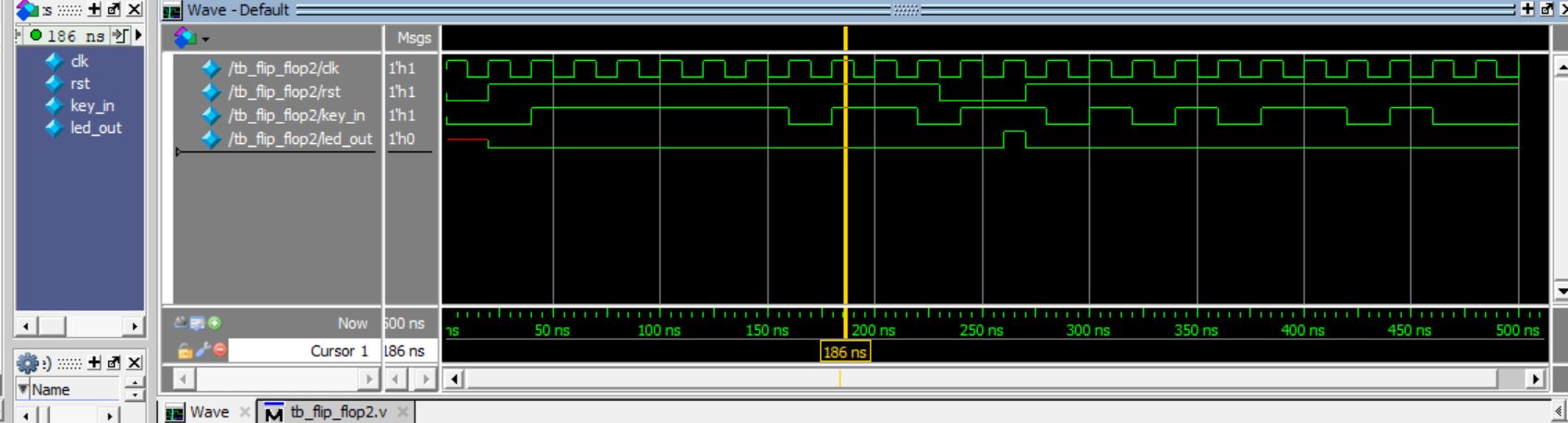

异步复位仿真结果

2022_5_9修改的

最后

以上就是拼搏咖啡最近收集整理的关于【verilog】寄存器概念工作原理代码的全部内容,更多相关【verilog】寄存器概念工作原理代码内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复