一、实验要求:

设计一个具有异步复位功能的32位数据寄存器

思路:利用一个复位信号,当复位为0时将信号复位,当复位信号为1时,把数据储存。

二、代码

其中Q都为0的代码可改为Q<=(OTHERS<=0);

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY REG32 IS

PORT(CLK: IN STD_LOGIC;

NRESET: IN STD_LOGIC;

D: IN STD_LOGIC_VECTOR (31 DOWNTO 0);

Q: OUT STD_LOGIC_VECTOR (31 DOWNTO 0));

END ENTITY REG32;

ARCHITECTURE ART OF REG32 IS

BEGIN

PROCESS(CLK,NRESET,D) IS

BEGIN

IF(CLK'EVENT AND CLK='1') THEN

IF(NRESET='0') THEN

Q<= "00000000000000000000000000000000";

ELSE

Q<=D;

END IF;

END IF;

END PROCESS;

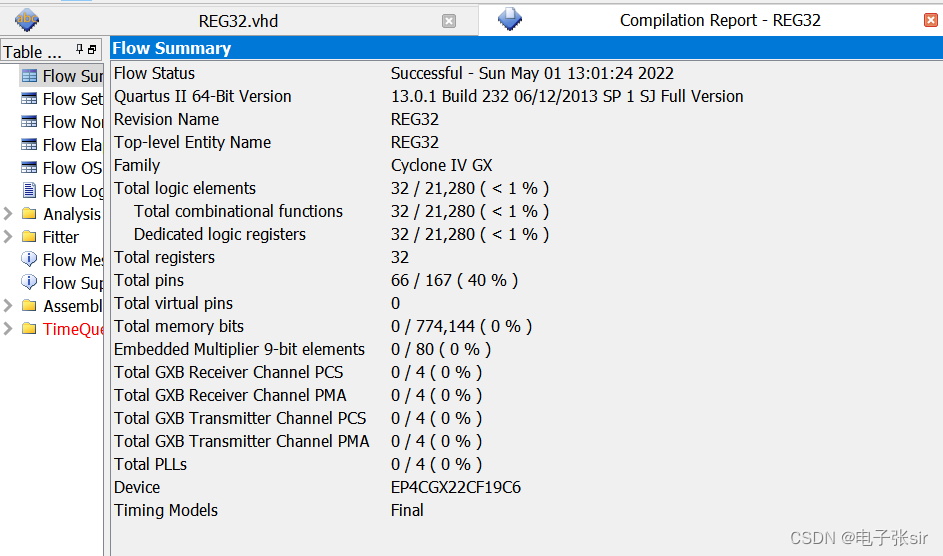

END ARCHITECTURE ART;三、编译结果:

四、代码分析:

IF(CLK'EVENT AND CLK='1') THEN

IF(NRESET='0') THEN

Q<= "00000000000000000000000000000000"; ELSE

Q<=D;

由于实验要求为异步复位,当复位信号为0为有效信号

(若为同步复位则复位信号为1时为有效信号)

利用俩个IF语句完成程序主要功能,当时钟上升沿触发寄存器功能后由复位信号决定是信号复位还是存储!

对于如果要改为其他类似功能的,其中的思想还是一样的,大家可以多去尝试尝试。

最后

以上就是紧张草莓最近收集整理的关于异步复位的32位数据寄存器【VHDL】的全部内容,更多相关异步复位内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复