题目描述

请编写一个十六进制计数器模块,计数器输出信号递增每次到达0,给出指示信号zero,当置位信号set 有效时,将当前输出置为输入的数值set_num。

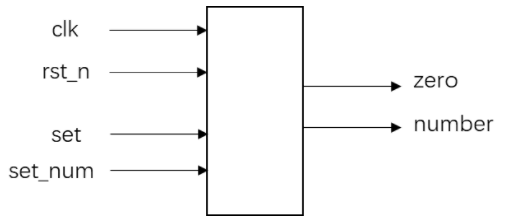

模块的接口信号图如下:

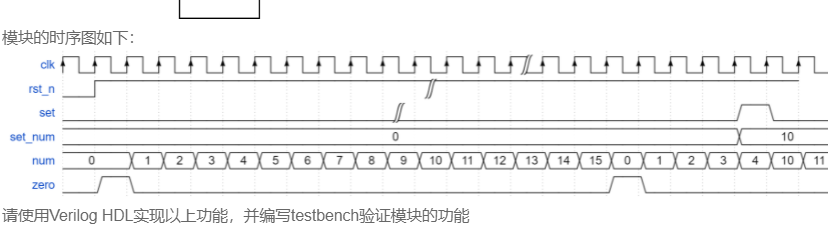

思路:在这个波形图看的不清楚,实际上rst_n置1后num先为0,再变1,一开始没注意这个一直不知道为啥错了。所以输出的number必须有一个周期的时延。

这里用添加一个中间计数器num来延后一个时钟,当num<=num+1时,number <=num,由于always块是并行的,所以此时number赋值时num,非阻塞赋值num<=num+1同步进行,而此时的num=0;

拓展的想,如果再加一个num2<=number,赋值又会延后一个周期。可以通多添加中间变量来增加时延。

(这个方法可以记一下)

剩余的思路就简单了,num=0时zero=1,num从0-15循环。

`timescale 1ns/1ns

module count_module(

input clk,

input rst_n,

input set,

input [3:0] set_num,

output reg [3:0]number,

output reg zero

);

reg [3:0]num;

always @(posedge clk or negedge rst_n)begin

if (!rst_n) zero <= 1'd0;

else if (num == 0) zero <= 1;

else zero <= 1'b0;

end

always @(posedge clk or negedge rst_n) begin

if (!rst_n) num <= 4'b0;

else if(set) num <= set_num;

else num <= num + 1'd1;

end

always @(posedge clk or negedge rst_n) beign

if (!rst_n) number <= 1'd0;

else number <= num;

end

endmodule最后

以上就是乐观小霸王最近收集整理的关于Verilog 每日一题 (VL27 可置位计数器)的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复