Verilog时序电路设计指南

没有时序电路设计准则的RTL设计可能会导致性能低下。本文关键指南包括在顺序设计中使用非阻塞赋值、使用同步复位和时钟选通。详细描述了在设计中使用流水线阶段的指南,这些指南有助于提高设计性能。本文还介绍了有关描述具有多个时钟、多相位时钟的Verilog RTL以及异步复位问题的基本信息。

阻塞赋值的使用

如之前介绍所述,建议使用阻塞赋值来描述组合逻辑设计。但是,如果在编码时序逻辑行为时使用阻塞赋值,会发生什么?这是需要解决的最重要的问题之一,对后续讨论很重要。

如果阻塞赋值用于编码时序逻辑的行为,则可以观察到综合结果不是正确的功能设计意图。

接下来介绍使用阻塞赋值对时序电路设计进行编码的几个设计方案。

阻塞赋值和多个“Always”进程

如例6.1所述,在多个“Always” 进程中使用阻塞赋值。程序块“Always”在时钟的正边缘触发,综合器推断时序逻辑。如前所述,所有阻塞赋值都在活动队列中进行计算和更新。读者请参阅之前分享的分层事件队列一文。

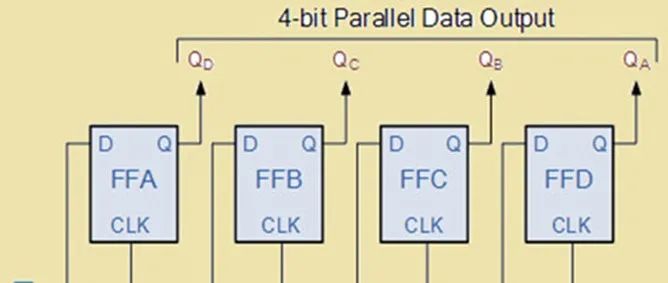

如例6.1所述,这两个“Always” 进程并行执行,并以两位串行输入串行输出移位寄存器的形式生成输出。首先,always进程生成一个输出“b_in”从第一个“Always” 进程生成的输出被另一个“Always” 进程用作输入。因此,综合器将其推断为两位串行输入串行输出移位寄存器。

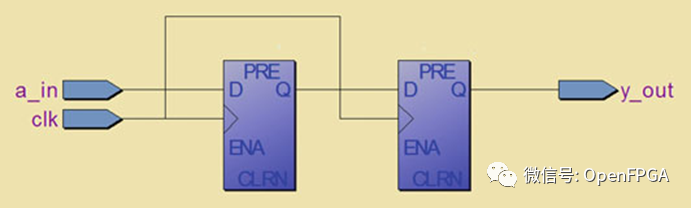

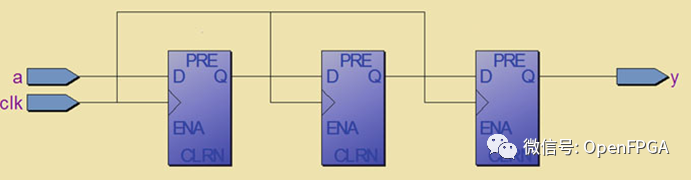

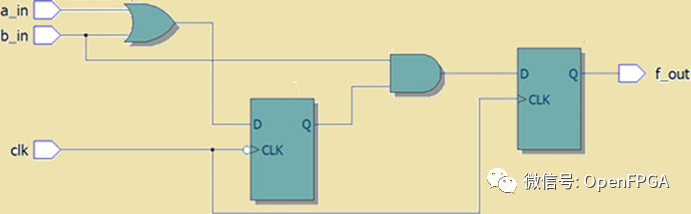

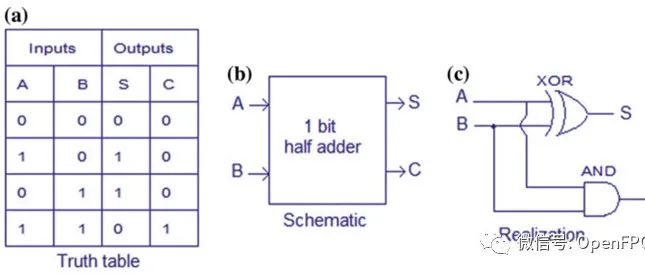

示例6.1的综合逻辑如图6.1所示,并具有输入“a_in”,“clk”和输出“y_out”

例6.1在多个always块中阻塞赋值

例6.1在多个always块中阻塞赋值

图6.1多个always块中阻塞赋值的综合逻辑

图6.1多个always块中阻塞赋值的综合逻辑

同一“always”进程中的阻塞赋值

如果阻塞赋值用于描述时序逻辑,并且在同一“always”程序块中使用多个分配,则预期需求可能与综合逻辑匹配,也可能与综合逻辑不匹配。原因是,在阻塞分配中,所有后续语句(下一个立即数)都被阻塞,除非直到当前语句被执行。这将导致硬件截断,并可能推断出不需要的综合输出。

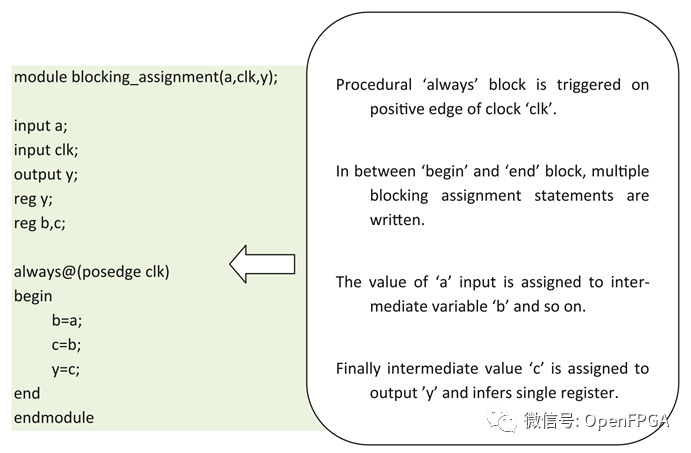

考虑在示例6.2中描述的设计场景,其意图是创建三位串行输入和串行输出移位寄存器,但是在综合示例6.2之后,它推断为单个触发器。

可综合逻辑如图6.2所示,其输入为“a”、“clk”和输出为“y”。所需的功能是串行输入、串行输出移位寄存器,但上述示例由于使用阻塞赋值而推断出单个触发器。因此,建议在为时序功能编码或描述RTL时使用非阻塞赋值。

例6.2在always”进程中的阻塞赋值

例6.2在always”进程中的阻塞赋值

图6.2同一always进程中阻塞赋值的综合逻辑

图6.2同一always进程中阻塞赋值的综合逻辑

阻塞赋值示例

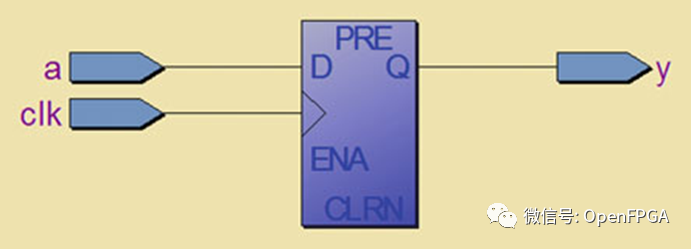

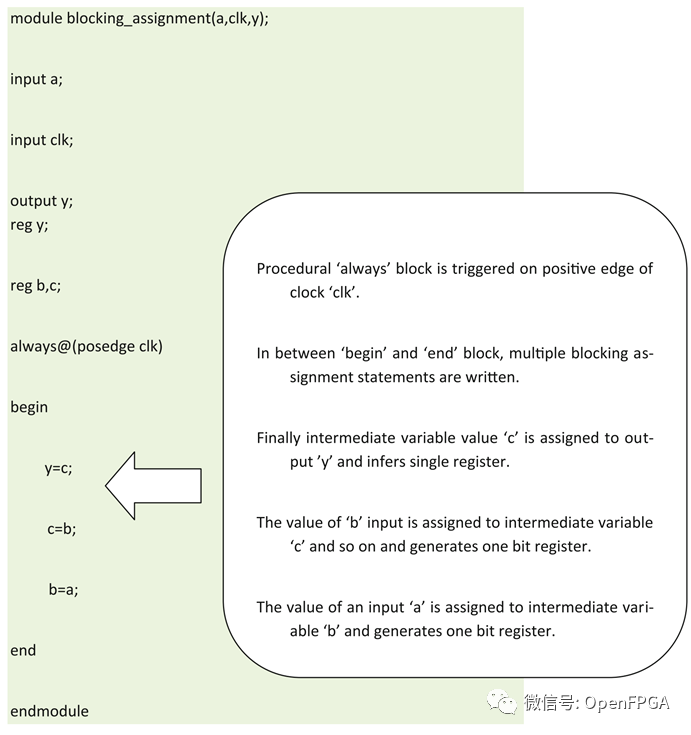

考虑在示例6.3中描述的设计场景,其意图是创建三位串行输入和串行输出移位寄存器,并且由于块“begin” 和 “end”中使用的阻塞赋值语句,它顺序生成三位串行输入串行输出移位寄存器。

综合逻辑如图6.3所示,其输入为“a”、“clk”和输出“y”。所需的功能是串行输入串行输出移位寄存器,它推断串行输入串行输出移位寄存器。因此,需要记住的重要一点是,程序“always”块中的阻塞赋值语句的顺序是综合中的决定性因素。

例6.3同一always块中的阻塞赋值(排序)

例6.3同一always块中的阻塞赋值(排序)

图6.3阻塞赋值重新排序后的可综合逻辑

图6.3阻塞赋值重新排序后的可综合逻辑

非阻塞赋值

如之前介绍的“分层事件队列”一文所述,非阻塞赋值在活动事件队列中评估,并在NBA队列中更新。非阻塞赋值用于描述时序逻辑。这些指定在程序块“always”中使用,以获得所需的综合结果。所有非阻塞赋值在“always”块内并行执行。

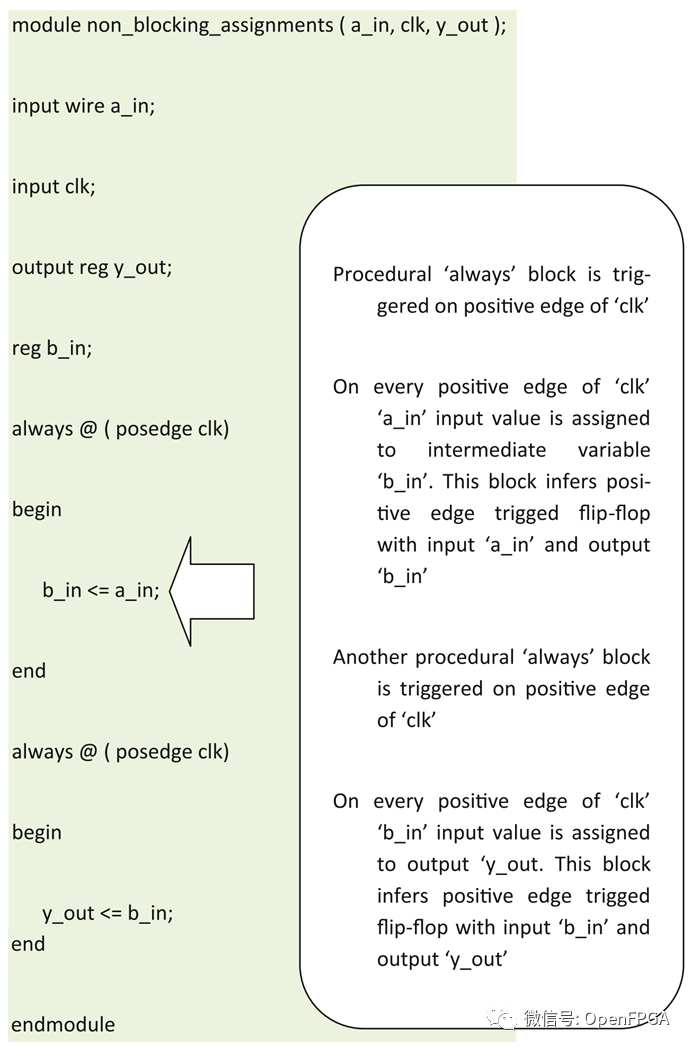

如例6.4所述。非阻塞赋值用于多个“always”块。程序块“always”在时钟的正边沿触发,综合器推断时序逻辑。综合逻辑如图6.4所示。

例6.4不同always块中的非阻塞赋值

例6.4不同always块中的非阻塞赋值

图6.4不同always块中的非阻塞赋值的综合逻辑

图6.4不同always块中的非阻塞赋值的综合逻辑

非阻塞赋值示例

如果使用非阻塞赋值来描述时序逻辑,并且在同一“always”程序块中使用多个赋值,则综合器始终推断出所需的预期逻辑。原因是,在非阻塞赋值中,“begin-end”块中写入的所有语句都是“并行”执行的,这就产生了时序逻辑。

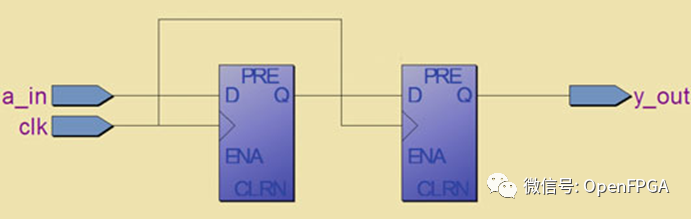

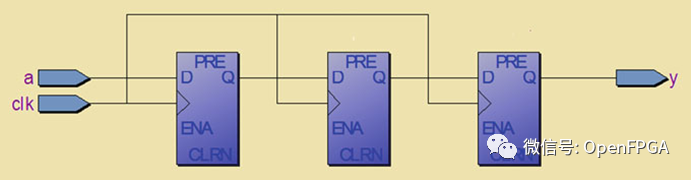

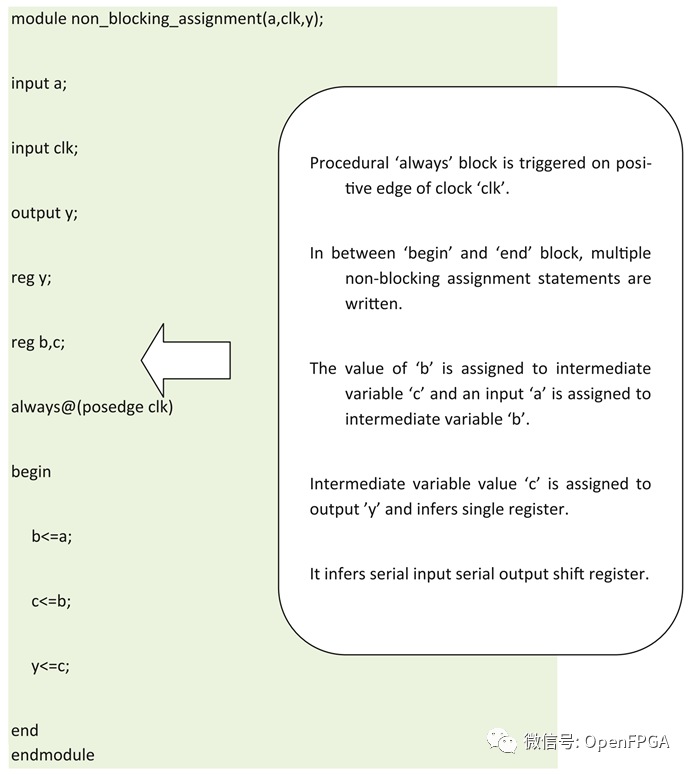

考虑示例6.5中描述的设计场景,意图是创建三位串行输入和串行输出移位寄存器,使用非阻塞赋值。

综合逻辑如图6.5所示,其输入为“a”、“clk”和输出“y”。所需的功能是串行输入串行输出移位寄存器,它推断串行输入串行输出移位寄存器。

例6.5同一always块中的非阻塞赋值

例6.5同一always块中的非阻塞赋值

图6.5同一always块中非阻塞赋值的综合逻辑

图6.5同一always块中非阻塞赋值的综合逻辑

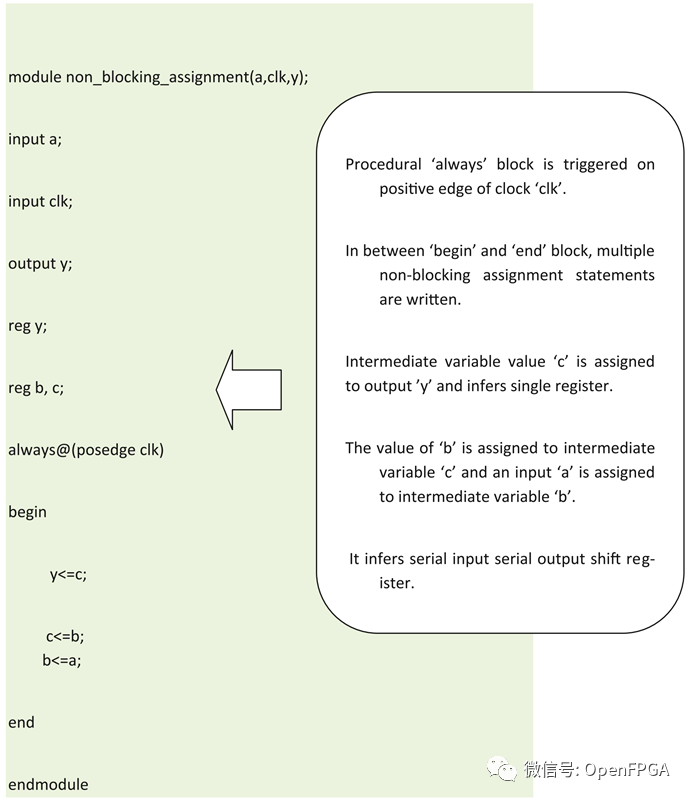

非阻塞赋值的排序

考虑在示例中描述的设计方案,其意图是创建三位串行输入和串行输出移位寄存器,并使用非阻塞赋值。

上一节中的实例,在本例6.6中重新排序。

综合逻辑如图6.5所示,其输入为“a”、“clk”和输出“y”。所需的功能是串行输入串行输出移位寄存器,它推断串行输入串行输出移位寄存器。所以,重要的一点是要记住,过程“always”块中非阻塞赋值语句的顺序不是推断逻辑的决定性因素。

例6.6在同一always块中具有顺序更改的非阻塞赋值

例6.6在同一always块中具有顺序更改的非阻塞赋值

锁存器与触发器

在实际的时序设计中,锁存器和触发器被用作设计所需预期设计功能的元件。锁存器是电平触发的,触发器是边缘触发的。大多数ASIC/FPGA设计都使用触发器作为时序元件。

D触发器

如前所述,触发器是边缘触发的,与锁存器相比,触发器单元的面积更大,甚至对于触发器,由于自由运行时钟的功耗更高,因此需要额外的功率控制逻辑。触发器没有周期窃取或时间借用(the cycle stealing or time borrowing)的概念,操作需要在一个时钟周期内完成。对于基于触发器的设计,应满足建立时间,设计的总体工作频率取决于设计中的关键路径。对于基于触发器的设计,时序分析和时间预算(Timing analysis and time budgeting)应更为明确。

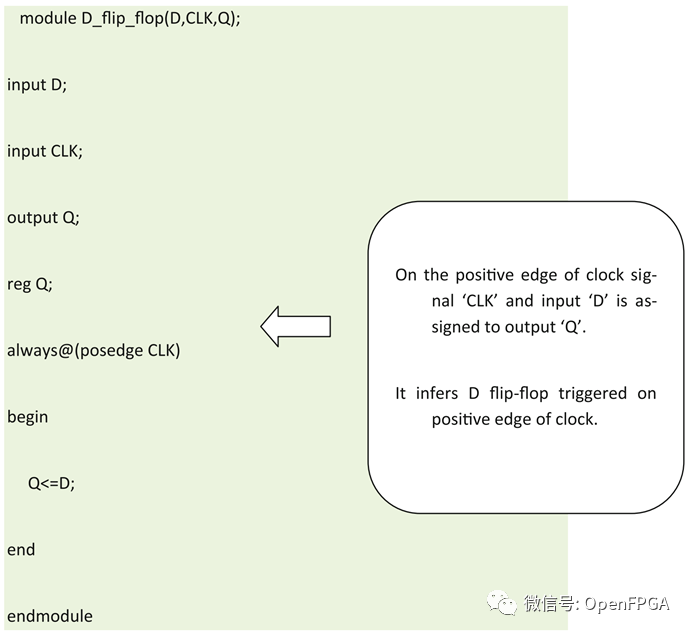

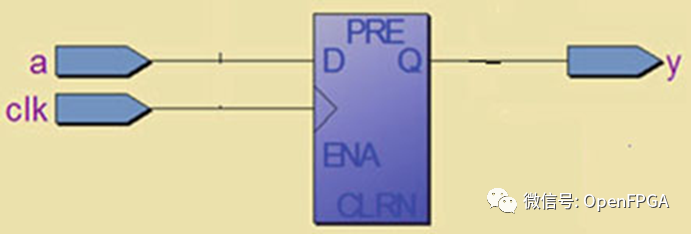

示例6.7中描述了D触发器RTL,并使用非阻塞赋值。输入“D”被分配到时钟正边缘的输出“Q”。

正边缘触发D触发器的综合逻辑如图6.6所示。

例6.7使用非阻塞赋值的D触发器

例6.7使用非阻塞赋值的D触发器

图6.6综合D触发器

图6.6综合D触发器

锁存器

如前所述,锁存器是电平触发的,与触发器相比,锁存器单元的面积更小,对于锁存器,也不需要额外的功率控制逻辑,因为由于锁存器启用输入的低开关导致功耗更小。锁存器具有周期窃取或时间借用的概念,在流水线中非常有用。不需要在一个时钟周期内完成操作。基于锁存器的设计,设计的总体工作频率不取决于设计中最慢的路径。对于基于锁存器的设计,时序分析和时间预算更为困难。

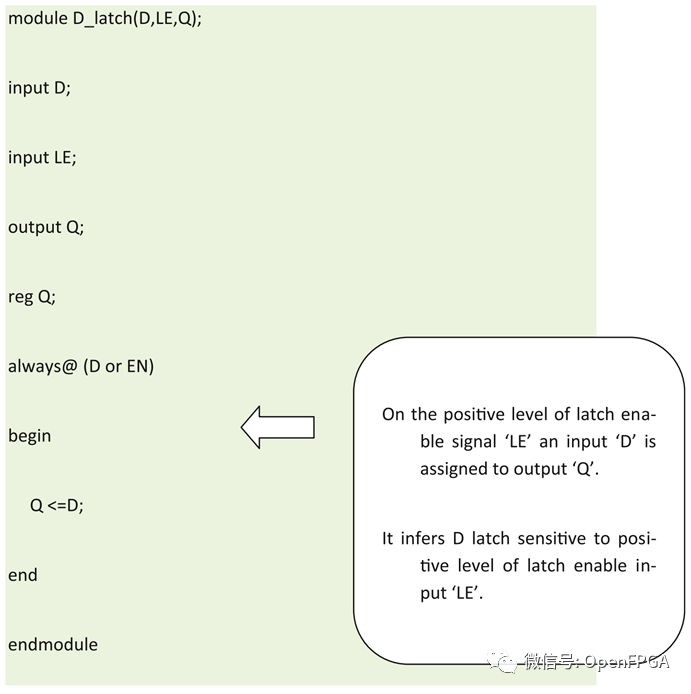

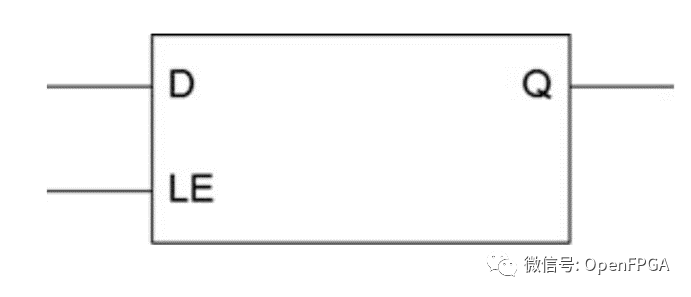

示例6.8中描述了D锁存器RTL,并使用非阻塞赋值。在锁存启用输入的正电平上,输入“D”被分配给输出“Q”。

正电平敏感锁存器的综合逻辑如图6.7所示。

图6.7综合锁存器

图6.7综合锁存器

同步与异步复位的使用

大多数情况下,设计工程师在使用复位时会感到困惑!对于我们来说,何时进行异步复位以及何时使用同步复位是工程师面临的关键挑战之一。因此,对于ASIC/FPGA设计工程师来说,需要很好地理解复位问题以及复位树。复位树结构和同步将在后面讨论。本节介绍使用Verilog HDL的同步和异步复位描述。

异步复位D触发器

如前面文章所述,异步复位是ASIC /FPGA设计中的一个问题,因为它独立于时钟信号。复位信号用于在任何时间点初始化时序逻辑,与时钟无关。复位输入不是数据路径的一部分,甚至内部生成的复位或异步复位也不建议在ASIC/FPGA设计中使用,因为它们容易出现故障。即使复位恢复也是一个问题,如果使用异步复位输入,则建议使用两级同步器同步异步复位输入。

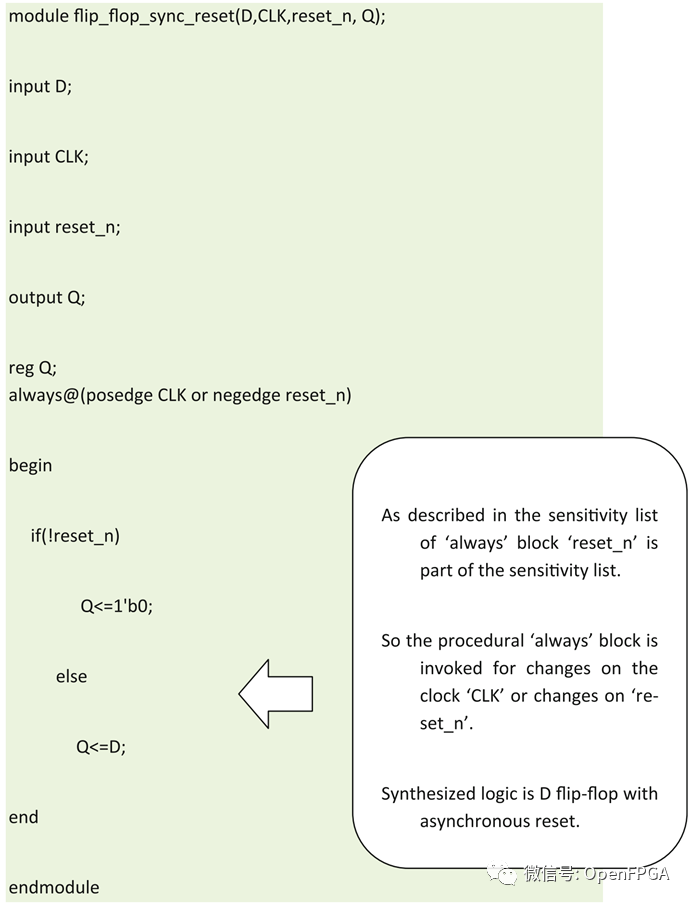

如例6.9所示,使用Verilog HDL描述异步复位信号D触发器RTL。

异步复位D触发器的综合逻辑如图6.8所示。

例6.9用于异步复位D触发器的Verilog RTL

例6.9用于异步复位D触发器的Verilog RTL

图6.8异步复位D触发器的综合

图6.8异步复位D触发器的综合

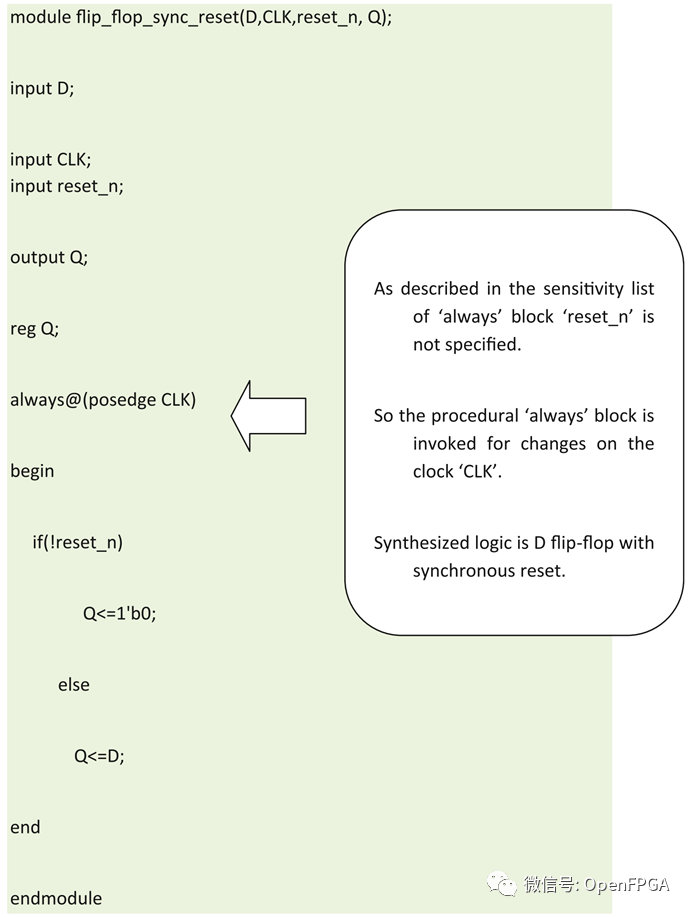

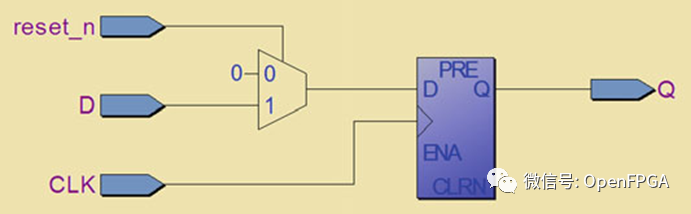

同步复位D触发器

如之前所述,在ASIC/FPGA设计中,同步复位与依赖于时钟信号。复位信号用于在时钟正边缘上的实例初始化时序逻辑。复位输入是数据路径的一部分,不容易出现故障。使用同步复位输入,复位恢复就不是问题。同步复位不需要使用电平同步器。

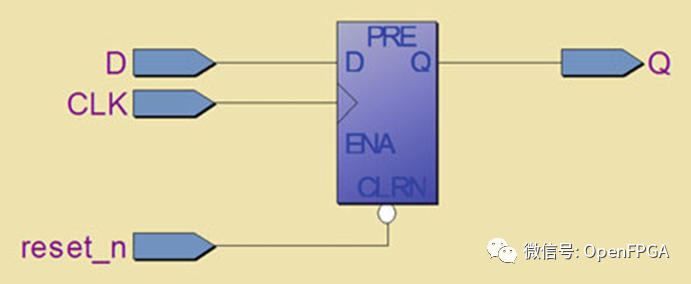

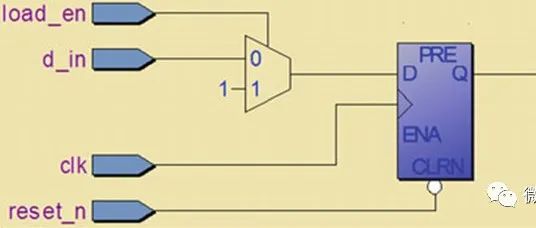

如例6.10所示,使用Verilog HDL描述同步复位信号D触发器RTL。

综合逻辑如图6.9所示,其中复位输入是数据路径的一部分。

例6.10同步复位D触发器的Verilog RTL

例6.10同步复位D触发器的Verilog RTL

图6.9同步复位综合D触发器

图6.9同步复位综合D触发器

使用if-else与案例分析

对于时序设计,使用“if-else”结构来描述优先级逻辑功能。要分配优先级信号,请使用“if-else”结构。使用“case”结构来描述并行逻辑。后续会进行详细介绍,这里先不介绍了。

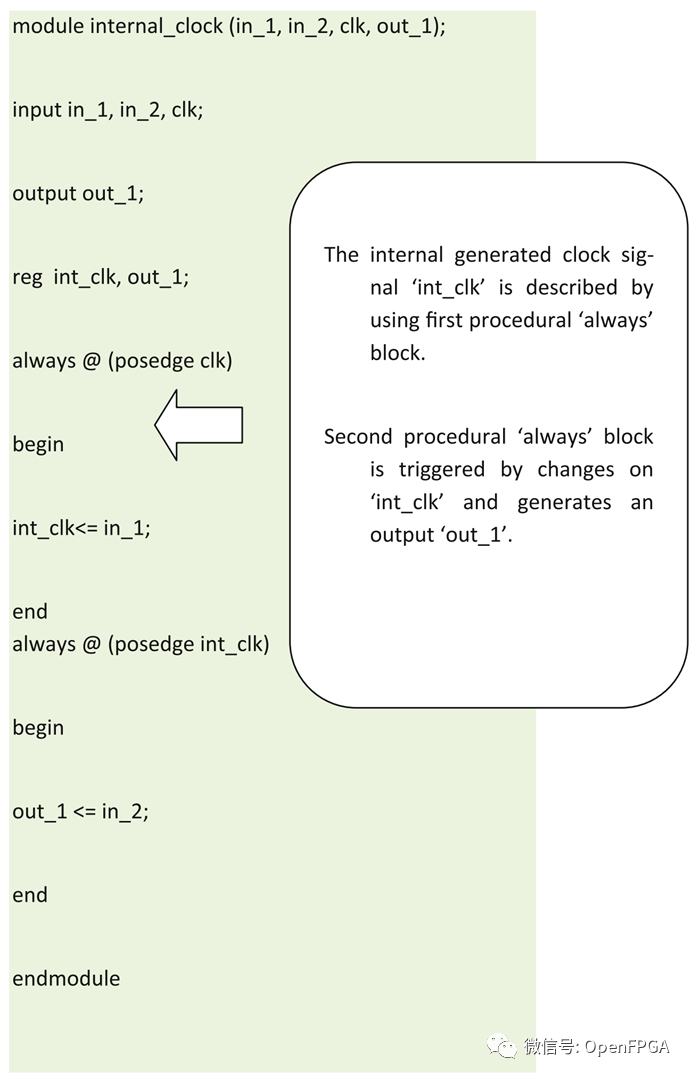

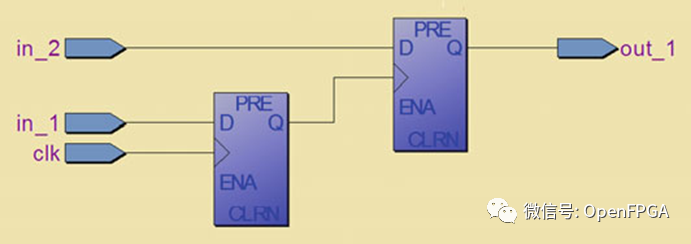

内部生成的时钟

内部生成的时钟信号使用系统或主时钟,并生成输出作为内部生成的时钟信号。但是,需要避免内部生成的时钟信号,因为它会导致设计中的功能和时序问题,功能和时序问题是由组合逻辑传播延迟引起的。内部产生的时钟信号会在系统中产生小故障或尖峰(glitch or spike)输出,这可能会多次触发时序逻辑,或产生不需要的输出。这不仅违反建立或保持时间,这些类型的设计也会违反计时规则。

始终建议使用寄存器输出逻辑生成内部时钟。但是仍然由于触发器的传播延迟,总体累积延迟或偏差可能会在设计中产生小故障或尖峰。

如例6.11所示,描述了Verilog RTL生成内部时钟。生成的内部时钟信号由其他时序程序块使用。

例6.11用于内部生成时钟的Verilog RTL

例6.11用于内部生成时钟的Verilog RTL

图6.10综合内部生成时钟逻辑

图6.10综合内部生成时钟逻辑

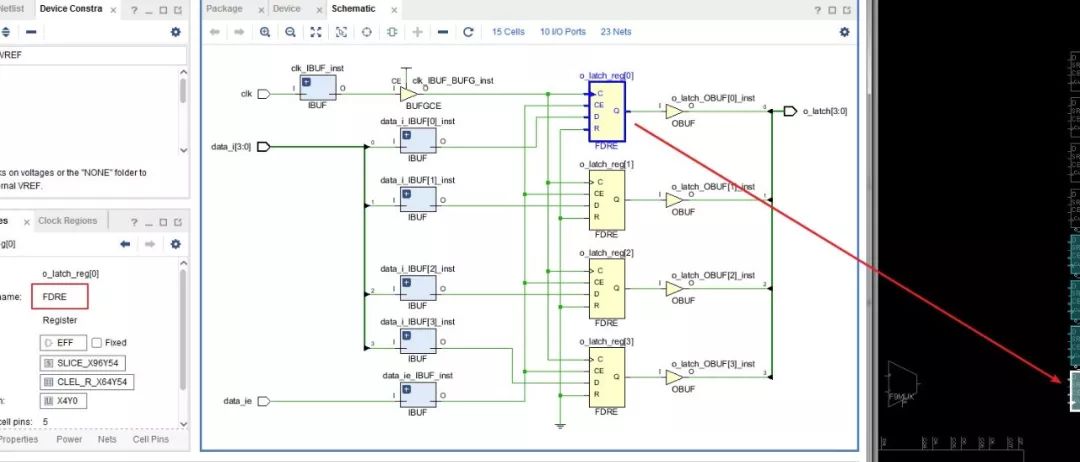

综合逻辑如图6.10所示,第一个寄存器由时钟“clk”驱动,第二个寄存器由“int_clk”驱动。

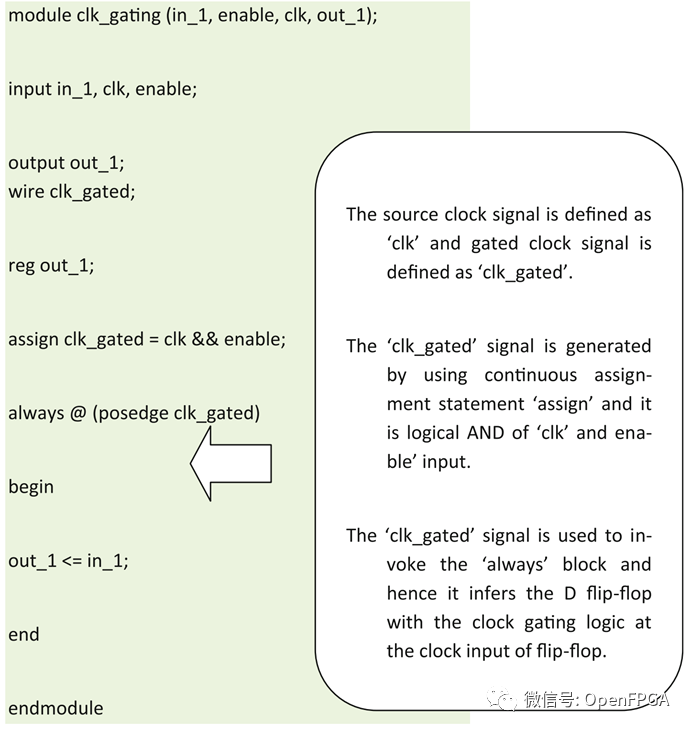

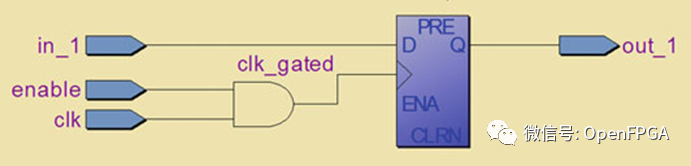

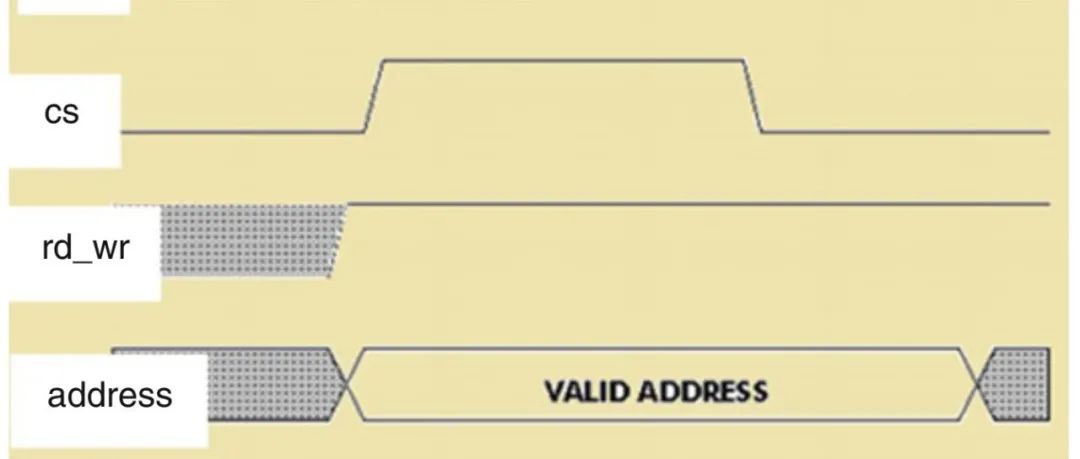

门控时钟

门控时钟信号用于在时钟输入端使能切换,并可通过使用使能输入端在单个或多个时钟域设计中使用。使能输入为高时,时钟域打开;使能输入为低时,时钟域关闭。需要时钟选通逻辑来控制时钟的开启或关闭。时钟选通是ASIC/FPGA设计中用来降低寄存器时钟输入端开关功率的一种有效技术。通过使用时钟选通结构,可以根据设计功能要求在需要时停止时钟切换。

但是时钟选通的问题是它不能用于同步设计,原因是它引入了大量的时钟偏移,甚至这种技术也引入了小故障。为了避免出现故障,ASIC/FPGA设计工程师需要特别小心。

例6.12中描述了Verilog RTL,并使用使能输入控制时钟切换活动。对于“enable=1”,时钟输入“clk”切换,对于“enable=0”,时钟输入无切换。

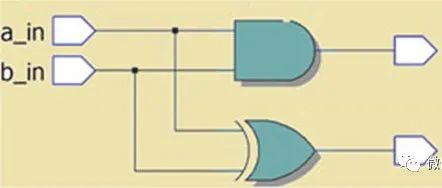

综合逻辑如图6.11所示,其中使用AND逻辑对时钟进行选通。

图6.11综合时钟选通逻辑

图6.11综合时钟选通逻辑

设计中“流水线”的使用

流水线是以延迟为代价提高设计性能的强大技术之一。这种技术被用于许多处理器设计和许多ASIC/FPGA设计应用程序中,以便一次并行执行多个任务。本节讨论无流水线设计和有流水线设计。

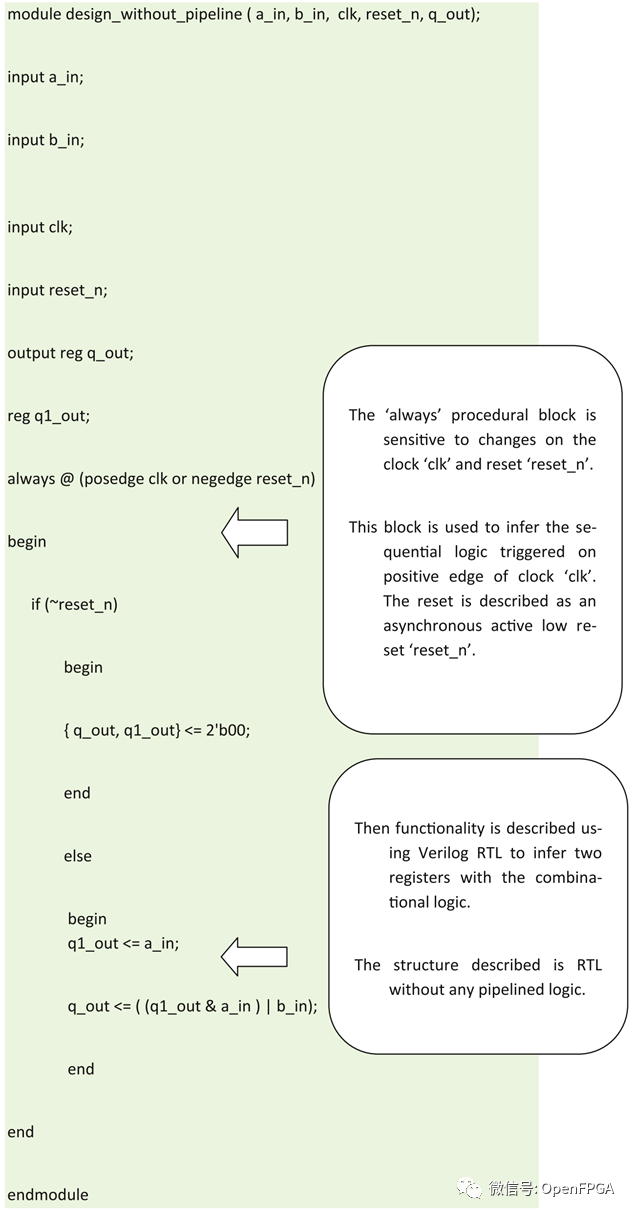

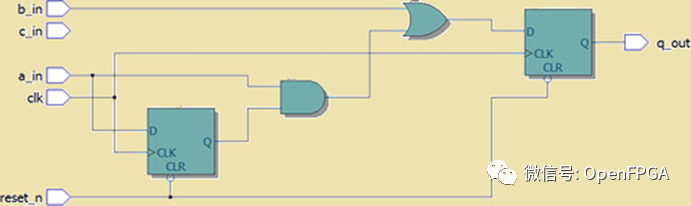

无流水线的设计

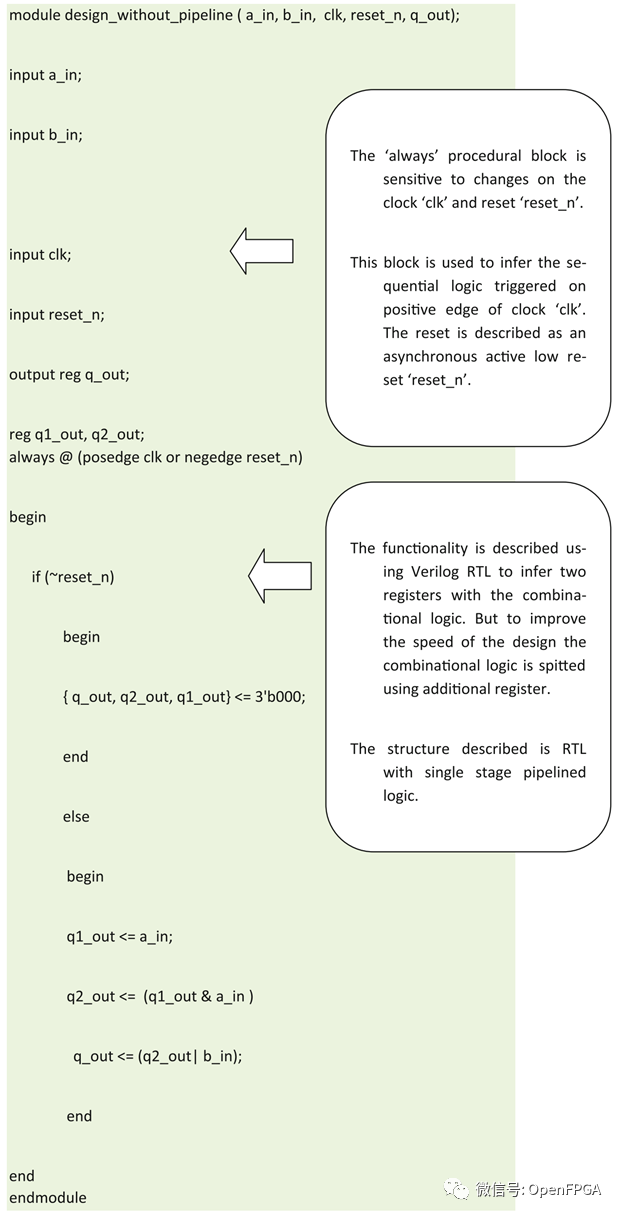

在设计的初始阶段,大多数设计都是使用Verilog RTL描述的,而不使用流水线逻辑。如果没有达到设计性能所需的速度,那么ASIC/FPGA设计者可以使用各种方法达到自己的目的。最好的方法之一是通过根据时钟延迟和数据速率要求插入寄存器逻辑进行流水线。示例6.13描述了在不使用任何流水线逻辑的情况下使用Verilog RTL的设计功能。

综合RTL逻辑如图6.12所示,由公共时钟源“clk”触发的两个寄存器组成。

例6.13无流水线级的Verilog RTL

例6.13无流水线级的Verilog RTL

图6.12无流水线级的综合逻辑

图6.12无流水线级的综合逻辑

流水线设计

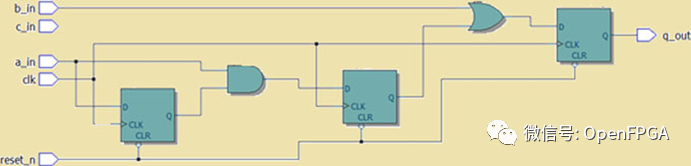

为了提高设计性能,可以将组合逻辑和输出提供给附加的流水线寄存器,流水线寄存器的输出可以驱动或逻辑的一个输入。

这种技术将以一次时钟延迟为代价来提高设计的整体性能。设计性能的提高是由于寄存器到寄存器路径中组合延迟的减少。

例6.14中描述了Verilog RTL,通过添加额外的寄存器逻辑,实现了流水线。

综合RTL逻辑如图6.13所示,由公共时钟源“clk”触发的三个寄存器组成。

例6.14带流水线级的Verilog-RTL

例6.14带流水线级的Verilog-RTL

图6.13流水线级综合逻辑

图6.13流水线级综合逻辑

同步设计建模指南

以下是用于描述同步设计的关键指南

要描述同步设计的功能,请使用非阻塞赋值。

请勿使用基于锁存器的设计,因为锁存器在半个时钟周期内是透明的。

使用流水线提高设计性能。

使用同步复位信号,因为它们不容易出现故障或尖峰。

如果使用异步信号,则使用双级同步器同步内部生成的复位。

使用时钟选通单元(门控时钟)进行低功耗设计。

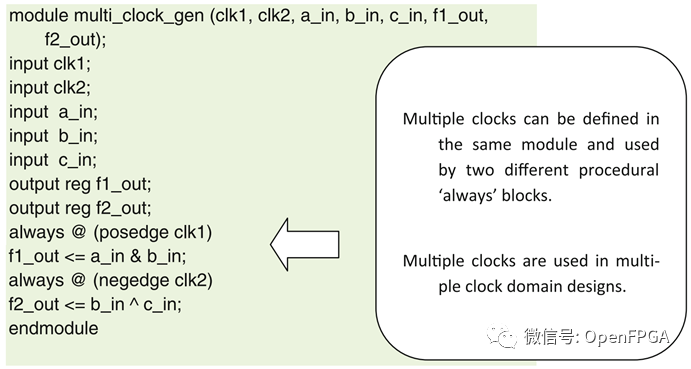

同一模块中的多个时钟

在多时钟域设计中可以使用多个时钟源或信号。这些时钟信号可以通过使用不同的源来生成,并且可以在ASIC/FPGA设计中用于触发不同的“always”程序块。数据从一个时钟域到另一个时钟域的传输需要数据路径和控制路径中的额外同步器,这些将在后续文章中讨论。

例6.15中描述了Verilog RTL,它使用两个不同的时钟信号“clk1”和“clk2”。使用两个不同的程序块分别使用“clk1”和“clk2”来描述功能y。在同一模块中定义多个时钟信号不是最佳做法。在多时钟域设计中,根据功能需求需要描述不同的设计块,并且可以在不同的时钟信号上触发它们。

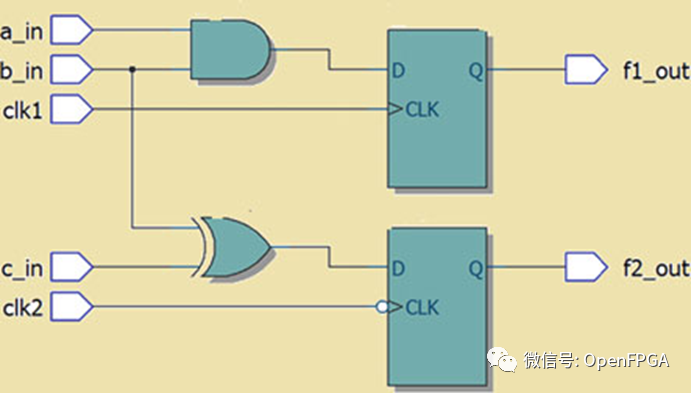

综合输出如图6.14所示,并生成输出“f1_out”和“f2_out”。时钟信号“clk1”用于触发上层寄存器。上层寄存器在时钟“clk1”的正边缘触发。下层寄存器在“clk2”的负边缘触发。

例6.15用于多时钟定义的Verilog RTL

例6.15用于多时钟定义的Verilog RTL

图6.14多时钟综合逻辑

图6.14多时钟综合逻辑

设计中的多相位时钟

用于触发多个程序块并从同一时钟源生成且具有到达时间差的时钟信号称为多相位时钟信号。例如,如果其中一个程序块在时钟的正边缘触发,而另一个程序块在时钟的负边缘触发,则寄存器和这些信号的触发中存在180°的相位差,并被视为相移信号。

Verilog RTL如例6.15所示,其中一个程序块由时钟的正边缘触发,另一个由时钟的负边缘触发(例6.16)。

综合逻辑如图6.15所示,其中在时钟的不同边缘触发两个不同的寄存器。

例6.16带多相时钟的Verilog-RTL

例6.16带多相时钟的Verilog-RTL

图6.15多相位时钟的综合逻辑

图6.15多相位时钟的综合逻辑

异步设计建模指南

以下是异步设计建模时需要遵循的关键准则

如果使用异步复位信号,则使用双边缘同步器同步内部生成的复位信号。

避免使用将触发器输出驱动到后续触发器的异步复位,因为这可能具有竞争条件。

避免使用异步脉冲发生器,因为它会在设计和定时关闭过程中,甚至在place和route过程中产生问题。

如果以功耗为目标,则仅使用高效纹波计数器;但是,由于触发器的累积延迟效应或级联延迟(由于触发器的个别传播延迟),在使用纹波计数器时会出现性能下降。

你真的理解Verilog 中的module吗?

工具与大脑完美结合,才能写出世上最棒的Verilog代码

数字硬件建模综述

数字硬件建模-从另一方面理解Verilog(一)

数字硬件建模-重新从另一方面理解Verilog(二)

组合逻辑硬件建模设计(一)逻辑门

FPGA的设计中为什么避免使用锁存器

组合逻辑硬件建模设计(二)算术电路

Verilog组合逻辑设计指南

Verilog时序逻辑硬件建模设计(一)锁存器D-latch和触发器Flip-Flop

Verilog时序逻辑硬件建模设计(二)同步和异步复位

Verilog时序逻辑硬件建模设计(三)同步计数器

Verilog时序逻辑硬件建模设计(四)移位寄存器

Verilog时序逻辑硬件建模设计(五)异步计数器&总结

最后

以上就是直率饼干最近收集整理的关于Verilog时序电路设计指南Verilog时序电路设计指南阻塞赋值的使用非阻塞赋值锁存器与触发器同步与异步复位的使用使用if-else与案例分析内部生成的时钟门控时钟设计中“流水线”的使用同步设计建模指南同一模块中的多个时钟设计中的多相位时钟异步设计建模指南的全部内容,更多相关Verilog时序电路设计指南Verilog时序电路设计指南阻塞赋值内容请搜索靠谱客的其他文章。

发表评论 取消回复