连续@posedge是可以综合,如果后面是阻塞赋值,会出现以下现象:

这部分是源码中的执行部分:

@(posedge clk) b = a;

@(posedge clk) c = b;

$display("blocking2 a = %b b = %b c = %b",a,b,c);

@(posedge clk)

begin

c = b;

b = a;

$display("blocking1 a = %b b = %b c = %b",a,b,c);

end这部分是测试代码的主体:

initial

begin

clk = 1'b1;

a = 4'b0;

sel = 2'b0;

repeat(15)

begin

#6

sel = sel + 2'b1;

a = 4'd0;

#6

a = 4'd6;

end

end

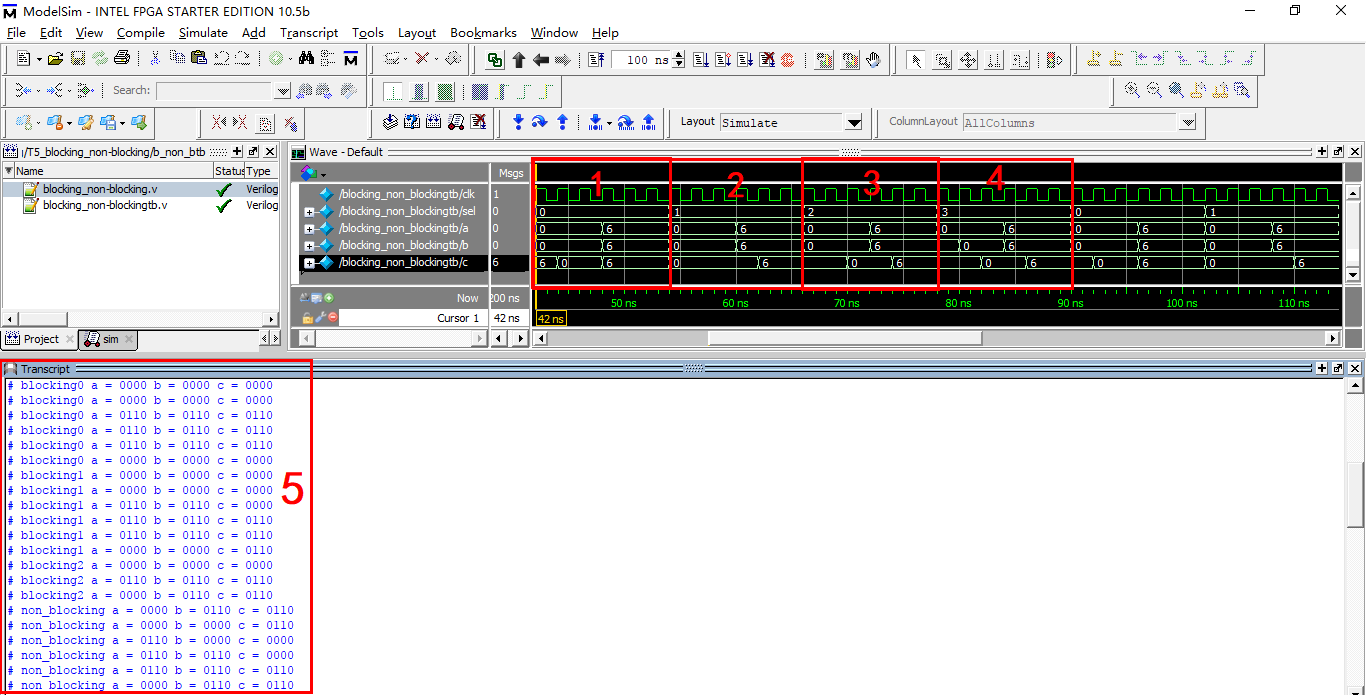

always #1 clk = ~clk;现象如下:

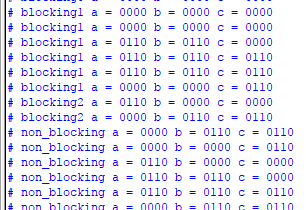

可以看到,其他的单个@posedge的都是输出6次,两个@posedge连着用,后面又跟的是阻塞赋值,就导致本来该出现6次的$display只出现了6/2次,更改位三连@就只剩6/3 = 2次了。是由于第一次阻塞赋值必须完成之后才能出第一个@,这时候边沿已经过去了,然后还得接着等第二个边沿,就在第二个@处等着,所以对于 $display,就错过了一个沿,所以就少了半,两个轮回就是三次。

那如果是三个@posedge是不是就应该只显示两次了呢,是的:

@(posedge clk) b = a;

@(posedge clk) c = b;

@(posedge clk) $display("blocking2 a = %b b = %b c = %b",a,b,c);

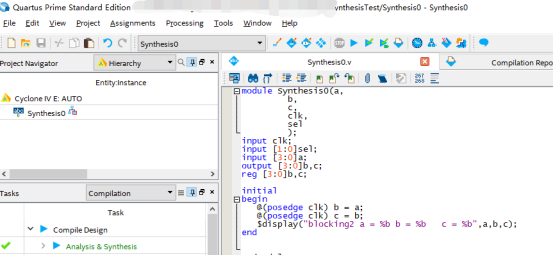

但是这种写法是可以综合的吗?我们验证一下:

的确是可综合的。

最后

以上就是机灵大象最近收集整理的关于Verilog中使用连续@posedge会是什么现象,是否可综合的全部内容,更多相关Verilog中使用连续@posedge会是什么现象内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复