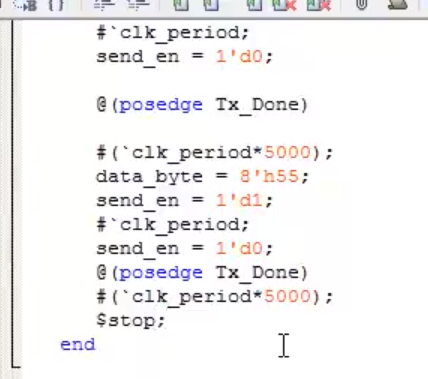

之前看小梅哥视频,对下面语句有所疑惑:

不知道这个@(posedge)触发后只执行一句还是后面的都执行,能不能加begin end只触发某几句;如果能用begin end的话,没有触发上升沿那么这个语句会不会阻塞后面的语句,自己就写了个testbench,代码如下:

`timescale 1ns/1ns

`define tm 20

module tb();

reg clk;

reg test1;

reg test2;

reg test3;

reg clk1;

initial clk = 1'b0;

always#(`tm/2) clk = ~clk;

initial begin

test1 = 1'b0;

test2 = 1'b0;

test3 = 1'b0;

clk1 = 1'b0;

#(`tm*3);

@(posedge clk)begin

test1 = 1'b1;

test2 = 1'b1;

end

#(`tm*3);

@(posedge clk1)begin

test3 = 1'b1;

end

#(`tm*3);

test1 = 1'b0;

test2 = 1'b0;

test3 = 1'b0;

@(posedge clk)begin

test1 = 1'b1;

end

#(`tm*10);

$stop;

end

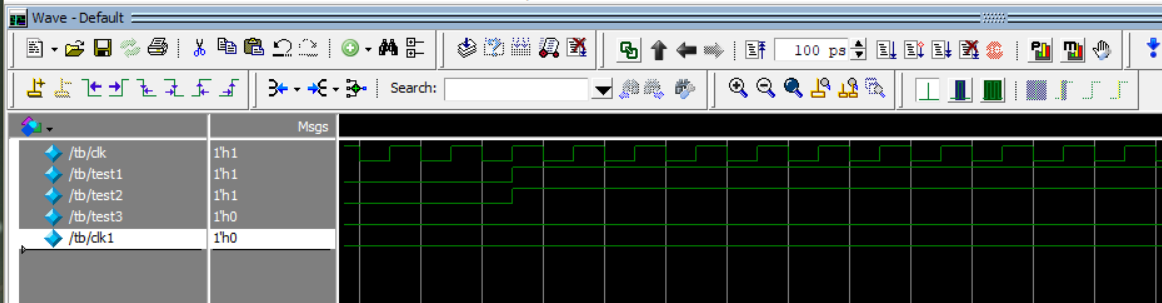

endmodule 波形结果:

结论是会阻塞,@(posedge clk)语句其实等同于wait。

最后

以上就是仁爱万宝路最近收集整理的关于FPGA学习笔记:单次调用@(posedge clk)(没有always)的全部内容,更多相关FPGA学习笔记:单次调用@(posedge内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复