转自:qinfengxiaoyue的百度空间

加法器逻辑结构的改进

1.全加器(加法单元)

加法单元是一个三端输入,两端输出的加法网络

·串行加法器和并行加法器

串行加法器:只设一个全加器称串行加法器

典型的串行加法器只用一位全加器,由移位寄存器从低位到高位串行地提供操作数进行相加

并行加法器:让各位数据同时相加,就产生了并行加法器

并行加法器解决了同时对数的各位相加,减少了本身求和延迟。但是。低位向高位产生的进位却姗姗来迟。

·进位链

通常我们将各位之间传递进位信号的逻辑连接构成的进位线路称进位链

(1)串行进位方式:每一级进位直接依赖于前一级的进位

(2)并行进位方式:从数学的角度去掉数据的相关项

(3) 分组并行进位方式:并行进位方式逻辑表达式没有问题,但是会使得硬件电路结构变得十分复杂,而且受到元器件前入系数的限制,使得完全采用并行方式变得不现实。所以进行分组并行进位方式,具体做法如下:设加法器字长16位,每4位为一组,则可将进位链分成两级,第一级在小组内采用并行进位链,第二级在小组间并行进位链

串行加法器和并行加法器

加法器是算术逻辑单元的重要组成部分,它是一种用于加法运算的器件,其本身主要由全加器再配以其他必要的逻辑电路组成,根据组成加法器的全加器个数,可以将加法器分为串行加法器和并行加法器。

1.串行加法器

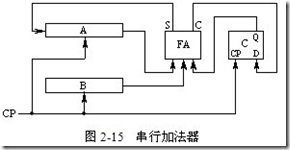

在串行加法器中,只有一个全加器,数据逐位串行送入加法器进行运算,如图2-15所示。图中FA是全加器,A、B是两个具有右移功能的寄存器,C为进位触发器。由移位寄存器从低位到高位逐位串行提供操作数相加。如果操作数长n位,加法就要分n次进行,每次产生一位和,并串行地送回A寄存器。进位触发器用来寄存进位信号,以便参与下一次的运算。

串行加法器具有器件少、成本低的优点,但运算速度太慢,所以除去某些低速的专用运算器外很少采用。

2.并行加法器

并行加法器由多个全加器组成,其全加器个数的多少取决于机器的字长,由于并行加法器可同时对数据的各位相加,读者可能会认为数据的各位能同时运算,其实并不是这样的。这是因为虽然操作数的各位是同时提供的,但低位运算所产生的进位会影响高位的运算结果。例如:11…11和00…01相加,最低位产生的进位将逐位影响至最高位,因此,并行加法器需要一个最长运算时间,它主要是由进位信号的传递时间决定的,而每个全加器本身的求和延迟只是次要因素。很明显,提高并行加法器速度的关键是尽量加快进位产生和传递的速度。

并行加法器中的每一个全加器都有一个从低位送来的进位输入和一个传送给高位的进位输出。通常将传递进位信号的逻辑线路连接起来构成的进位网络称为进位链。每一位的进位表达式为:

Ci=AiBi+(Ai⊕Bi)Ci-1

其中,“AiBi”取决于本位参加运算的两个数,而与低位进位无关,因此称AiBi为进位产生函数(本次进位产生),用Gi表示,其含义是:若本位的两个输入均为1,必然要向高位产生进位。“(Ai⊕Bi)Ci-1”则不但与本位的两个数有关,还依赖于低位送来的进位,因此称Ai⊕Bi为进位传递函数(低位进位传递),用Pi表示,其含义是:当两个输入中有一个为1,低位传来的进位Ci-1将向更高位传送,所以进位表达式又可以写成:

Ci=Gi+PiCi-1

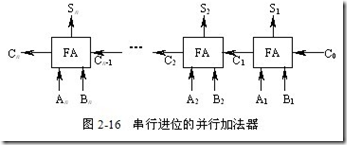

把n个全加器串接起来,就可进行两个n位数的相加。这种加法器称为串行进位的并行加法器,如图2-16所示。串行进位又称行波进位,每一级进位直接依赖于前一级的进位,即进位信号是逐级形成的。

其中:C1=G1+P1C0

C2=G2+P2C1

…

Cn=Gn+PnCn-1

串行进位的并行加法器的总延迟时间与字长成正比,字长越长,总延迟时间就越长。假设将一级与门、或门的延迟时间定为ty,从上述公式中可以看出,每一级全加器的进位延迟时间为2ty。在字长为n位的情况下,若不考虑Gi、Pi的形成时间,从C0→Cn的最长延迟时间为2nty(设C0为加法器最低位的进位输入,Cn为加法器最高位的进位输出)。

显然,串行进位方式的进位延迟时间太长了,要提高加法运算的速度,就要尽可能地减少进位延迟时间,也就是要改进进位方式,这就产生了并行进位方式和分组并行进位方式。限于篇幅,本书不详细介绍这两种方式的具体内容。

算术逻辑单元的功能和结构

ALU是既能完成算术运算又能完成逻辑运算的部件。由于无论是加、减、乘、除运算,最终都能归结为加法运算。因此,ALU的核心首先应当是一个并行加法器,同时也能执行像与、或、非、异或这样的逻辑运算。由于ALU能完成多种功能,所以ALU又称为多功能函数发生器。

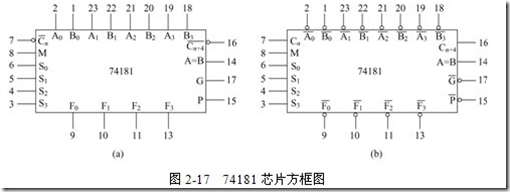

最简单的ALU是4位的,目前,随着集成电路技术的发展,多位的ALU已相继问世。为了说明原理,仍以典型的4位ALU芯片(74181)为例介绍ALU的结构及应用。

74181能执行16种算术运算和16种逻辑运算。工作于正逻辑或负逻辑的74181的框图分别如图2-17(a)、(b)所示。以负逻辑为例,其中:

是两个操作数,

是两个操作数,  为输出结果;Cn表示最低位的外来进位,Cn+4是向高位的进位; 为组进位产生函数输出, 为组进位传递函数输出;M表示工作方式(M=0为算术操作,M=1为逻辑操作),S3~S0为功能选择线。

为输出结果;Cn表示最低位的外来进位,Cn+4是向高位的进位; 为组进位产生函数输出, 为组进位传递函数输出;M表示工作方式(M=0为算术操作,M=1为逻辑操作),S3~S0为功能选择线。

转载于:https://www.cnblogs.com/shenerguang/archive/2012/07/10/2585074.html

最后

以上就是伶俐可乐最近收集整理的关于[转] 串、并行加法器的全部内容,更多相关[转]内容请搜索靠谱客的其他文章。

![[转] 串、并行加法器](https://www.shuijiaxian.com/files_image/reation/bcimg11.png)

发表评论 取消回复