文章目录

- 串行加法器

- 全加器真值表

- 补码加法运算

- 串行全加器图

- 表达式

- 并行加法器

- 表达式

- 并行加法器

- 并行加法器逻辑电路图

- CLA加法器

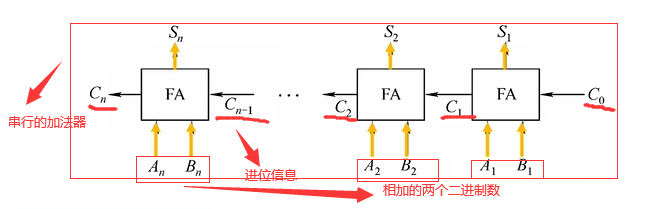

串行加法器

- FA指的是加法器

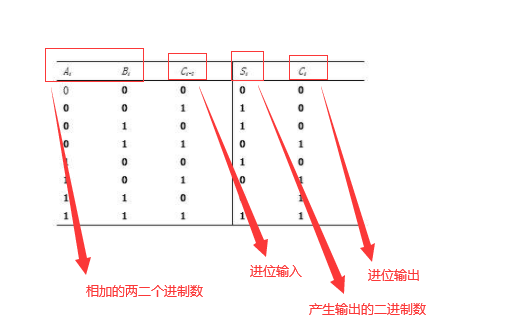

全加器真值表

Si = AI ⊕ Bi (⊕ 代表异或运算)

Ci+1 = AIBI + BIC! + CIAI = AIBi + (AI ⊕ BI) (AIBI 代表与运算)

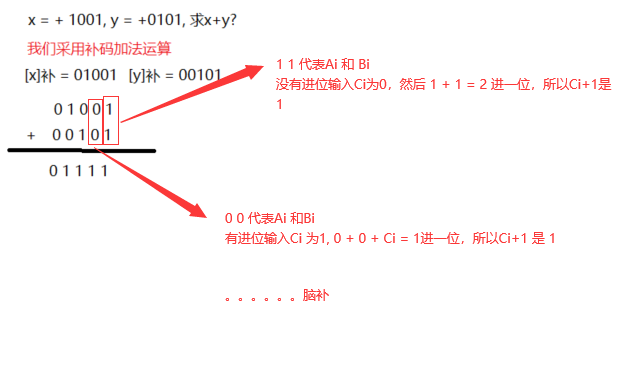

补码加法运算

对照上面的表

串行全加器图

引入问题:当加法运算个数太多时,下一位的全加器必须等待上一位的全加器的进位信息C,才能进行接下来的运算,这种串行加法器的设计会影响计算速度

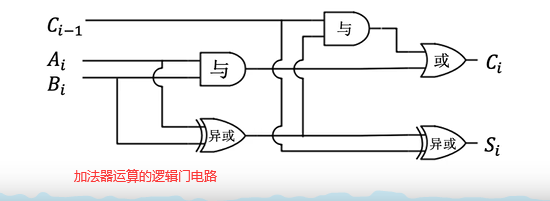

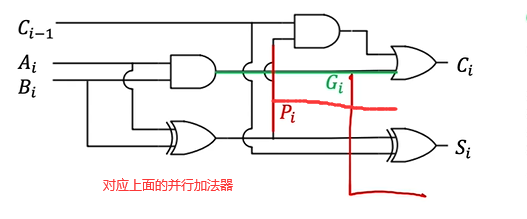

逻辑电路图:

表达式

Ci = AiBi + (A ⊕ B)CI-1

Fi = Ai ⊕ BI ⊕ CI (Fi代表 i 位的和)

并行加法器

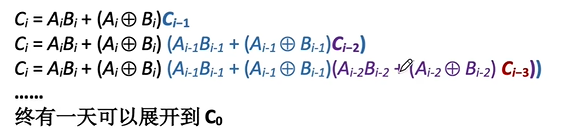

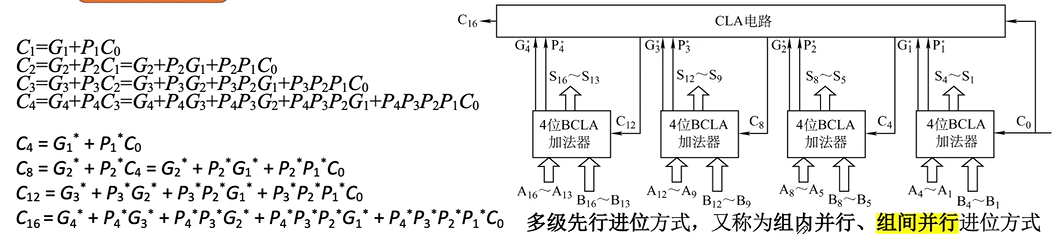

表达式

Ci = AiBi + (A ⊕ B)CI-1

Fi = Ai ⊕ BI ⊕ CI (Fi代表 i 位的和)

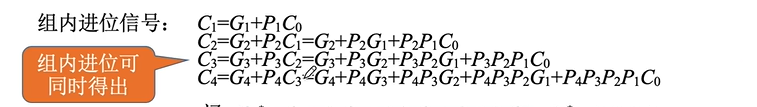

转换:

GI = AiBI (G 是进位发生输出)

PI = AI ⊕ BI (P 是进位传送输出)

CI = AIBi + (AIBi)Ci-1 = Gi + PiCi-1 (Gi + PiCi-1进行或运算)

逻辑电路图和逻辑运算一一对应

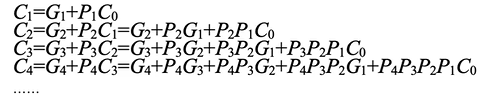

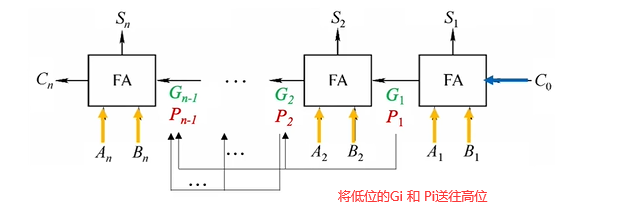

并行加法器

并行加法器逻辑电路图

引入问题:从图中我们可以看出各个加法器的进位信号同时形成,同时形成,弥补了串行加法器等待进位信号的缺点,但是会形成一个问题当Ci的 i值足够大时,逻辑表达式就会越来越复杂,从而造成逻辑电路越复杂

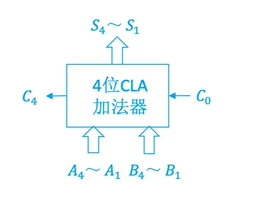

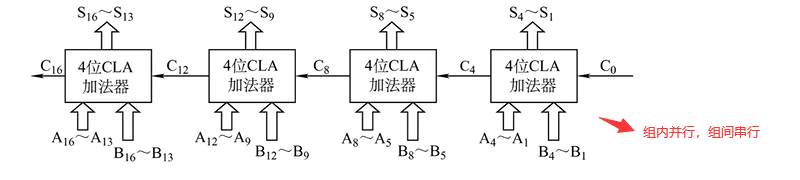

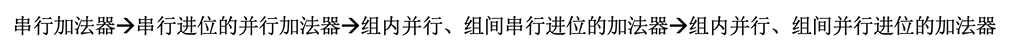

CLA加法器

为了解决上面的问题,我们引入了CLA加法器

它是由4个FA和一些新的线路、运算逻辑组成

引入问题:组内加法器并行,进位是同时进行的,但是组间的进位信息还是串行的

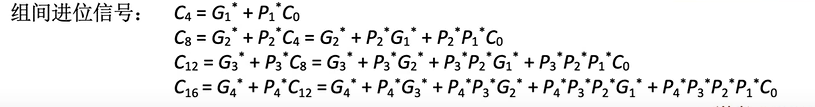

转换:

P* = P4P3P2P1 (P* 是成组进位发生输出)

G* = G4 + P4G3 + P4P3G2 + P4P3P2G1 (P* 是成组进位传送输出)

最后

以上就是幸福中心最近收集整理的关于算术逻辑运算单元ALU的串行和并行加法器串行加法器并行加法器的全部内容,更多相关算术逻辑运算单元ALU内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复