文章目录

- 题目

- 题解

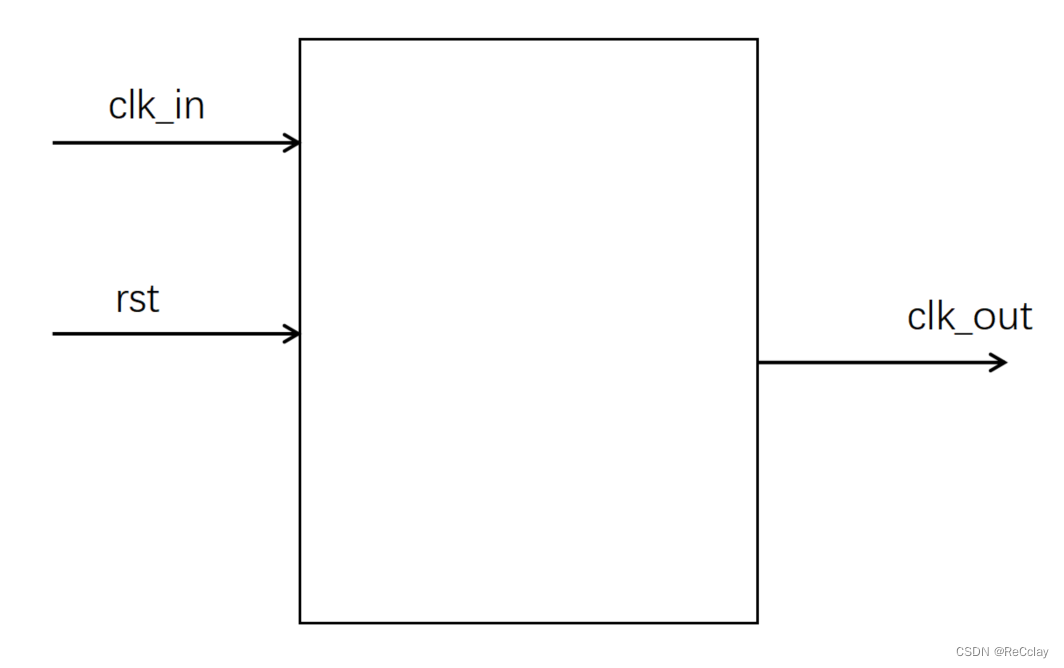

题目

描述

请设计一个可以实现任意小数分频的时钟分频器,比如说8.7分频的时钟信号

注意rst为低电平复位

提示:

其实本质上是一个简单的数学问题,即如何使用最小公倍数得到时钟周期的分别频比。

设小数为nn,此处以8.7倍分频的时钟周期为例。

首先,由于不能在硬件上进行小数的运算(比如2.1个时钟这种是不现实的,也不存在3.3个寄存器),小数分频不能做到分频后每个时钟周期都是源时钟的nn倍,也无法实现占空比为1/2,因此,考虑小数分频,其实现方式应当为53个clkout时钟周期是10个clkin时钟周期的8.7倍。

信号示意图:

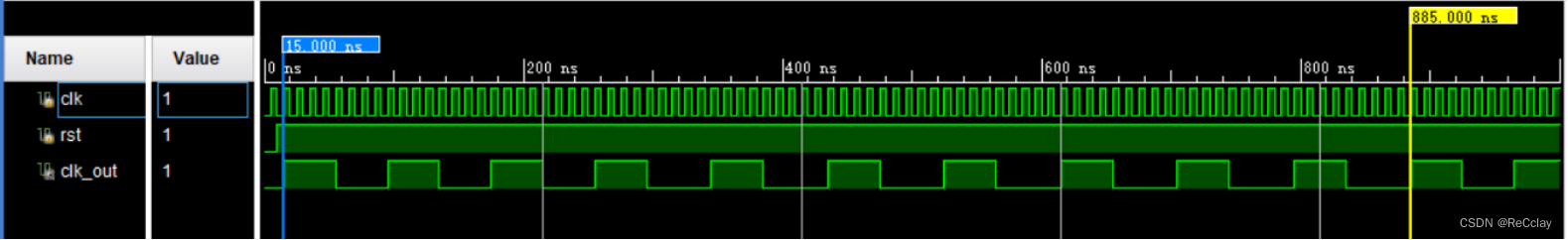

波形示意图:

输入描述:

输入信号 clk_in rst

类型 wire

输出描述:

输出信号 clk_out

最后

以上就是舒适电话最近收集整理的关于【校招Verilog进阶挑战】 时序逻辑篇:VL17 任意小数分频题目的全部内容,更多相关【校招Verilog进阶挑战】内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复