实验基于多思计算机组成原理网络虚拟实验系统

实验室地址:http://www.dsvlab.cn/

实验目的:

1.完成全加器的电路图

2.实现 2 位串行进位并行加法器

前置知识:

半加器:

半加器电路是指:对两个输入数据位相加,输出一个结果位和进位,没有进位输入的加法器电路。 是实现两个一位二进制数的加法运算电路

类比:现实中我们可以很容易计算出 1 + 1 = 2这样简单的基础加法问题,但是计算机中没有人这样智能,计算机本质就是元器件,逻辑电路组成的工具。

计算机必须借助基本的逻辑元部件才能实现加法操作。

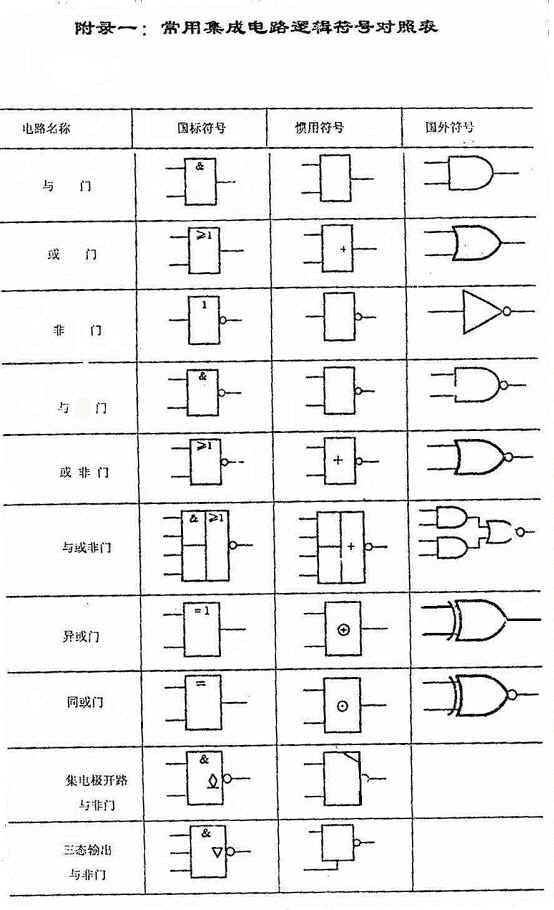

基本电路逻辑单元

半加器逻辑真值表

| 被加数A | 被加数字B | 和数S | 进位数C |

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

不难看出:

半加器的基本实现通过基本逻辑单路异或电路就能实现对和的计算

进位的统计则完全可以借助一个与门电路来进行实现

特点:

输入没有进位,而输出没进位

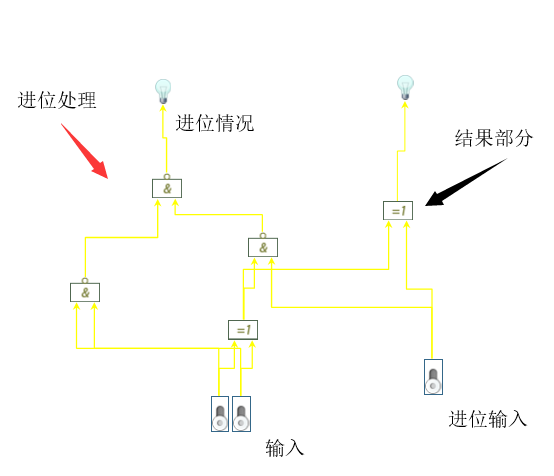

基本电路图:

不难看出,半加器的电路还是相对简单的,一个异或逻辑单元,一个与门逻辑单元,接入输入信息接通电源后就能实现~~~

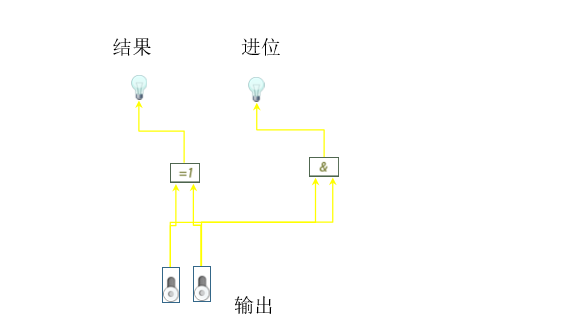

全加器

全加器英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器

特点:

在半加器基础上改进,使得输入有进位,输出有进位,即三输入二输出的一个部件

全加器真值表

| 输入 | 输出 | |||

| Ai | Bi | Ci | Si | Ci+1 |

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 1 |

1 位二进制加法器有三个输入量:两个二进制数字 Ai、Bi 和一个低位的进位信号 Ci,这三个值相加产生一个和输出 Si 以及一个向高位的进位输出 Ci+1,这种加法单元称为全加器,其逻辑方程如下:

Si=Ai⊕Bi⊕Ci (1.1) [⊕异或操作]

Ci+1=AiBi+BiCi+CiAi所需电路元器件:

与非门、异或门、开关、指示灯

思路:

求和部分:逐位相加,两个输入相加,之后再同进位输入信息相加 --------> 异或门实现

进位部分:输入与非 输入和同进位与非 之后两个结果在进行与非 -----> 借助与非电路实现

电路逻辑图:

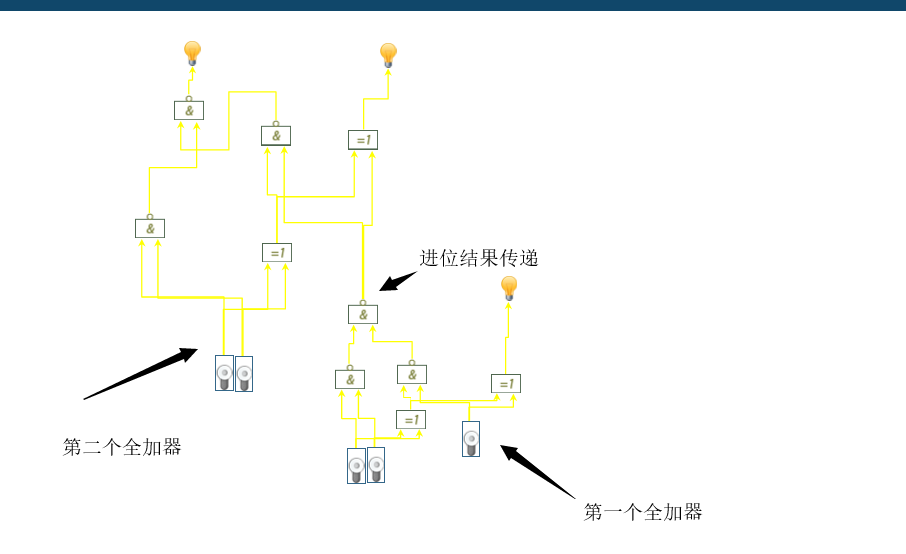

2 位串行进位并行加法器 的实现

将全加器进行串接,进位信息前一个全加器提供

串行进位并行加法器的主要缺点是什么?有改进的方法吗?

答:高位的运算必须等到低位的进位产生才能进行,因此运算速度较慢。改进方法:为了提高运算速度,可采用超前进位的方式,即每一位的进位根据各位的输入同时预先形成,而与低位的进位无关。比如74ls283芯片

能使用全加器构造出补码加法/减法器吗?

答:可以。因为当前计算机中加法和减法都是通过加法器来实现的。数值一律用补码来存储可以将符号位和其他位一起处理,便于加法和减法运算。

小结

重点阐述半加器,全加器,二位串行并行加法器的原理及电路图,同时给出真值表的分析

最后

以上就是俊秀西牛最近收集整理的关于计算机组成原理实验一:全加器实验的全部内容,更多相关计算机组成原理实验一内容请搜索靠谱客的其他文章。

发表评论 取消回复