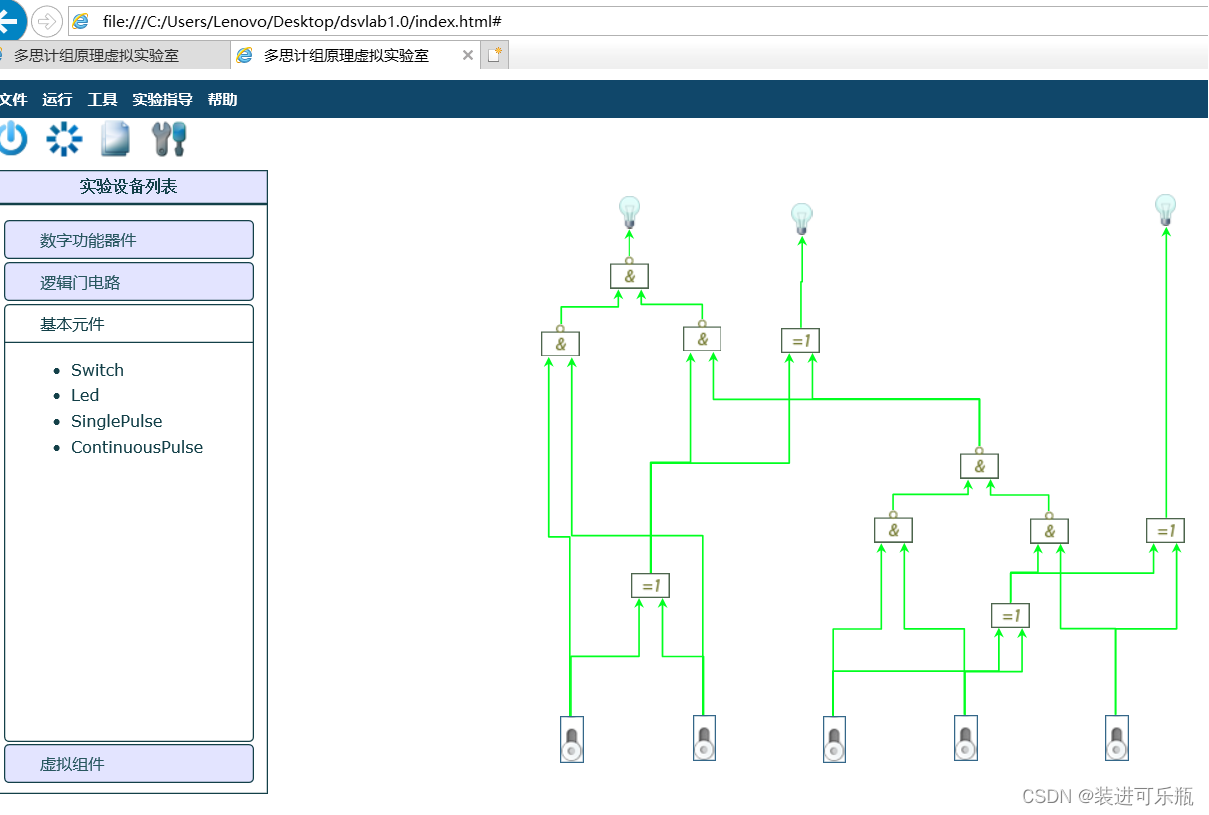

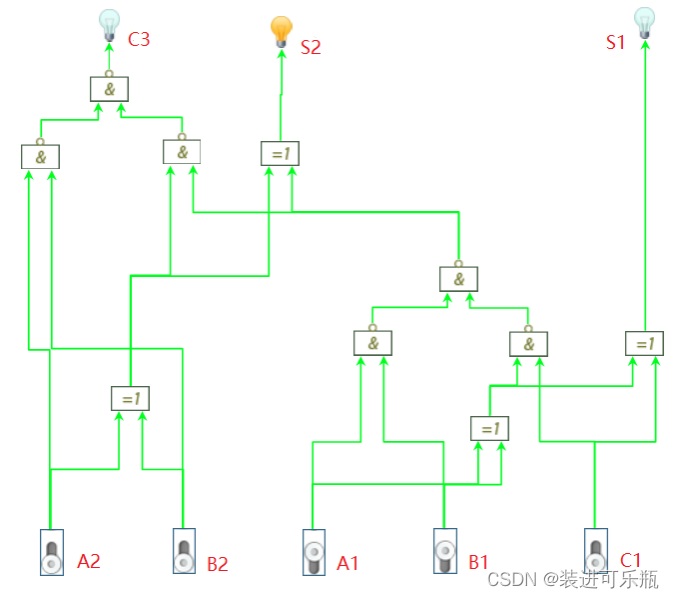

设计2位串行进位并行加发器电路,运行虚拟实验系统,根据下述的逻辑方程,得到如图 1 所示的实验电路。

逻辑方程:

s1=A1⊕B1⊕C1

c2=A1B1+B1C1+C1A1

s2=A2⊕B2⊕C2

C3=A2B2+B2C2+C2A2

图1 两位全加器设计电路图

- 打开电源开关,按表 1 中的输入信号设置数据开关,1中列出对应的输出值。

表 1 2 位串行进位并行加法器真值表

| 输入 | 输出 | ||||||

| A2 | A1 | B2 | B1 | C1 | S2 | S1 | C3 |

| 0 | 1 | 0 | 1 | 0 | 1 | 0 | 0 |

| 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

| 1 | 1 | 1 | 1 | 1 | 1 | 1 | 1 |

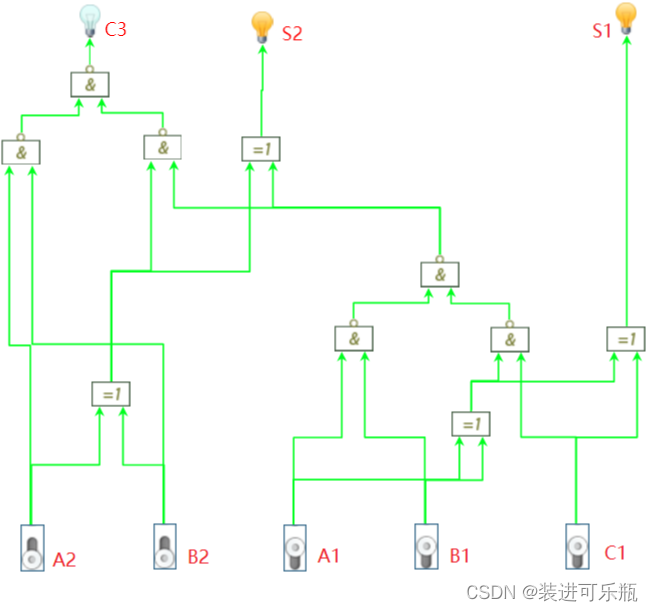

表1输入结果对应的输出值的截图,如下图所示。

输入00110输出结果

输入00111输出结果

最后

以上就是怡然月亮最近收集整理的关于实现一个 2 位串行进位并行加法器的全部内容,更多相关实现一个内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复