原理图设计以及VHDL设计 一位加法器

- 全加器原理

- 全加器真值

- 输出表达式

- 原理图设计法

- VHDL设计法

- 代码如下:

全加器是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。

全加器原理

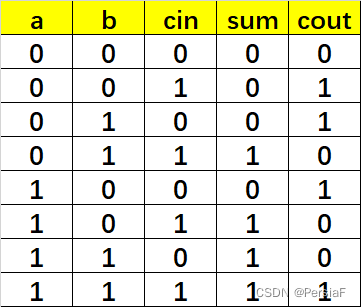

全加器真值

a,b为输入,cin为进位输入,sum为输出和,cout为输出进位。

输出表达式

sum = a xor b xor cin

cout =(a and b) or (b and cin) or (a and cin)

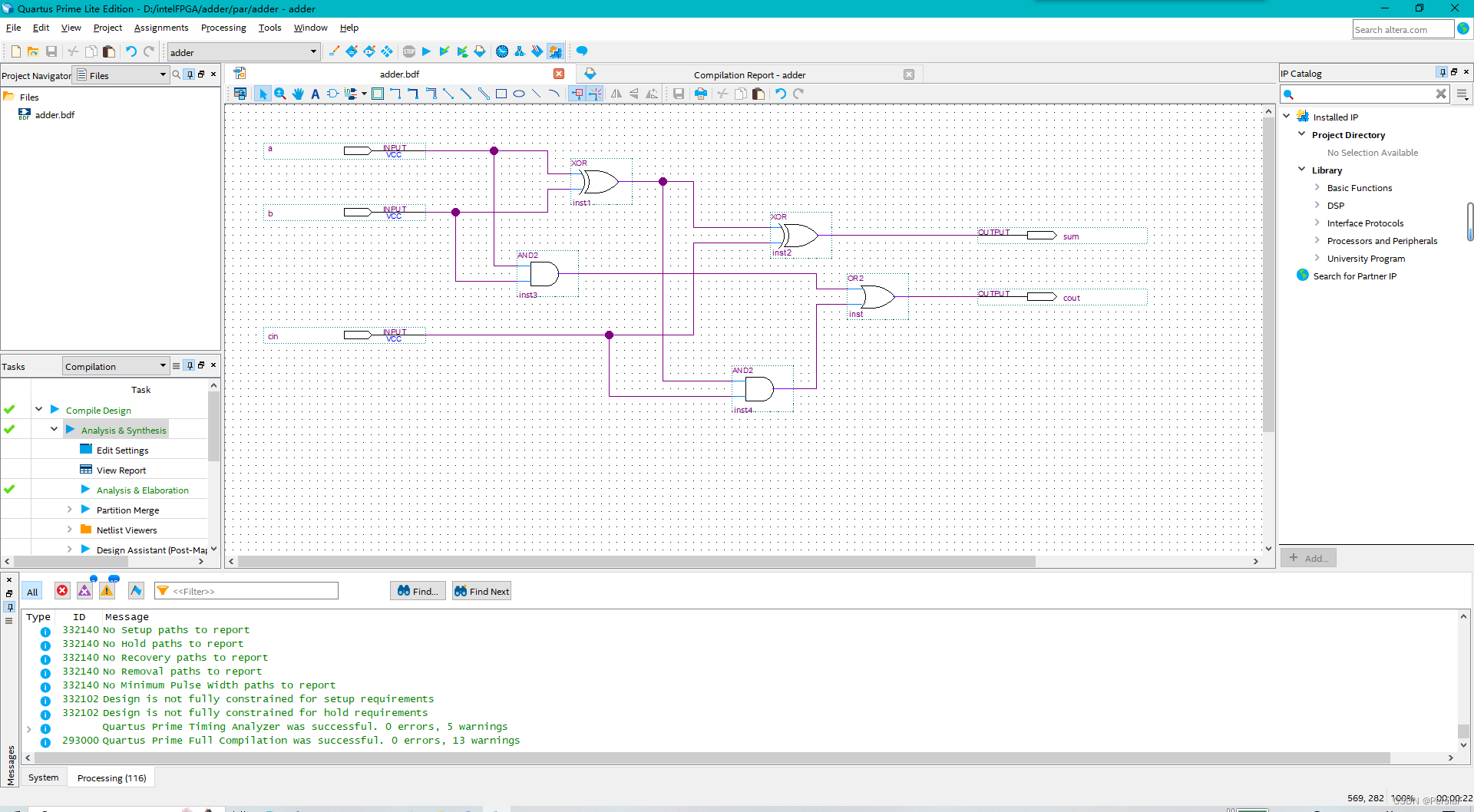

原理图设计法

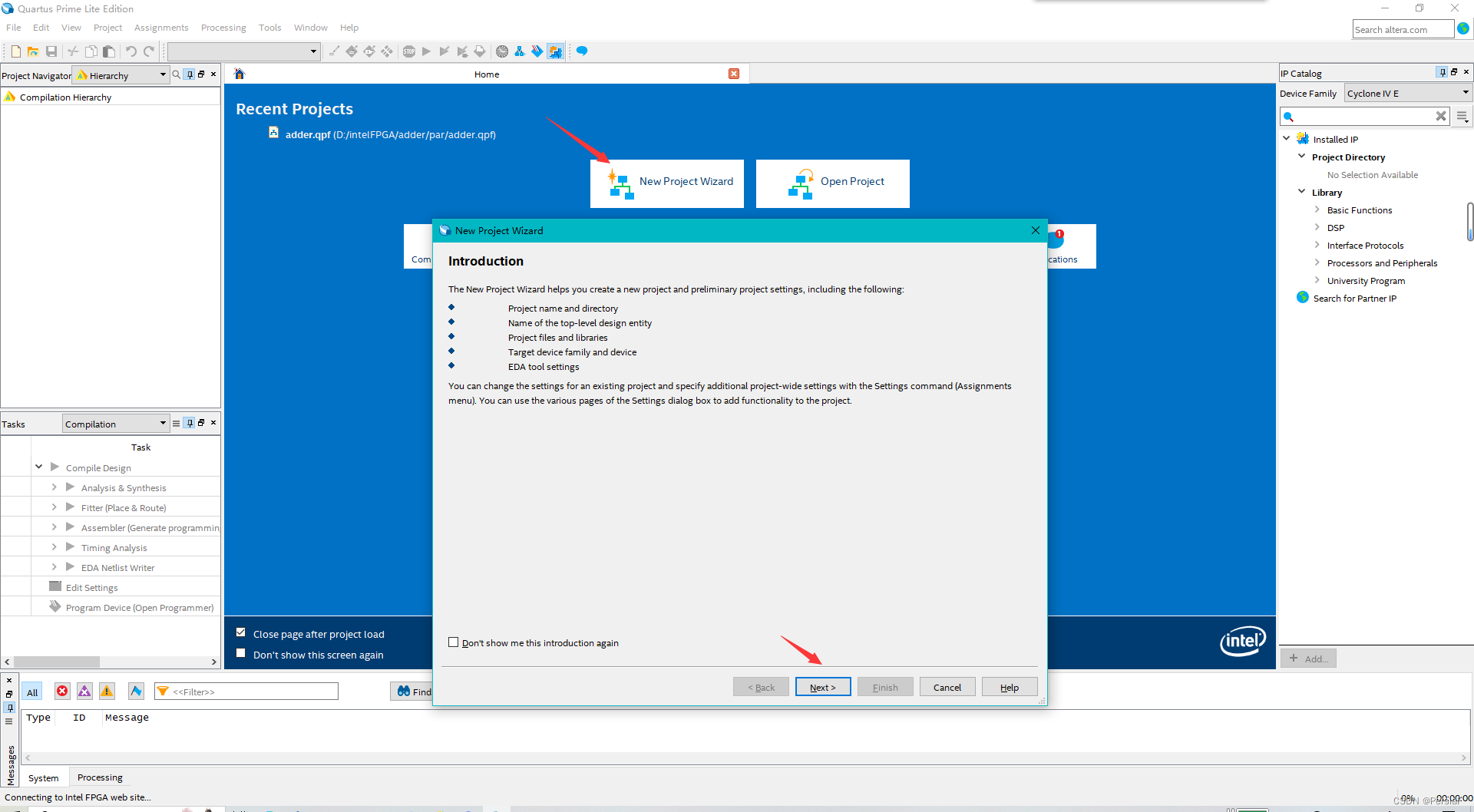

创建项目文件

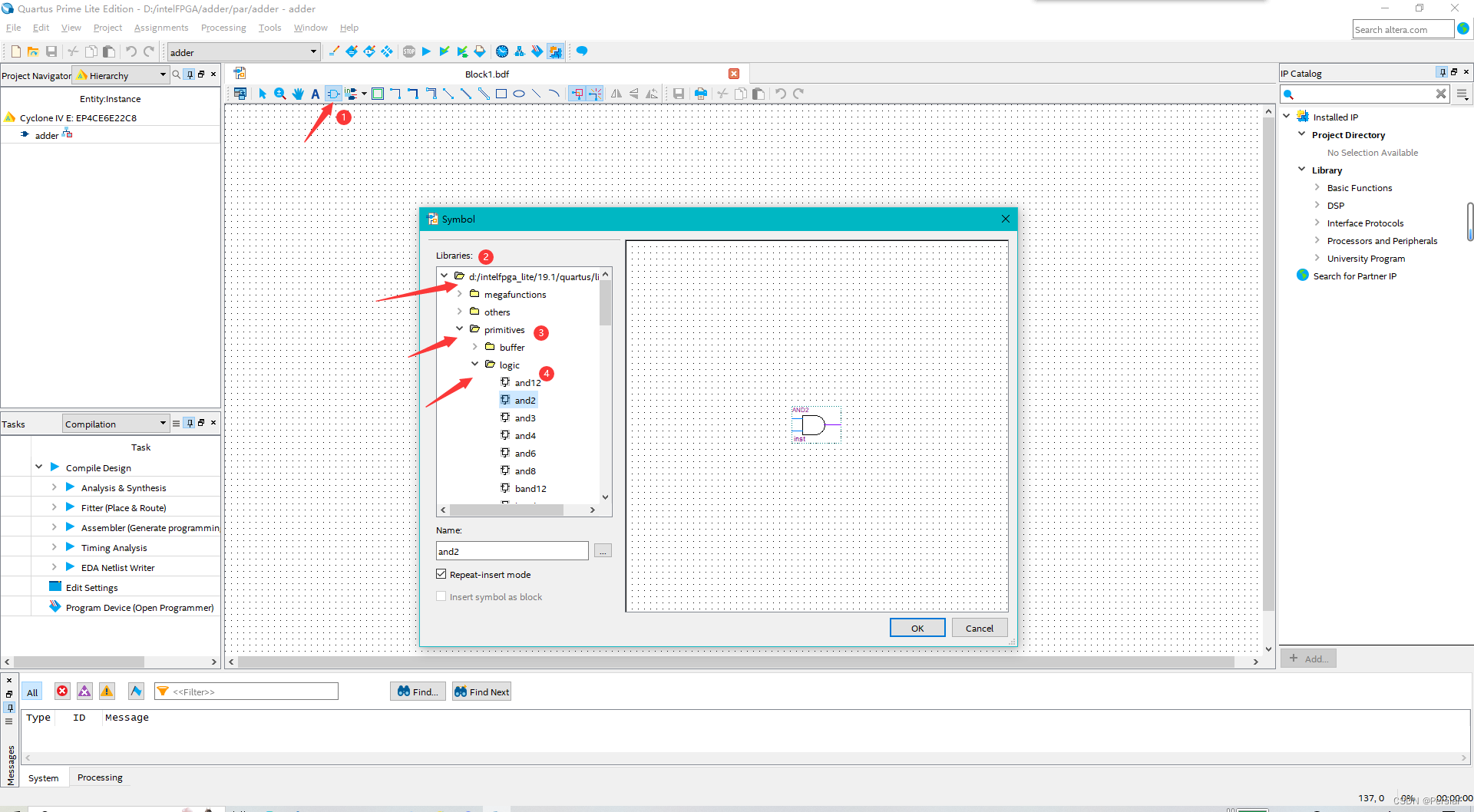

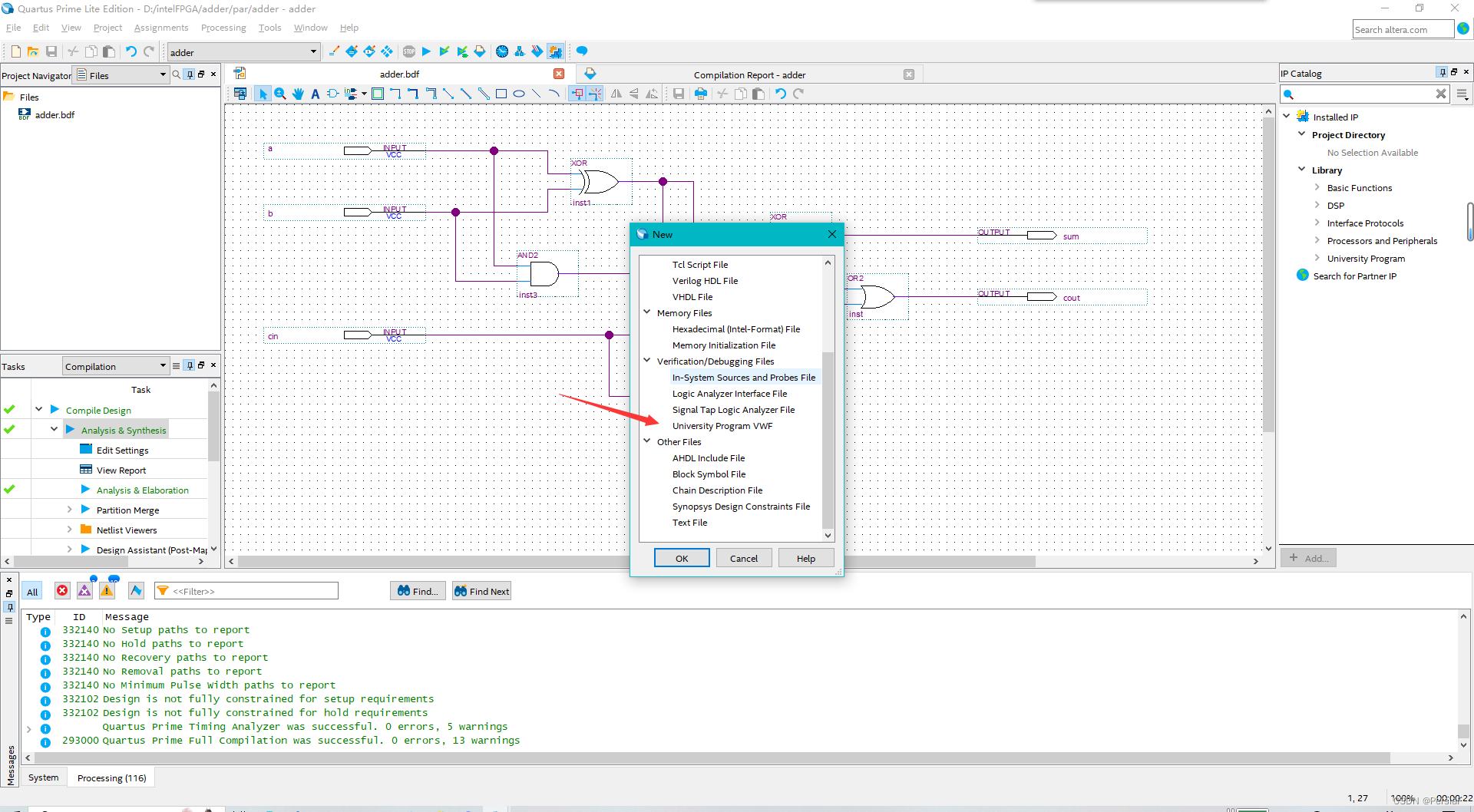

添加原理图设计文件

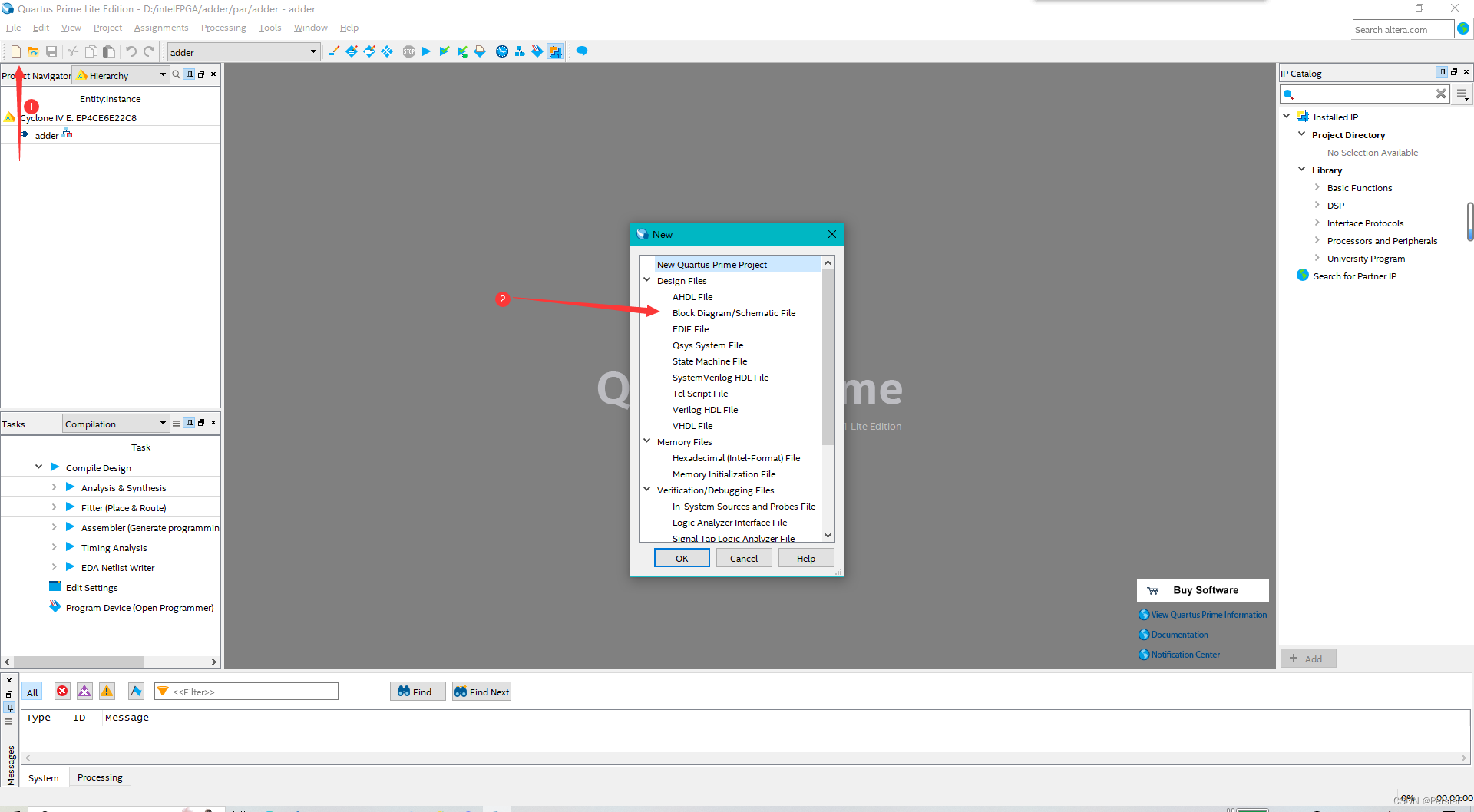

在原理图设计板块中找到对应的元器件,添加对应的IO口

放置好所有的元器件以及IO后,将鼠标移到对应模块连接处,将电路图连接起来。然后保存编译。

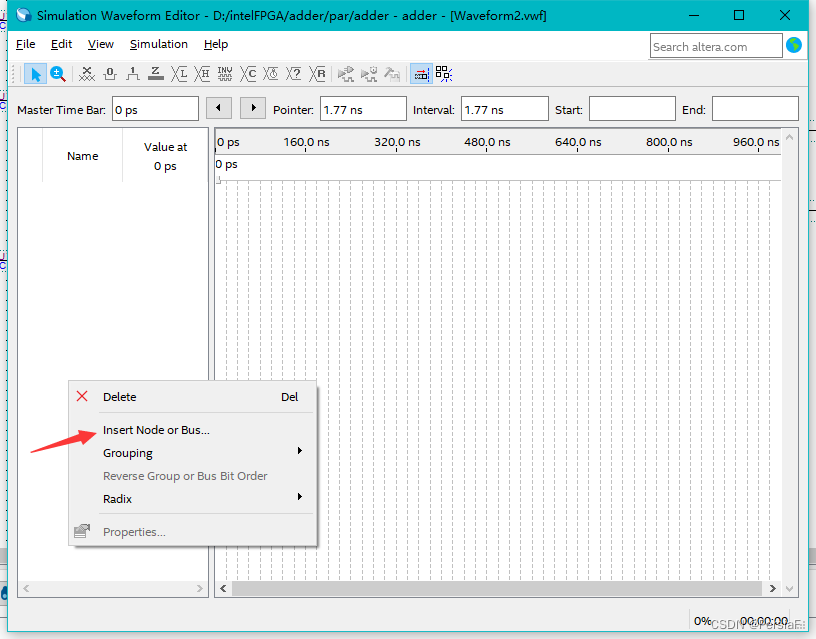

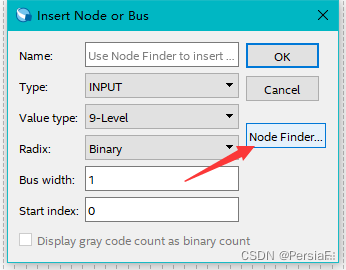

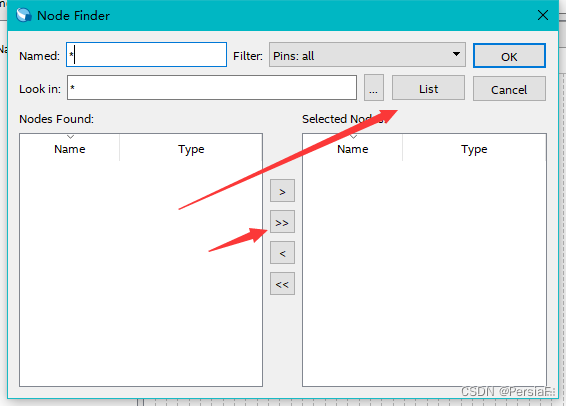

添加波形文件,然后鼠标右击进入选择信号,点击>>添加。

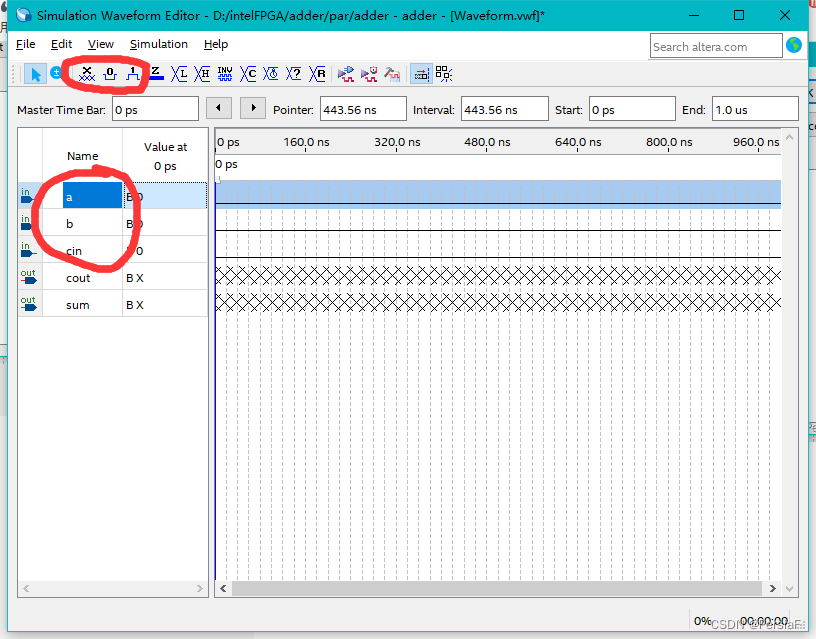

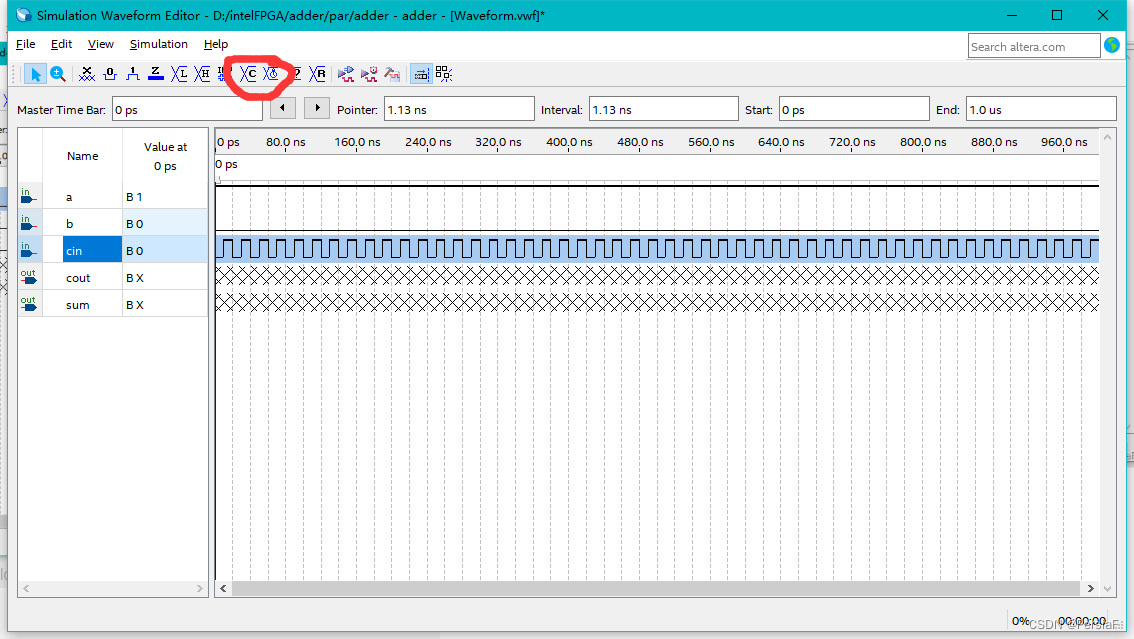

设置初始激励信号,可以选择0,1 或者后面的定时器与计数器,可以添加不同的值,去验证项目电路是否正确。

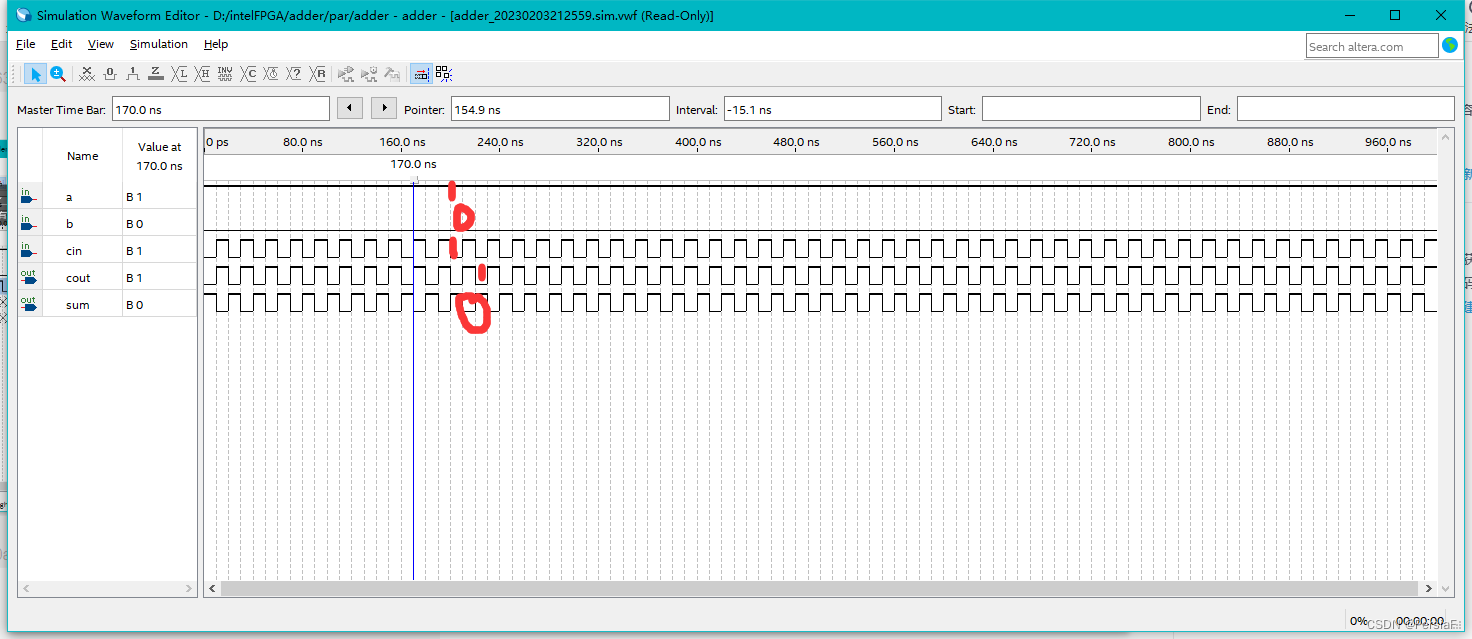

生成对应的网表后点击功能仿真,验证电路功能是否正确。

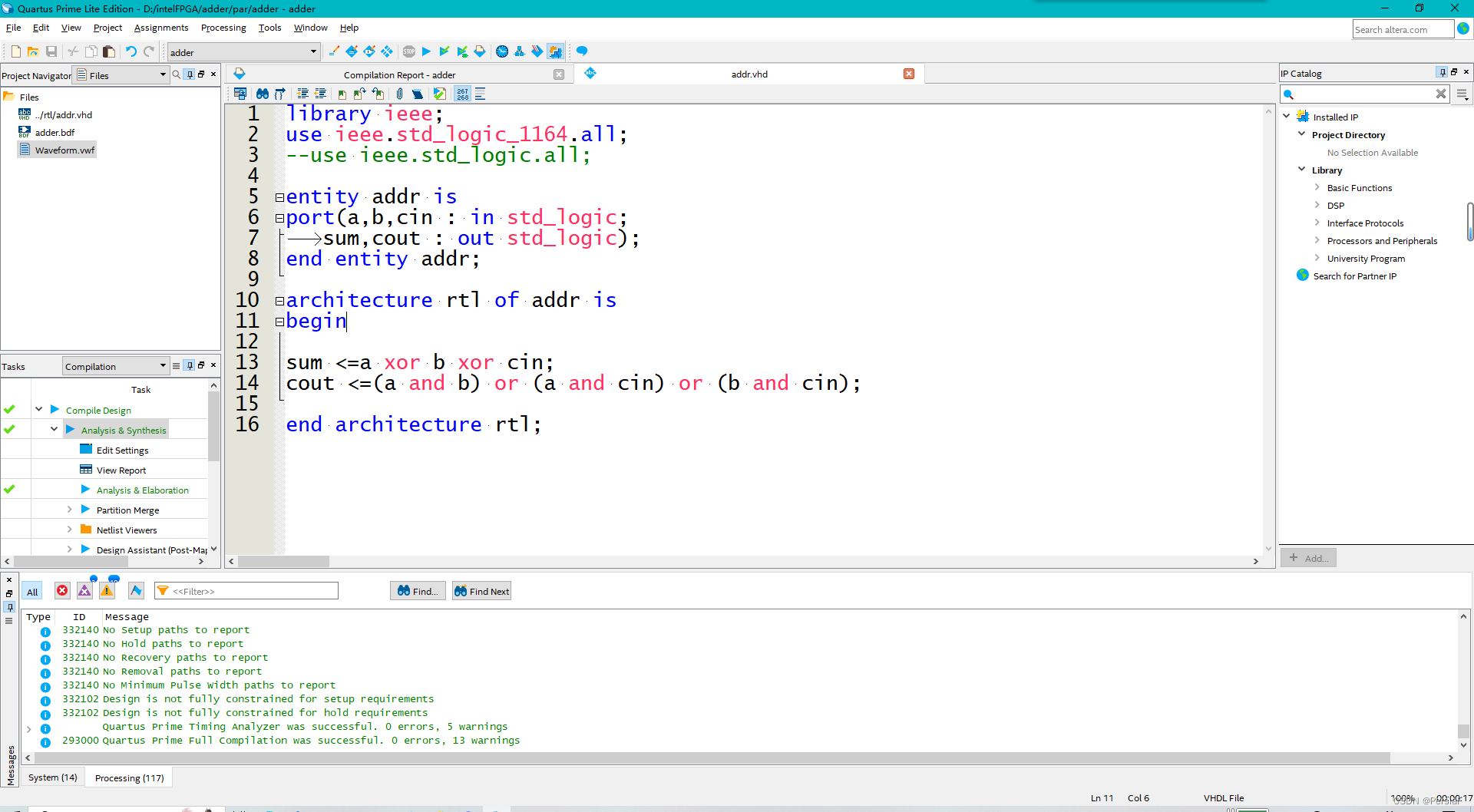

VHDL设计法

点击左边的文件添加VHDL文件,将代码敲入后,鼠标右键点击代码文件设置为定成==顶层文件,不然会报错。

代码如下:

library ieee;--库文件引用

use ieee.std_logic_1164.all;

entity addr is

port(a,b,cin : in std_logic;--端口配置

sum,cout : out std_logic);

end entity addr;

architecture rtl of addr is--结构体配置

begin

sum <=a xor b xor cin;

cout <=(a and b) or (a and cin) or (b and cin);

end architecture rtl;

最后

以上就是坦率钢笔最近收集整理的关于原理图以及vhdl设计一位全加器的全部内容,更多相关原理图以及vhdl设计一位全加器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复