采用2位7段数码显示器设计一个00~99循环计数器电路。输入包括一个时钟输入端和一个低电平复位端,

复位时输出88,两个输出分别控制高位和低位数码显示器。

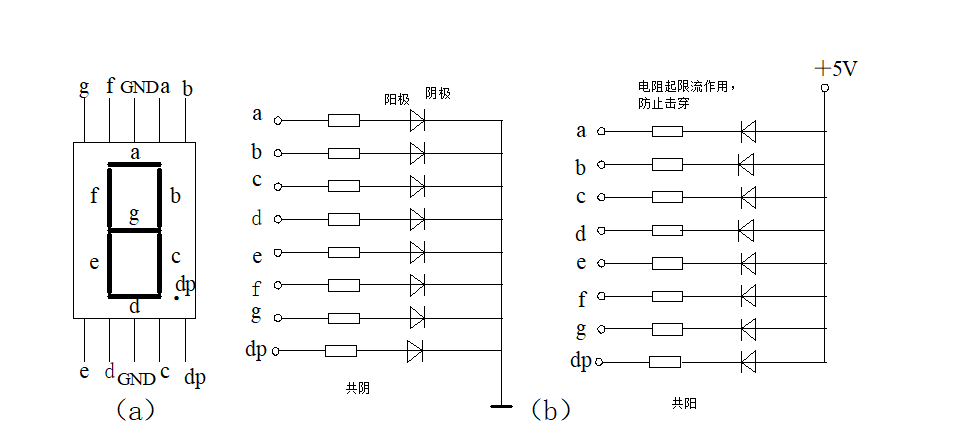

7位数码管显示器的结构图如下:

a~g分别对应输出out中的0-7,由低位到高位,其中out0表示低位,out1表示高位。

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/07/24 10:00:19

// Design Name:

// Module Name: Test1000

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module Test1000(clk,reset,out0,out1);

input clk,reset;

output [6:0] out0,out1;

reg [6:0] out0,out1;

reg [9:0] cnt;

reg [3:0] pr_state,nx_state;

reg [3:0] state;

parameter s0=0,s1=1,s2=2,s3=3,s4=4,s5=5,s6=6,s7=7,s8=8,s9=9;

parameter zero=7'b0111111,one=7'b0000110,two=7'b1011011,three=7'b1001111,four=7'b1100110,five=7'b1101101,

six=7'b1111101,seven=7'b0000111,eight=7'b1111111,nine=7'b1101111;

always @(posedge clk or posedge reset)

if(!reset)

begin

pr_state<=s8;

state<=s8;

cnt=0;

end

else

begin

pr_state<=nx_state;

state<=cnt;

end

always @(pr_state)

case(pr_state)

s0:begin

nx_state=s1;

out0=zero;

end

s1:begin

nx_state=s2;

out0=one;

end

s2:begin

nx_state=s3;

out0=two;

end

s3:begin

nx_state=s4;

out0=three;

end

s4:begin

nx_state=s5;

out0=four;

end

s5:begin

nx_state=s6;

out0=five;

end

s6:begin

nx_state=s7;

out0=six;

end

s7:begin

nx_state=s8;

out0=seven;

end

s8:begin

nx_state=s9;

out0=eight;

end

s9:begin

nx_state=s0;

out0=nine;

cnt=cnt+1;

end

default:begin

nx_state=s0;

out0=zero;

state=zero;

end

endcase

always@(state)

case(state)

s0:begin

out1=zero;

end

s1:begin

out1=one;

end

s2:begin

out1=two;

end

s3:begin

out1=three;

end

s4:begin

out1=four;

end

s5:begin

out1=five;

end

s6:begin

out1=six;

end

s7:begin

out1=seven;

end

s8:begin

out1=eight;

end

s9:begin

out1=nine;

end

default:begin

state=s0;

out1=zero;

end

endcase

endmodule

测试代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2020/07/24 10:27:04

// Design Name:

// Module Name: Test1027

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module Test1027;

reg clk;

reg reset;

wire [6:0] out0,out1;

initial begin

clk=0;

reset=0;

#100;

reset=1;

end

always begin

#10 clk=1;

#10 clk=0;

end

Test1000 x1(

.clk (clk ),

.reset (reset ),

.out0 (out0 ),

.out1 (out1 ));

endmodule

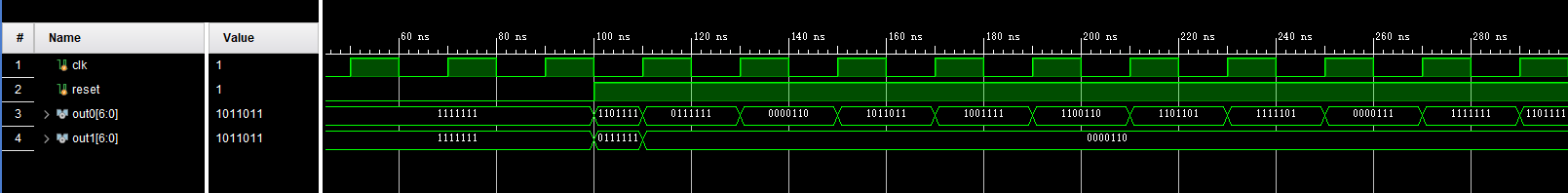

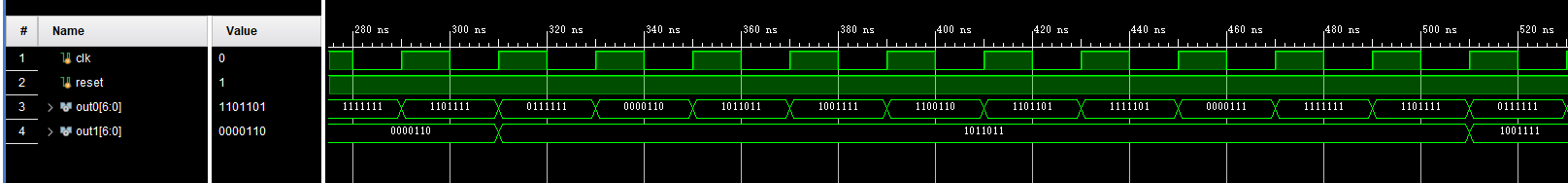

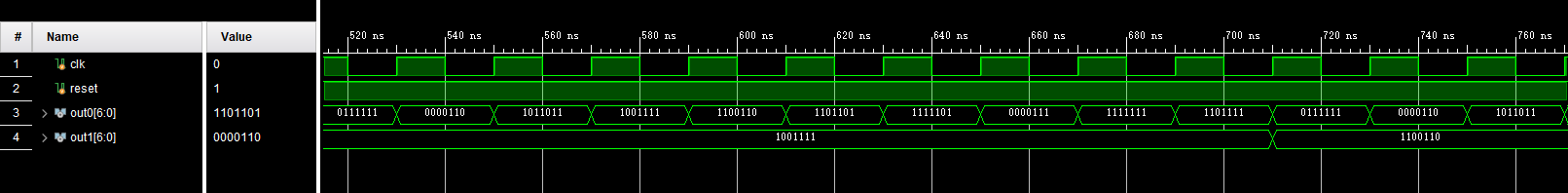

仿真波形

因为仿真波形较长,这里只展示部分,可以根据输出out信号来对照数码管显示的数字。第一仿真图中,由于复位数为88,因此会直接跳至09,然后到10,之后会正常计数,第二个周期的完整循环将会从00开始。

最后

以上就是微笑学姐最近收集整理的关于Verilog数码显示器00~99循环计数器电路的全部内容,更多相关Verilog数码显示器00~99循环计数器电路内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复