时序逻辑代码设计

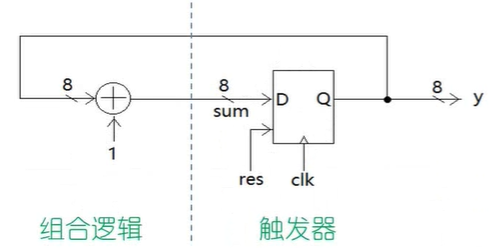

组合逻辑+触发器=时序逻辑

计数器

组合逻辑:这是一个加法器,做加一计算

Verilog代码:

`timescale 1ns/10ps//写testbench定义时间单位

module counter(

clk,//时钟信号

res,//复位信号

y

);

//端口属性

input clk;

input res;

output[7:0] y;//八位计数器

//组合逻辑电路

reg[7:0] y;//触发器,定义为reg型,虽然是输出,但是要在always语句里对它赋值,要做reg型变量定义

wire[7:0] sum;//+1运算的结果

assign sum=y+1;//组合逻辑部分

//触发器工作

always@(posedge clk or negedge res)//敏感变量为时钟和复位沿;

//如果复位信号到来(复位下降沿)

if(~res)begin

y<=0;

end

//时钟触发,正常工作时(时钟上升沿)

else begin

y<=sum;

end

endmodule测试代码testbench

//-------testbench of counter----

module counter_tb;

reg clk,res;

wire[7:0] y;

//模块例化

counter counter(

.clk(clk),//时钟信号

.res(res),//复位信号

.y(y)

);

//给clk,res赋值

//clock要反复动,不能用initial给clk大量赋值

//使用initial赋初值

initial begin

clk<=0;res<=0;//赋初值,复位清零

#17 res<=1;//让res不复位,释放复位

#6000 $stop;//八位计数器跑两遍需要的时间,到时间调用系统任务结束

end

//clk变化

always #5 clk<=~clk;//每过5ns时钟翻一次,周期为10ns

endmodule最后

以上就是霸气万宝路最近收集整理的关于Verilog——计数器的全部内容,更多相关Verilog——计数器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复