Verilog之计数器资源优化

采用Verilog编写计数器延时或定时时,会消耗FPGA的片内资源,同时也进而对综合出来的逻辑电路的路径延时产生影响。为此本文探讨以下两种情况对FPGA片内资源的消耗,以及路径延时对系统最大工作频率的影响。其一,计数器实现语句位于同一个always逻辑块中;其二,计数器实现语句采用单独的always逻辑块,与程序其他逻辑块相互独立。

(1)计数器实现语句与程序其他逻辑位于同一个always逻辑块

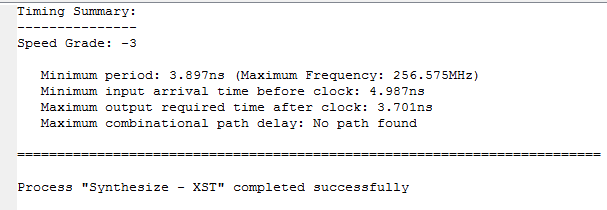

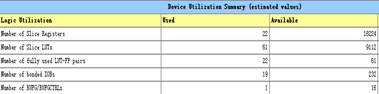

上述代码如下所示,系统最大工作频率约为256.6MHz,消耗61个LUT,22个寄存器。

//-------------------------------------------------

Clear: begin

if( (!en)&& (cnt1==cnt_ms) ) begin

cnt1 <= 0;

dout <= 0;

state <= Idle;

end

else begin

cnt1 <= cnt1 + 1;

state <= Clear;

end

end

//-------------------------------------------------

(2)计数器实现语句与程序其他逻辑位于两个独立的always逻辑块

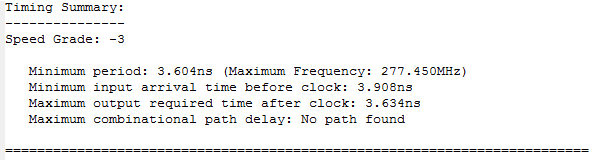

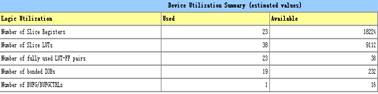

上述代码如下所示,系统最大工作频率约为277.5MHz,消耗38个LUT,23个寄存器。多用的一个寄存器为DelayOver变量。

//-------------------------------------------------

Clear: begin

if( (!en)&& DelayOver ) begin

dout <= 0;

state <= Idle;

end

else begin

state <= Clear;

end

end

default: state <= Idle;

endcase

end

always@(posedge clk)

if(rst) begin

cnt1 <= 0;

DelayOver <= 0;

end

else begin

if(cnt1==cnt_ms) begin

cnt1 <= 0;

DelayOver <= 1;

end

else begin

cnt1 <= cnt1 + 1;

DelayOver <= 0;

end

end

//-------------------------------------------------

结论

对比两种情况可知,尤其对于位宽较大的计数器可以进行优化,由独立的always块进行实现,同时可以将一个计数器拆分为两级计数实现,这样可以减小计数器的位宽。

最后

以上就是开放西装最近收集整理的关于Verilog之计数器资源优化的全部内容,更多相关Verilog之计数器资源优化内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复