在VHDL设计中,常需要将自己设计的子模块或者实体进行组合,设计复杂的数字电路。在quartus中既可以采用原理图设计方式,对设计实体进行连线,也可以采用VHDL程序实现,采用元器件例化语句。下面以一个利用两个四位加法器设计一个八位加法器的例子,介绍元件例化的方法。

如下是四位加法器的代码,实体输入为四位的a、b两个端口、上一级进位信号cin,输出为四位的运算结果s以及进位信号cout。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adder4b is

port(

cin:in std_logic;

a,b:in std_logic_vector(3 downto 0);

s:out std_logic_vector(3 downto 0);

cout:out std_logic

);

end adder4b;

architecture behave of adder4b is

signal sint:std_logic_vector(4 downto 0);

signal aa,bb:std_logic_vector(4 downto 0);

begin

process(cin)

begin

aa<='0'&a(3 downto 0);

bb<='0'&b(3 downto 0);

sint<=aa+bb+cin;

s(3 downto 0)<=sint(3 downto 0);

cout<=sint(4);

end process;

end behave;

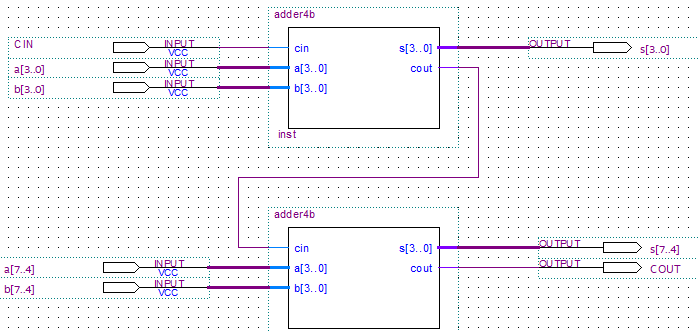

要采用元件例化的方式设计,我们首先要清楚元器件之间的连接方式。采用原理图方式,利用两个四位加法器设计八位加法器的原理图如下:

明确了连接方式后,再通过VHDL语言进行描述设计,八位加法器的代码如下

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity adder8b is

port(

cin:in std_logic;

a,b:in std_logic_vector(7 downto 0);

s:out std_logic_vector(7 downto 0);

cout:out std_logic

);

end adder8b;

architecture behave of adder8b is

component adder4b

port(

cin:in std_logic;

a,b:in std_logic_vector(3 downto 0);

s:out std_logic_vector(3 downto 0);

cout:out std_logic

);

end component;

signal carry_out:std_logic;

begin

u1:adder4b port map(cin=>cin,a=>a(3 downto 0),b=>b(3 downto 0),s=>s(3 downto 0),cout=>carry_out);

u2:adder4b port map(cin=>carry_out,a=>a(7 downto 4),b=>b(7 downto 4),s=>s(7 downto 4),cout=>cout);

end behave;

进行设计时,首先要对八位加法器实体进行声明和引脚定义,然后在调用四位加法器的时候,要先在结构体部分对调用的四位加法器进行声明。元器件的说明采用component语句,格式如下:

component 调用的元件名

generic 参数说明(可省略,一般自制元件不需要说明)

port 端口说明

end component;

注意元件说明语句应该在architecture 和begin之间。

对元件进行说明之后,为了实现元件例化,就必须吧被调用的元器件的端口信号与相应的端口信号进行连接,以实现电路连接的功能,元件例化的格式如下:

标号名:元件名

generic map(参数映射,可省略)

port map(端口映射)

例如八位加法器中低位的加法

u1:adder4b port map(cin=>cin,a=>a(3 downto 0),b=>b(3 downto 0),s=>s(3 downto 0),cout=>carry_out);

u1就是标号名,adder4b 就是调用的元器件名字,port map括号内就是端口的映射,将端口的信号与实际的信号连接,调用元器件的端口名字写前面,实际端口名字写后面,中间通过=>连接。例如将输入端口a、b(4位)与实际输入端口ab(8位)的低四位相连,cin 与cin相连,输出端口S(4位)与实际输出端口s(8位)的低四位相连,以此类推。这里定义了一个中间变量carry_out,用于传递低四位加法的进位信号给高四位。因此高位加法的进位信号输入就为carry_out,例化语句如下:

u2:adder4b port map(cin=>carry_out,a=>a(7 downto 4),b=>b(7 downto 4),s=>s(7 downto 4),cout=>cout);

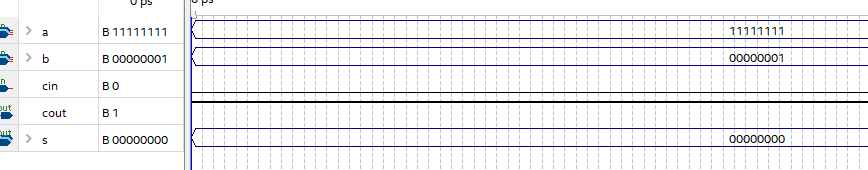

完成设计后,进行仿真验证,结果如下图

可以看到运算结果正确,且进位信号正确输出。

通过这样一个例子,熟悉了元器件例化设计方式,方便了以后的设计。

最后

以上就是虚幻丝袜最近收集整理的关于VHDL学习-元件例化的全部内容,更多相关VHDL学习-元件例化内容请搜索靠谱客的其他文章。

发表评论 取消回复