一、实验目的

(1)学习并掌握Quartus II的使用方法

(2)学习简单时序电路的设计和硬件测试。

(3)学习使用VHDL 语言方法进行逻辑设计输入

(4)学习设计一个流水灯电路,并在实验开发系统上熟悉运行输入及仿真步骤原理

二、实验仪器设备

(1) PC机一台。

(2)Quartus Ⅱ开发软件一套

(3)EDA实验开发系统一套(EP1C12Q240C8)

三、实验原理

FPGA 的所有I/O控制块都可以允许每个1/O引脚单独配置为输入口,不过这种配置是系统自动完成的,一旦该输入口被设置为输入口使用时,该I/O控制模块将直接使三态缓冲区的控制端接地,便得该IO 引脚对外呈高阻态,这样该I/O引脚即可用作专用输入引脚。只旦在KEY1-KEY8中有键输入,要正确地分配并锁定引脚后,在检测到键盘输入的情况下,继续判断其键盘值并作出相应的处理。

四、实验内容

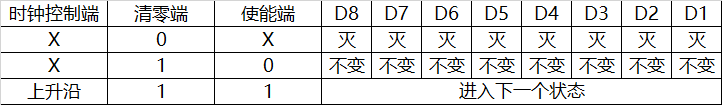

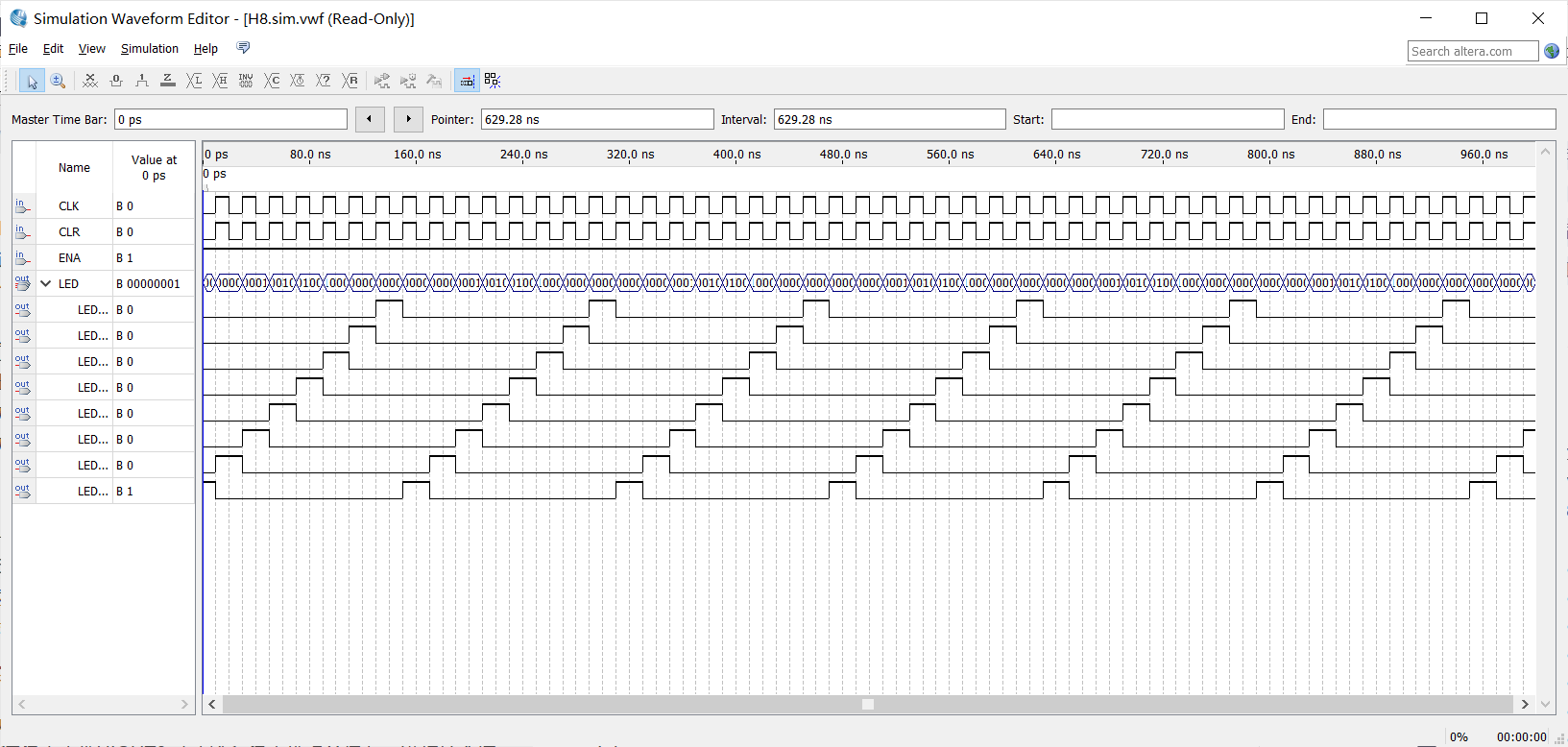

(1)基于VHDL 语言设计可用于控制LED流水灯的简单逻辑电路,电路包含三个输入、八个输出。输入信号为清零信号端CLR、时钟信号CLK 和使能信号ENA,输出信号Y接八个发光二极管。当清零信号端CLR 为低时,系统清零,此时8个LED灯全灭。当 ENA输入信号为高电平,CLK的上升沿到来时,流水灯开始流动,流动顺D1→D2→D3→D4→D5→D6→D7→D8,然后再返回D1;当ENA输入信号为低电平时,流水灯暂停,保持在原有状态。

其对应关系见表如下

(2)在Quartus II上用V

HDL 文本方式设计该流水灯电路;对该设计进行编辑、编译、综合、适配、仿真。将经过仿真的设计下载到硬件实验箱进行验证。注意选择:输入信号线3根(ENA接按键1,clr接按键2和CLK 接CLK0)、输出线8根(接发光二极管指示灯);硬件测试时为便于观察,流水速率最好在4Hz左右,测试时根据输入信号的变化观察输出信号的改变。

流水灯控制电路仿真如图所示

实验引脚锁定:

八个按键:按键1~8分别对应FPGA上的引脚233,234,235,236,237,238,239,240。

八个发光二极管:发光.极管D1~D8分别对应 FPGA 上的引脚168~161。

时钟端口:CLKO对应28CLK2对应153,CLK5对应152,CLK90对应29。

五、实验步骤

(1)启动Quartus II建立一个空白工程,然后命名为 HIGHT8.qpf。

(2)新建VHDL 源程序文件HIGHT8.vhd,输入程序代码并保存,进行综合编译,若编译过程中发现错误,则找出并更正错误,直至编译成功为止。

(3)选择目标器件并对相应的引脚进行锁定,在这里所选择的器件为Altera公司 Cyclone系列的EPIC12Q240C8芯片。将未使用的管脚设置为三态输入。则找出并更正错误,

(4)对该工程文件进行全程编译处理,若在编译过程中发现错误直至编译成功为止。接到PC机的打印机并

(5)拿出 Altera Byte Blaster II下载电缆,并将此电缆的两端分别接到PC机的打印机并口和实验箱的JTAG下载口上,打开电源,执行下载命令,把程序下载到 FPGA器件中,观察发光管发光二极管LED1~LED8的亮灭状态。

六、实验扩展

在前面实验的基础上实现其他花样流水显示,控制8个 LED灯进行花样显示,设计3种

模式:

①从左到右逐个点亮LED;

实例代码:

LIBRARY IEEE; --流水灯顶层文件

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HIGHT8 IS --顶层实体名称

PORT( --定义端口数据

CLK: IN STD_LOGIC; --定义时钟信号输入端口

CLR: IN STD_LOGIC; --定义清零控制端输入端口

ENA: IN STD_LOGIC; --定义使能信号输入端口

LED: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --定义LED灯输出端口

);

END;

ARCHITECTURE BEHAV OF HIGHT8 IS

SIGNAL A:INTEGER RANGE 0 TO 7;

SIGNAL B:STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL C:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

P1:PROCESS(CLK,CLR,ENA)

BEGIN

IF CLR='0' THEN C<="00000000";

ELSIF ENA='1'

THEN IF CLK'EVENT AND CLK='1' THEN A<=A+1;

END IF;

END IF;

END PROCESS P1;

P2:PROCESS(A)

BEGIN

CASE A IS --8位信号LED灯输出控制

WHEN 0=>B<="10000000";

WHEN 1=>B<="01000000";

WHEN 2=>B<="00100000";

WHEN 3=>B<="00010000";

WHEN 4=>B<="00001000";

WHEN 5=>B<="00000100";

WHEN 6=>B<="00000010";

WHEN 7=>B<="00000001";

END CASE;

END PROCESS P2;

P3:PROCESS(ENA)

BEGIN

IF CLR='1' AND ENA='0' THEN LED<=C;

ELSE LED<=B;

END IF;

END PROCESS P3;

END;

②从右到左逐个点亮LED;

示例代码:

LIBRARY IEEE; --流水灯顶层文件

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HIGHT8 IS --顶层实体名称

PORT( --定义端口数据

CLK: IN STD_LOGIC; --定义时钟信号输入端口

CLR: IN STD_LOGIC; --定义清零控制端输入端口

ENA: IN STD_LOGIC; --定义使能信号输入端口

LED: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --定义LED灯输出端口

);

END;

ARCHITECTURE BEHAV OF HIGHT8 IS

SIGNAL A:INTEGER RANGE 0 TO 7;

SIGNAL B:STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL C:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

P1:PROCESS(CLK,CLR,ENA)

BEGIN

IF CLR='0' THEN C<="00000000";

ELSIF ENA='1'

THEN IF CLK'EVENT AND CLK='1' THEN A<=A+1;

END IF;

END IF;

END PROCESS P1;

P2:PROCESS(A)

BEGIN

CASE A IS --LED灯输出控制

WHEN 0=>B<="00000001";

WHEN 1=>B<="00000010";

WHEN 2=>B<="00000100";

WHEN 3=>B<="00001000";

WHEN 4=>B<="00010000";

WHEN 5=>B<="00100000";

WHEN 6=>B<="01000000";

WHEN 7=>B<="10000000";

END CASE;

END PROCESS P2;

P3:PROCESS(ENA)

BEGIN

IF CLR='1' AND ENA='0' THEN LED<=C;

ELSE LED<=B;

END IF;

END PROCESS P3;

END;

③从中间到两边逐个点亮LED,3种模式循环切换,由复位键控制系统的运行和停止。

示例代码:

LIBRARY IEEE; --流水灯顶层文件

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HIGHT8 IS --顶层实体名称

PORT( --定义端口数据

CLK: IN STD_LOGIC; --定义时钟信号输入端口

CLR: IN STD_LOGIC; --定义清零控制端输入端口

ENA: IN STD_LOGIC; --定义使能信号输入端口

LED: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --定义LED灯输出端口

);

END;

ARCHITECTURE BEHAV OF HIGHT8 IS

SIGNAL A:INTEGER RANGE 0 TO 7;

SIGNAL B:STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL C:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

P1:PROCESS(CLK,CLR,ENA)

BEGIN

IF CLR='0' THEN C<="00000000";

ELSIF ENA='1'

THEN IF CLK'EVENT AND CLK='1' THEN A<=A+1;

END IF;

END IF;

END PROCESS P1;

P2:PROCESS(A)

BEGIN

CASE A IS --LED灯输出控制

WHEN 0=>B<="00011000";

WHEN 1=>B<="00100100";

WHEN 2=>B<="01000010";

WHEN 3=>B<="10000001";

WHEN 4=>B<="10000001";

WHEN 5=>B<="01000010";

WHEN 6=>B<="00100100";

WHEN 7=>B<="00011000";

END CASE;

END PROCESS P2;

P3:PROCESS(ENA)

BEGIN

IF CLR='1' AND ENA='0' THEN LED<=C;

ELSE LED<=B;

END IF;

END PROCESS P3;

END;

合并代码段:

实现:

①从左到右逐个点亮LED;

②从右到左逐个点亮LED;

③从中间到两边逐个点亮LED,3种模式循环切换,由复位键控制系统的运行和停止。

LIBRARY IEEE; --流水灯顶层文件

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY HIGHT8 IS --顶层实体名称

PORT( --定义端口数据

CLK: IN STD_LOGIC; --定义时钟信号输入端口

CLR: IN STD_LOGIC; --定义清零控制端输入端口

ENA: IN STD_LOGIC; --定义使能信号输入端口

LED: OUT STD_LOGIC_VECTOR(7 DOWNTO 0) --定义LED灯输出端口

);

END;

ARCHITECTURE BEHAV OF HIGHT8 IS

SIGNAL A:INTEGER RANGE 0 TO 23;

SIGNAL B:STD_LOGIC_VECTOR(7 DOWNTO 0);

SIGNAL C:STD_LOGIC_VECTOR(7 DOWNTO 0);

BEGIN

P1:PROCESS(CLK,CLR,ENA)

BEGIN

IF CLR='0' THEN C<="00000000";

ELSIF ENA='1'

THEN IF CLK'EVENT AND CLK='1' THEN A<=A+1;

END IF;

END IF;

END PROCESS P1;

P2:PROCESS(A)

BEGIN

CASE A IS --8位信号LED灯输出控制

WHEN 0=>B<="10000000";

WHEN 1=>B<="01000000";

WHEN 2=>B<="00100000";

WHEN 3=>B<="00010000";

WHEN 4=>B<="00001000";

WHEN 5=>B<="00000100";

WHEN 6=>B<="00000010";

WHEN 7=>B<="00000001";

WHEN 8=>B<="00000001";

WHEN 9=>B<="00000010";

WHEN 10=>B<="00000100";

WHEN 11=>B<="00001000";

WHEN 12=>B<="00010000";

WHEN 13=>B<="00100000";

WHEN 14=>B<="01000000";

WHEN 15=>B<="10000000";

WHEN 16=>B<="00011000";

WHEN 17=>B<="00100100";

WHEN 18=>B<="01000010";

WHEN 19=>B<="10000001";

WHEN 20=>B<="10000001";

WHEN 21=>B<="01000010";

WHEN 22=>B<="00100100";

WHEN 23=>B<="00011000";

END CASE;

END PROCESS P2;

P3:PROCESS(ENA)

BEGIN

IF CLR='1' AND ENA='0' THEN LED<=C;

ELSE LED<=B;

END IF;

END PROCESS P3;

END;

七、实验要求

(1)选择实验电路模式5

(2)设计仿真文件,进行软件验证

(3)用VHDL程序设计方法实现流水灯设计

(4)通过下载线下载到实验系统上进行硬件测试验证

工程源代码下载:流水灯电路设计源代码–VHDL

最后

以上就是听话台灯最近收集整理的关于流水灯电路设计实验--VHDL的全部内容,更多相关流水灯电路设计实验--VHDL内容请搜索靠谱客的其他文章。

发表评论 取消回复