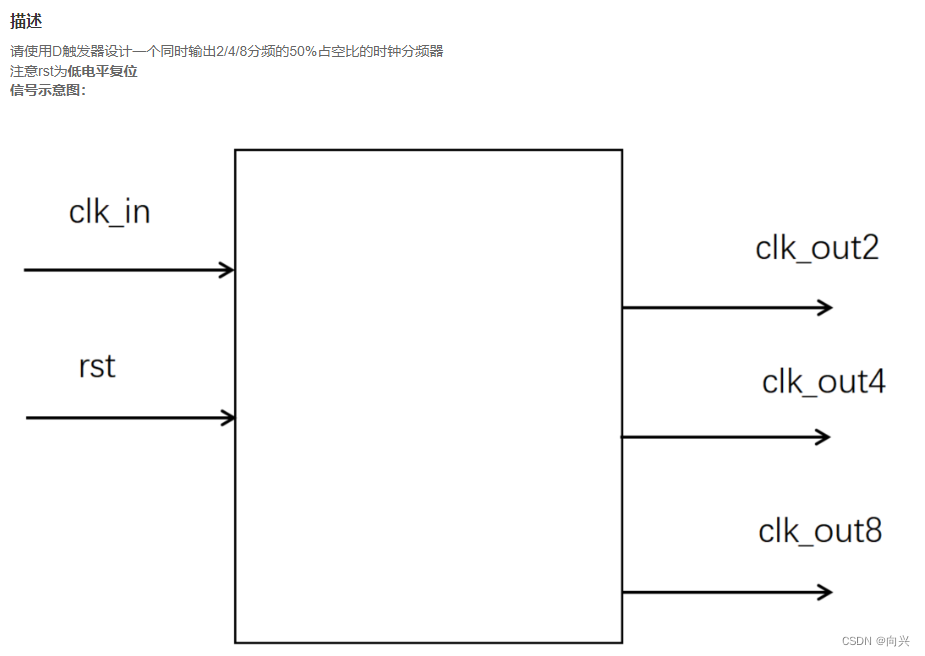

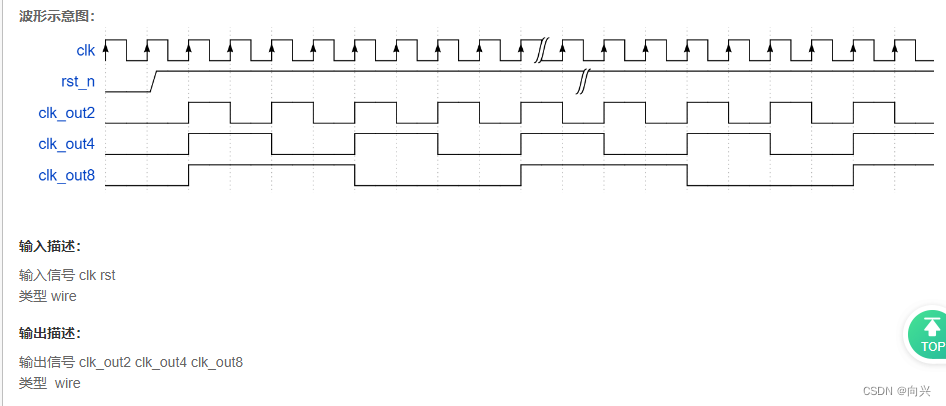

第一部分:题目要求及描述

第二部分:代码+前仿真验证

1,RTL代码

// 使用D触发器设计一个2、4、8分频 且 占空比是50% 的时钟分频器

module even_div(

input rst_n,

input clk,

output reg clk_out1,

output reg clk_out2,

output reg clk_out3

);

reg [3最后

以上就是失眠小霸王最近收集整理的关于VL37-时钟分频(偶数)的全部内容,更多相关VL37-时钟分频(偶数)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复