D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

而边沿触发的D触发器出现是为了提高触发器的可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于CLK的上升沿/下降沿到来时的输入信号状态。本次我们着重介绍边沿(上升沿)触发式D触发器,和负边沿(下降沿)触发式D触发器。

边沿(上升沿)触发式D触发器

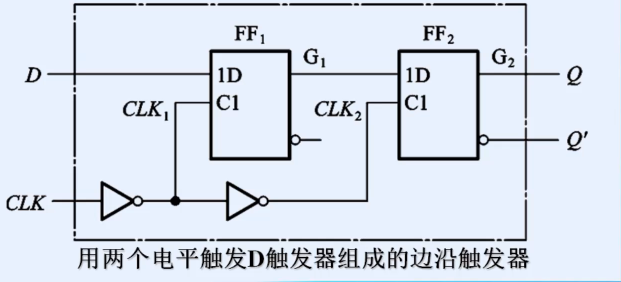

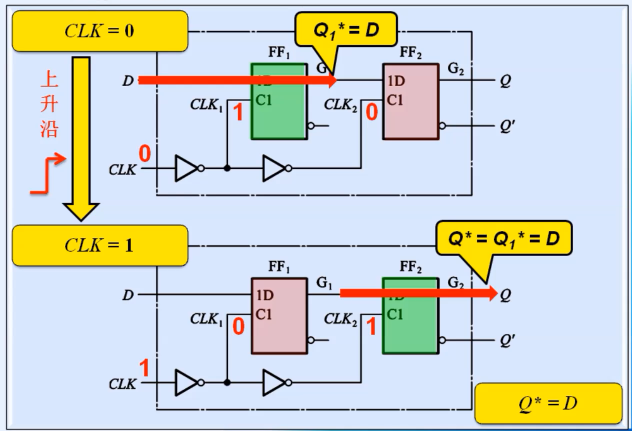

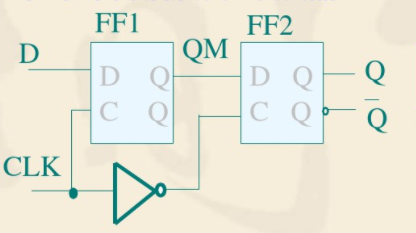

电路结构如下:

该锁存器结构为主锁存器(左)+从锁存器(右)

CLK1与CLK相异,CLK2与CLK相同。这样的结构致使主锁存器和从锁存器必将有一个截止,有一个运行。

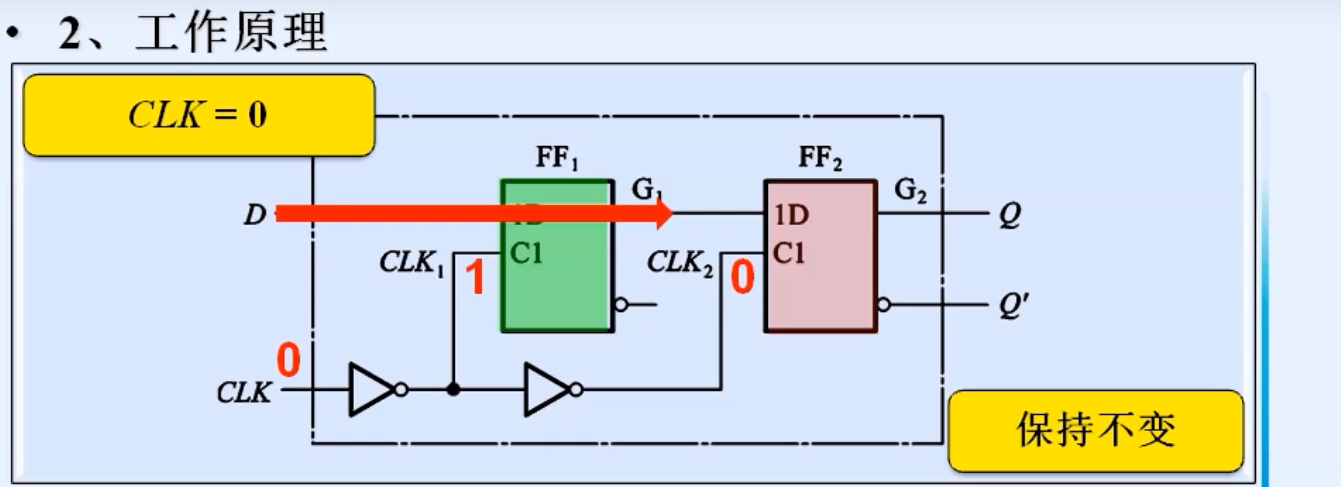

当CLK=0时,CLK1=1,CLK2=0,从锁存器截止,Q和Q'将保持不变

当CLK=1时,CLK1=0,CLK2=1,主锁存器截止,从锁存器运行,D信号无法进入主锁存器,进而影响不到从锁存器,Q和Q'保持不变

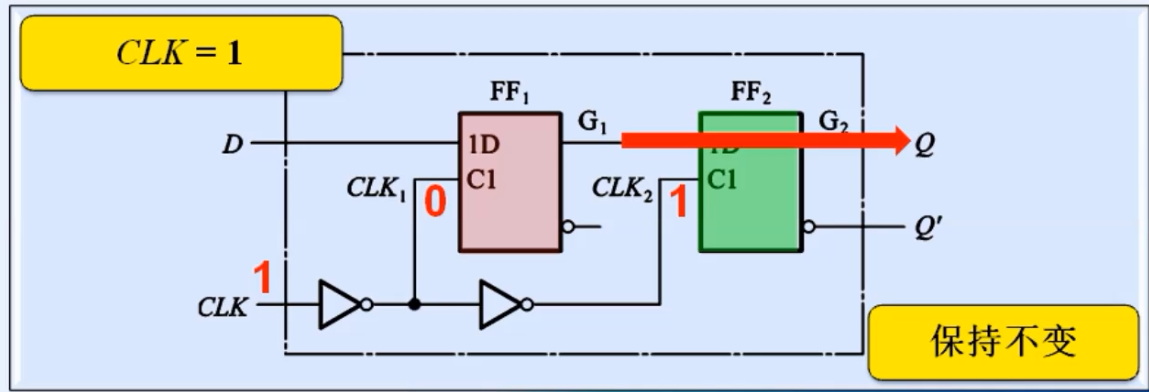

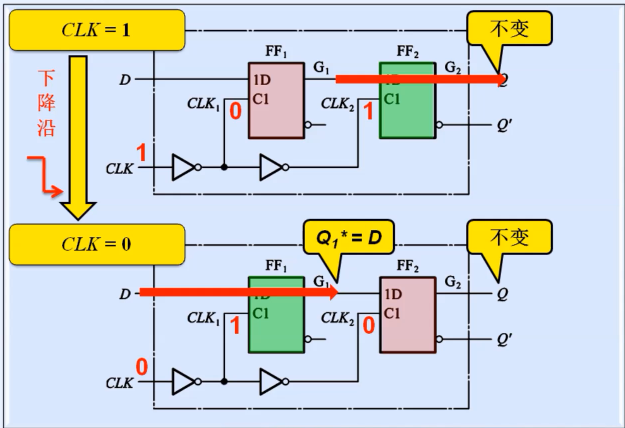

当CLK处于下降沿时,CLK快速从1跳向0,CLK=1主锁存器截止,输入D信号被阻断。CLK=0时,从锁存器截止,输入信号被阻断

当CLK处于上升沿时,CLK快速从0跳向1,CLK=0主锁存器运行,信号D输入主锁存器。CLK=1主锁存器截止(阻断后面信号输入),从锁存器运行,此时信号恰好进入从锁存器,输出 Q*=D

易知其功能表:

D CLK Q Q'

0 ↑ 0 1

1 ↑ 1 0

x x Q Q'

总的来说,对于边沿(上升)触发的D触发器,当CLK=↑时,Q输出为D。其余情况,Q不变。

负边沿(下降沿)触发式D触发器

同理,CLK1=CLK,CLK2=(CLK)'

CLK=0/1均有一锁存器截止

CLK为下降时,主从锁存器接续开启,信号得以传递,Q=D

易知其功能表:

D CLK Q Q'

0 ↓ 0 1

1 ↓ 1 0

x x Q Q'

总的来说,对于边沿(下降)触发的D触发器,当CLK=↓时,Q输出为D。其余情况,Q不变。

最后

以上就是可靠薯片最近收集整理的关于数字电路:边沿触发的D触发器简析的全部内容,更多相关数字电路:边沿触发内容请搜索靠谱客的其他文章。

发表评论 取消回复