在进行数字电路设计过程中,不论是ASICFPGA,系统时钟的可靠性,非常关键。设计不良的时钟在极限的温度、电压或制造工艺的偏差情况下将导致错误的行为。并且一般和时钟相关的问题,在调试过程中,难度较大、定位问题较难、花销很大。 所以今天我们就来谈一谈数字电路设计过程中的时钟问题。

时钟类型

通常时钟可分为如下四种类型:全局时钟、门控时钟、多级逻辑时钟和波动式时钟。但是在实际工作中,一个设计里面,往往都是多时钟系统,即包括上述四种时钟类型的任意组合。

全局时钟

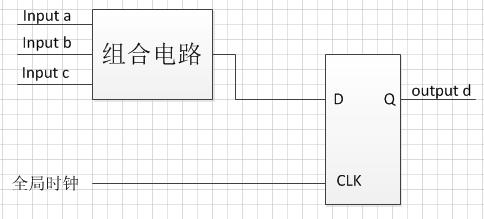

全局时钟(或同步时钟)指的是一个系统或者一颗芯片里面,所有的电路、触发器都使用同一个时钟。全局时钟是最简单和最可预测的时钟。

在进行数字电路设计过程中,一个理想的时钟方案是:由专用的全局时钟输入引脚,引入一个主时钟,去驱动电路里面的每一个触发器。只要可能就应尽量在设计项目中采用全局时钟。在一些逻辑器件里面(FPGA),都具有专门的全局时钟引脚,它直接连到器件中的每一个寄存器。

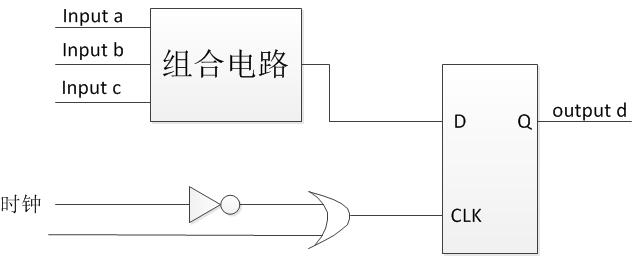

在图一中,给出一个全局时钟的例子。每个触发器的数据,都必须遵守建立时间(setup time)和保持时间(hold time)的约束条件。在ASIC设计中,setup/hold time时间取决于,项目所采用的工艺库,电路需要跑的的最高频率等等因素(关于setup time和hold time部分,牵扯到时序分析相关内容,今天的文章中,先不做讨论)。如果不满足setup/hold time,就不能保证寄存器能够捕获到正确的数据,导致电路的功能出现错误。

图一 全局时钟

门控时钟

全局门控,仅仅适合一些很小的项目。目前随着集成电路技术的发展,功能的增加,设计的复杂度提升,在大部分的应用中,一个项目采用一个全局时钟的设计,都是不可能的。

在使用可编程逻辑过程中,具有乘积项逻辑阵列时钟(即时钟是由逻辑产生的),允许任意函数单独地,控制各个触发器。所以就出现了阵列时钟。

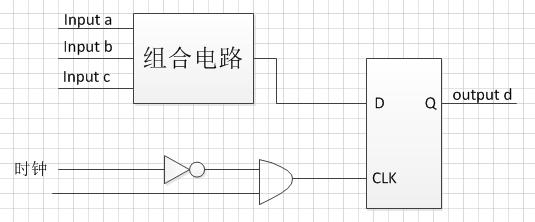

通常用阵列时钟构成门控时钟。门控时钟常常同微处理器接口有关,用地址线去控制写脉冲。然而,每当用组合函数钟控触发器时,通常都存在着门控时钟。如果符合下述条件,门控时钟可以象全局时钟一样可靠地工作:

- 驱动时钟的逻辑必须只包含一个“与”门或一个“或”门。如果采用任何附加逻在某些工作状态下,会出现竞争产生的毛刺。

- 逻辑门的一个输入作为实际的时钟,而该逻辑门的所有其它输入必须当成地址或控制线,它们遵守相对于时钟的建立和保持时间的约束。

图二 “与”门门控时钟

图三 “或”门门控时钟

另外,在ASIC设计过程中,随着设计复杂度增加,人们对功耗的要求越来越高,所以门控时钟现在作为一种有效的低功耗设计方法,被广泛的使用到设计过程中。这部分内容,后面在谈低功耗设计的文章中,我们再进行讨论,今天不再赘述。

多级逻辑时钟

当产生门控时钟的组合逻辑,超过一级(即超过单个的“与”门或“或”门)时,我们称之为多级逻辑时钟。

多级逻辑时钟使得,对设计的验证变得很困难,项目的可靠性变得很差。而且这种风险一般在仿真过程中,不会体现出来,但是在实际工作过程中,仍然存在着很大的危险。在通常情况之下,我们不推荐使用多级门控时钟。

波动式时钟

最后一种时钟电路是波动式,即一个触发器的输出用作另一个触发器的时钟输入。

如果设计得当,行波时钟的可靠性较好,可以和全局时钟相提并论。

但是,波动式时钟,把和电路有关的定时计算变得复杂化。行波时钟将导致在这条时钟链上各触发器的时钟之间,产生较大的时间偏移,并且可能会超出最坏情况下的setuphold time以及电路中时钟到输出的延时,使系统的实际速度下降。

小结

可靠性是进行时钟系统设计的首要考虑点,不能够在时钟上面有任何毛刺,并且为了降低可能的风险,要尽可能的使得时钟网络简单化。

最后

以上就是欢喜电源最近收集整理的关于数字电路技术可能出现的简答题_浅谈数字电路设计(ASICFPGA)中的时钟(CLOCK)...时钟类型全局时钟门控时钟多级逻辑时钟波动式时钟小结的全部内容,更多相关数字电路技术可能出现内容请搜索靠谱客的其他文章。

发表评论 取消回复