计数器

- 任务要求

- 相关知识

- 逻辑原理

- 同步16进制计数器真值表

- 编程要求

- 源代码

任务要求

根据所学的时序逻辑及数字电路的知识完成计数器的设计,验证同步16进制计数器的功能,进一步熟悉 Verilog HDL 文本设计流程, 掌握时序电路的设计仿真和测试方法。完善计数器电路的功能描述风格Verilog HDL 代码。

相关知识

逻辑原理

计数器能记忆输入脉冲的个数, 用于定时、分频、产生节拍脉冲及进行数字运算等等。 加法计数器每输入一个 CP 脉冲, 加法计数器的计数值加一。 十六进制计数即从 0000 一直计数到 1111;当计数到 1111 时,若再来一个 CP 脉冲,则回到 0000,同时产生进位 1。

同步 16 进制计数器设计采用 if-else 语句对计数器的输出分别进行赋值,能实现对输入脉冲的计数,并具有使能和异步清零功能。

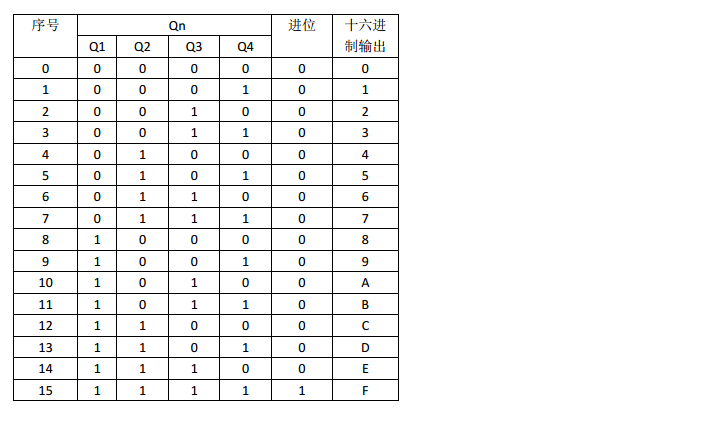

同步16进制计数器真值表

编程要求

为了完成计数的任务,完善编程模块设计代码,编写的程序要能根据不同的输入得到满足同步16进制计数器真值表的逻辑输出。

源代码

测试平台:EduCoder

module count_test(en,clk,clr,cout,outy);

input en,clk,clr;

output [3:0]outy;

output cout;

reg [3:0]outy;

always @ (posedge clk or posedge clr)

// 请在下面添加代码,完成16 进制计数器功能

/* Begin */

begin

if(clr) outy<=4'b0000;

else if(en)

begin if(outy==4'b1111) outy<=4'b0000;

else outy<=outy+1'b1;

end

end

assign cout=((outy==4'b1111)&en)?1:0;

/* End */

endmodule

觉得有帮助的可以点个赞再走哦!!

最后

以上就是沉静野狼最近收集整理的关于计数器——Verilog HDL语言任务要求相关知识编程要求源代码的全部内容,更多相关计数器——Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复