一. 用D触发器设计可重叠101序列检测器

1. 分析设计要求,列出全部可能状态

1. 未收到一个有效位(0):S0

2. 收到一个有效位(1):S1

3. 连续收到两个有效位(10):S2

4. 连续收到三个有效位(101):S3

5. 状态转移表如下

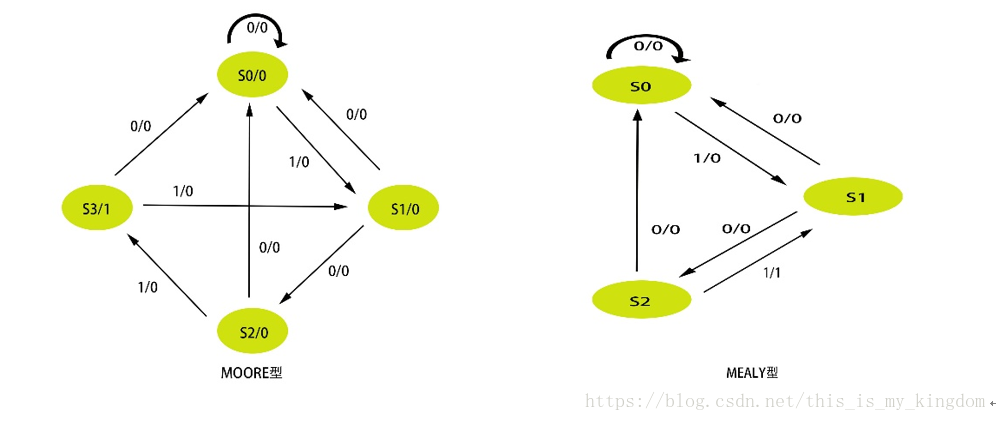

b) 画出状态转移图

c) HDL语言描述(verilog源代码)

i. MOORE型

输出只取决于当前的状态

源文件:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2018/05/13 16:50:14

// Design Name:

// Module Name: Checker

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module Checker(

input x, clk, rst,

output y

);

reg y;

//register to store the state and nextstate

reg [1:0] currentstate, nextstate;

//the code for states, can be changed

parameter S0 = 2'b00;

parameter S1 = 2'b01;

parameter S2 = 2'b10;

parameter S3 = 2'b11;

//the D_trigger to set the currentstate

always@(posedge clk or negedge rst)

begin

if(!rst)

currentstate <= S0;

else

currentstate <= nextstate;

end

//the nextstate

always@(currentstate or x or rst)

begin

if(!rst)

nextstate = S0;

else

begin

case(currentstate)

S0:nextstate = (x==1)?S1:S0;

S1:nextstate = (x==0)?S2:S0;

S2:nextstate = (x==1)?S3:S0;

S3:nextstate = (x==1)?S1:S0;

default:nextstate = S0;

endcase

end

end

//the output

always@(rst or currentstate)

begin

if(!rst)

y = 0;

else

case(currentstate)

S0:y = 0;

S1:y = 0;

S2:y = 0;

S3:y = 1;

default:y = 0;

endcase

end

endmodule

仿真文件:

`timescale 1ns / 1ps

`//

// Company:

// Engineer:

//

// Create Date: 2018/05/13 17:19:43

// Design Name:

// Module Name: Checker_testbench

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module Checker_testbench(

);

reg clk,rst;

reg x;

wire y;

Checker ch(.clk(clk),.rst(rst),.x(x),.y(y));

initial begin

clk = 0;

rst = 1;

#5 rst = 0;

#3 rst = 1;

#40 x = 1;

#40 x = 1;

#40 x = 0;

#40 x = 1;

#40 x = 1;

#40 x = 0;

#40 x = 0;

#40 x = 1;

#40 x = 0;

#40 x = 1;

#40 x = 0;

#40 x = 0;

#40 x = 1;

#40 x = 0;

#40 x = 0;

#40 x = 1;

#40 x = 0;

#40 x = 1;

#40 x = 0;

end

always #50 clk = ~clk;

endmodule

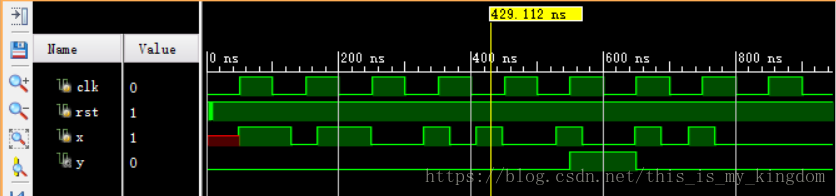

仿真时序图:

ii. MEALY型

源文件:

`timescale 1ns / 1ps

/

// Company:

// Engineer:

//

// Create Date: 2018/05/13 22:26:33

// Design Name:

// Module Name: Mealy

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

/

module Mealy(

input clk, rst, x,

output y

);

//make the output y to be a register

reg y;

/*temp_y: to store the temp value of y, becaouse the output y is decided

the state and the input*/

//currentstate and nextstae: the present state and the next state

reg temp_y;

reg[1:0] currentstate, nextstate;

//the state parameter

parameter S0 = 2'b00;

parameter S1 = 2'b01;

parameter S2 = 2'b10;

//the D_trigger to modify the state

//if reset, set the currentstate to S0

//else, set the currentstate to nextstate

always@(posedge clk or negedge rst)

begin

if(!rst)

currentstate <= S0;

else

currentstate <= nextstate;

end

//the modifier of state

always@(currentstate or x or rst)

begin

if(!rst)

nextstate <= S0;

else

begin

case(currentstate)

S0: nextstate = (x==1)?S1:S0;

S1: nextstate = (x==0)?S2:S0;

S2: nextstate = (x==1)?S1:S0;

default: nextstate = S0;

endcase

end

end

//the temp output

always@(rst or currentstate or x)

begin

if(!rst)

temp_y = 0;

else

case(currentstate)

S0: temp_y = 0;

S1: temp_y = 0;

S2: temp_y = (x==1)?1:0;

default: temp_y = 0;

endcase

end

//the real output

always@(posedge clk or negedge rst)

begin

//reset

if(!rst)

y <= 0;

else

begin

//

if((temp_y == 1)&&(nextstate == S1))

y <= 1;

else

y <= 0;

end

end

endmodule

仿真文件:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2018/05/13 22:59:56

// Design Name:

// Module Name: Mealy_testbench

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module Mealy_testbench(

);

reg x, clk, rst;

wire y;

Mealy meal(.x(x),.clk(clk),.rst(rst),.y(y));

initial begin

clk = 0;

rst = 1;

#5 rst = 0;

#3 rst = 1;

#40 x = 1;

#40 x = 1;

#40 x = 0;

#40 x = 0;

#40 x = 1;

#40 x = 0;

#40 x = 0;

#40 x = 1;

#40 x = 0;

#40 x = 0;

#40 x = 0;

#40 x = 0;

#40 x = 1;

#40 x = 0;

#40 x = 0;

#40 x = 1;

#40 x = 0;

#40 x = 1;

#40 x = 0;

end

always #50 clk = ~clk;

endmodule

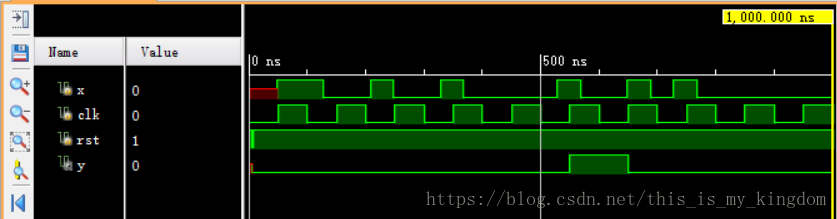

仿真波形图:

最后

以上就是坦率豌豆最近收集整理的关于设计MOORE型和MEALY型的可重叠101序列检测器的全部内容,更多相关设计MOORE型和MEALY型内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复