我是靠谱客的博主 坚强咖啡豆,这篇文章主要介绍【Verilog】移位寄存器总结:移位寄存器、算数移位寄存器、线性反馈移位寄存器(LFSR)一、移位寄存器二、算数移位寄存器三、 线性反馈移位寄存器LFSR(linear feedback shift register ),现在分享给大家,希望可以做个参考。

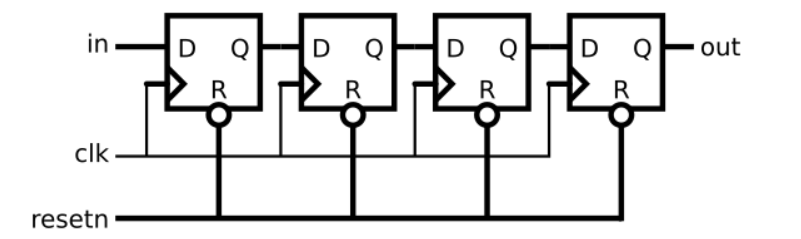

一、移位寄存器

module top_module(

input clk,

input resetn,

input in,

output out

);

reg [3:0] q;

always @(posedge clk) begin

if (resetn == 1'b0) begin

q <= 4'd0;

end

else begin

q <= {in,q[3:1]};//右移

end

end

assign out = q[0];

endmodule

二、算数移位寄存器

- 算数左移:和逻辑左移一样。空出来的位用0补;

- 算数右移:算术移位,也就是包含符号位的移位,对于正数来说,最高位为0,对于负数来说,最高位为1,所以进行算术移位时,如果是左移,那不用管符号位的问题,如果是右移,就要将符号位补在高位。比如:5位数字11000算术右移1为11100,而逻辑右移将产生01100;5位数字01000算术右移1等于00100,而逻辑右移将产生相同的结果,因为原始数字是非负的。

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0]q

);

always @(posedge clk ) begin

if (load) begin

q <= data;

end

else if (ena) begin

case(amount)

2'b00:q <= q<<1; //左移一位

2'b01:q <= q<<8; //左移八位

2'b10:begin //右移一位

if(q[63] == 0)begin

q <= q>>1;

end

else begin

q <= {1'b1,q[63:1]};

end

end

2'b11:begin //右移八位

if(q[63] == 0)begin

q <= q >> 8;

end

else begin

q <= {8'b1111_1111,q[63:8]};

end

end

endcase

end

end

endmodule

三、 线性反馈移位寄存器LFSR(linear feedback shift register )

相关参考文章

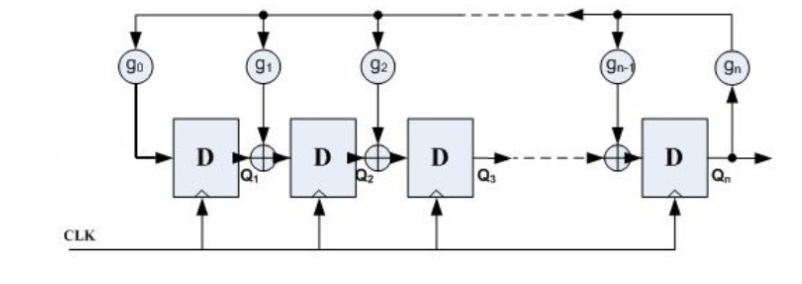

LFSR用于产生可重复的伪随机序列PRBS,。如图所示。其中gn为反馈系数,取值只能为0或1,取为0时表明不存在该反馈之路,取为1时表明存在该反馈之路;这里的反馈系数决定了产生随机数的算法的不同。

- 组成: 由n级触发器和一些异或门组成。

- LFSR初始值: 伪随机序列的种子。

- 抽头: 影响下一个状态的比特位。

- 含有N个触发器的LFSR电路最多可以产生2的n次方减1个序列。

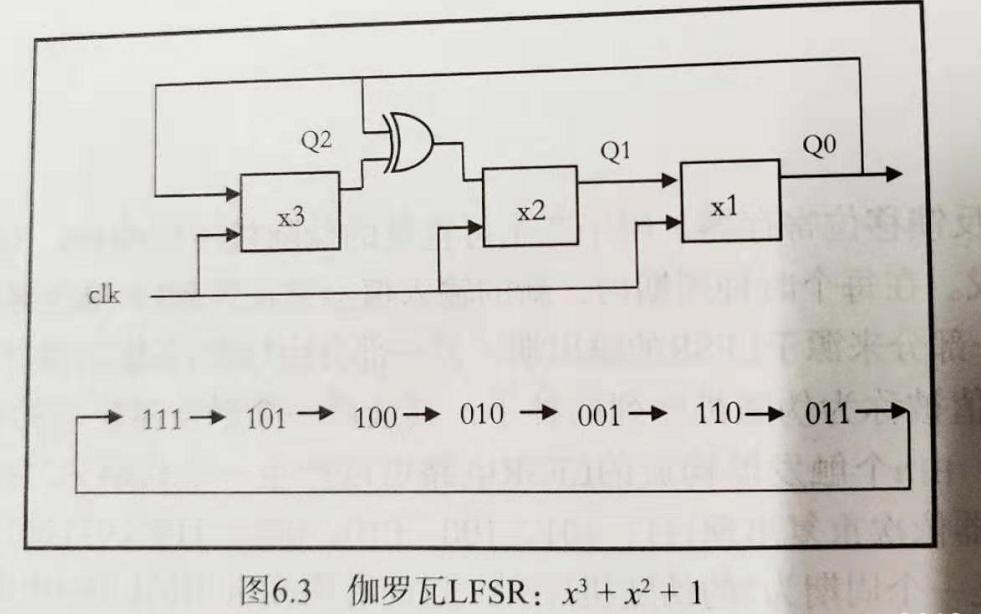

1、伽罗瓦LFSR(Galois LFSR)

伽罗瓦LFSR是一到多型的LFSR,即最后一个触发器的输出 与抽头序列对应位置触发器前一级触发器的输出 相异或逻辑来驱动多个抽头序列对应位置触发器的输入,如下图所示。

Galois LFSR:其中抽头的位置与输出位异或,以产生其下一个值。如果仔细选择抽头位置,则LFSR可以设置为“最大长度”。n位的最大长度LFSR有2^(n-1)个状态(永远不会达到全零状态)。

- 例子:构建一个32位Galois LFSR,在32、22、2和1位的位置处使用抽头。

module top_module(

input clk,

input reset,

output reg [31:0]q

);

reg [31:0] q_next;

integer i;

always @(*) begin

for(i = 0;i<32;i++)begin

if(i == 0 ||i == 1||i == 21)begin

q_next[i] <= q[i+1] ^ q[0];

end

else if (i == 31) begin

q_next[i] <= 1'b0 ^ q[0];

end

else begin

q_next[i] <= q[i+1];

end

end

end

always @(posedge clk) begin

if (reset) begin

q <= 32'h1;

end

else begin

q <= q_next;

end

end

endmodule

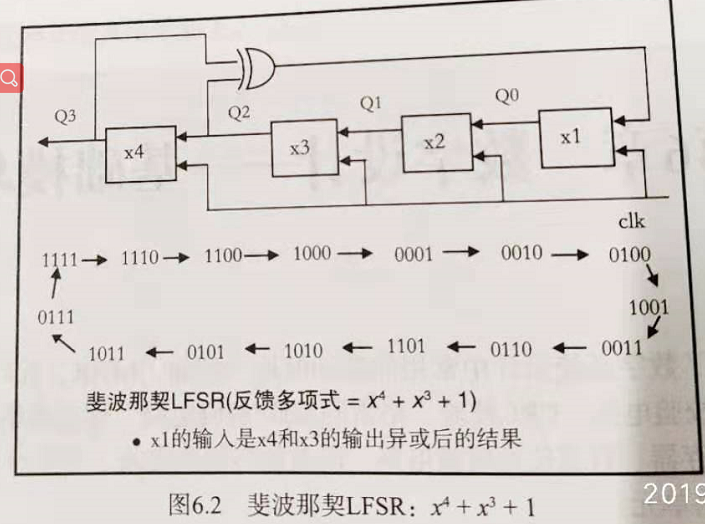

2、斐波那契LFSR

斐波那契LFSR也可以称为多到一型LFSR,即抽头序列对应bit位置的多个触发器的输出通过异或逻辑来驱动一个触发器的输入。如下图所示。

最后

以上就是坚强咖啡豆最近收集整理的关于【Verilog】移位寄存器总结:移位寄存器、算数移位寄存器、线性反馈移位寄存器(LFSR)一、移位寄存器二、算数移位寄存器三、 线性反馈移位寄存器LFSR(linear feedback shift register )的全部内容,更多相关【Verilog】移位寄存器总结:移位寄存器、算数移位寄存器、线性反馈移位寄存器(LFSR)一、移位寄存器二、算数移位寄存器三、内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复