移位寄存器的设计:

有三个模式:

- 左循环

- 右循环

- 加载预置的数

具体功能可以根据需要对程序做出一些修改即可

代码如下:

module shift1(clk,D,MD,QB);

input clk; //时钟信号

input [7:0] D; //预置数,可以在测试文件中预置,或者在板子上选取

input [1:0] MD; //模式选择数值

output [7:0] QB; //输出的数值

reg [7:0] REG; //定义寄存器类型

always @ ( posedge clk ) begin //对时钟信号上升沿敏感

case (MD) //根据MD的数值,选择模式

2'b01: begin REG[0] <= REG[7] ; REG[7:1] <= REG[6:0]; end //循环左移

2'b10: begin REG[7] <= REG[0] ; REG[6:0] <= REG[7:1]; end //循环右移

2'b00: begin REG <= D; end //加载预置的数值

endcase

end

assign QB[7:0] = REG[7:0]; //把REG中的数值赋给QB

endmodule

测试文件

module shift1_tb();

reg clk;

reg [7:0] D;

reg [1:0] MD;

wire [7:0] QB; //输出

initial

begin //初始化

clk = 0;

D = 8'b11110000; //初始化待移数值(这样赋值只是为了最后好观察波形)

MD = 2'b00; //以置数模式开始

end

always #10 clk = ~clk; //时钟信号

always #100 MD = MD+1;//循环改变模式,

shift1 test( .clk(clk),

.D(D),

.MD(MD),

.QB(QB)

);

endmodule

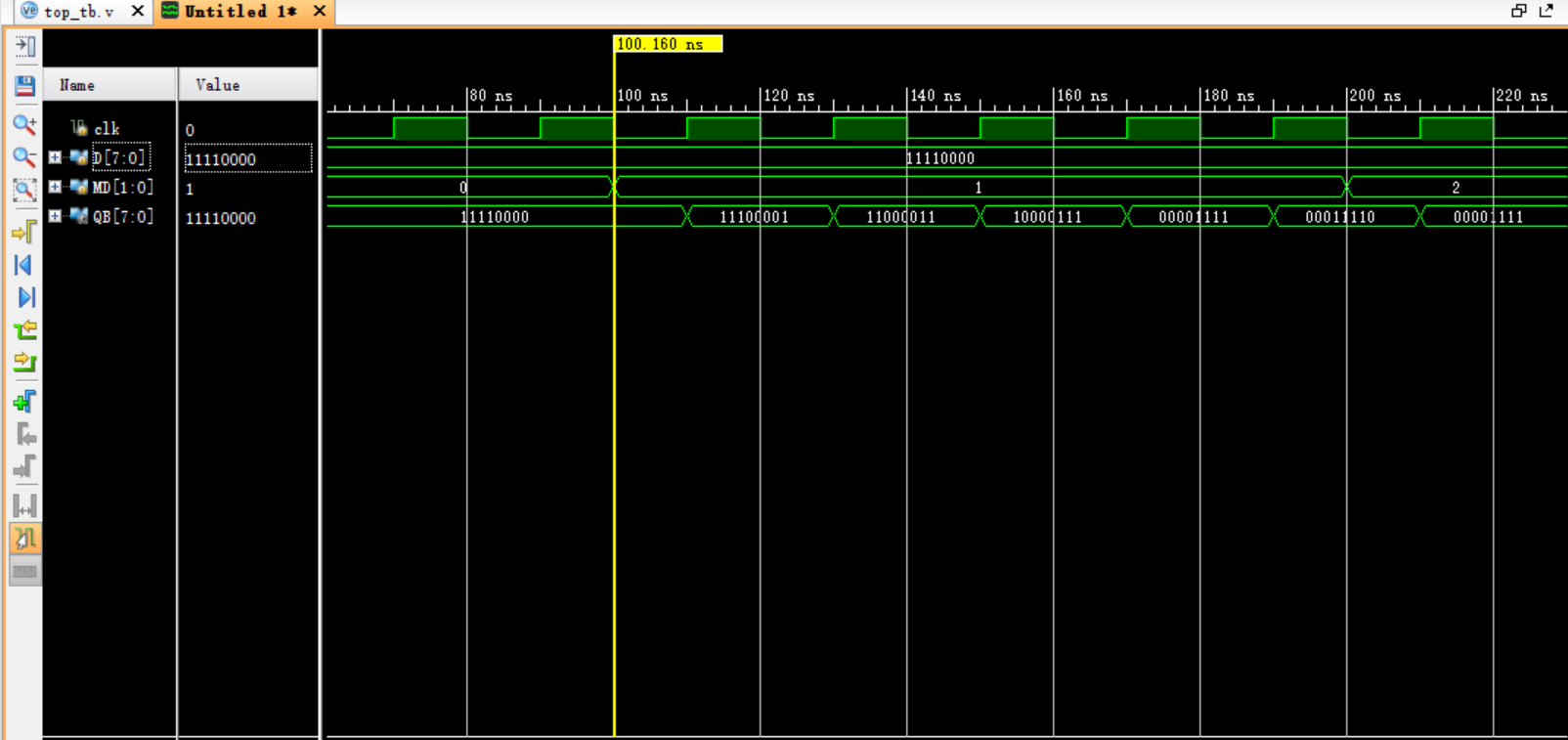

这里图形没有从一开始截取,而是选择能看到三个模式效果的时间段,MD=0时,一直在加载预置数,输出等于D 11110000.MD=1时,开始循环左移。MD=2时,开始循环右移。

这里图形没有从一开始截取,而是选择能看到三个模式效果的时间段,MD=0时,一直在加载预置数,输出等于D 11110000.MD=1时,开始循环左移。MD=2时,开始循环右移。

基本的设计就是这样子,可以在它的基础上进行改进,以达到大家需要的功能,比如在shift1中的case加几个模式。D的值也可以随便赋值。

我也写了几篇关于Veirlog的文章,感兴趣的同学可以去看看。该模块链接如下:

https://blog.csdn.net/weixin_43877139/article/category/8778400

最后

以上就是傲娇蜡烛最近收集整理的关于Veirlog学习记录(3),移位寄存器(左循环,右循环)的实现的全部内容,更多相关Veirlog学习记录(3),移位寄存器(左循环,右循环)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复