实验报告

日期:2017.11.26 指导老师:窦老师

院系:信息院, 年级班级:17计算机

实验课程名称:数字逻辑

实验项目名称:设计‘101’序列检测器(可重复)

实验要求:

- 验证RS/D/JK/T触发器的功能;

- 熟悉逻辑分析仪,字发生器的使用;

一. 实验步骤:

(这里没有不确定的状态,所以是完全确定的同步时序电路的设计)

- 形成原始的状态图和状态表

这里是采用的Mealy型同步时序逻辑电路来实现序列检测器的功能

初始状态: A

状态1 : B

状态2 : C

|

现态

| 次态/输出 | |

| X=0 | X=1 | |

| A | A/0 | B/0 |

| B | C/0 | B/0 |

| C | A/0 | B/1 |

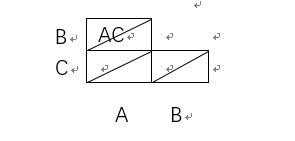

2. 状态化简(用隐含表)

由以上的隐含表可知此状态已是最简

3.状态编码

有三条规则可以得到

- AC

- AB,BC

- AB

优先级1>2>3的顺序编码

由此可得

A--00

B--01

C--10

二进制的状态图如下

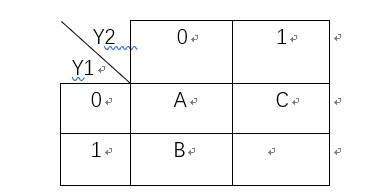

| 现态 Y2/Y1 | 次态y2’y1’/输出 | |

| X=0 | X=1 | |

| 0 0 | 00/0 | 01/0 |

| 0 1 | 10/0 | 01/0 |

| 1 0 | 00/0 | 01/1 |

4.确定激励函数和输出函数,并画出逻辑电路图

| 输入和现态 | 激励函数 | 输出函数 | |||||

| X | y2 | y1 | J2 | K2 | J1 | K1 | Z |

| 0 | 0 | 0 | 0 | d | 0 | d | 0 |

| 0 | 0 | 1 | 1 | d | d | 1 | 0 |

| 0 | 1 | 0 | d | 1 | 0 | d | 0 |

| 1 | 0 | 0 | 0 | d | 1 | d | 0 |

| 1 | 0 | 1 | 0 | d | d | 0 | 0 |

| 1 | 1 | 0 | d | 1 | 1 | d | 1 |

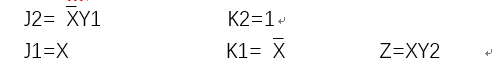

经过库洛图化简后可得激励函数和输出函数的最简表达式:

在草稿纸上画出草图。

5.在 Ni Multisim上面实现电路的仿真下面附上自己实现的草图

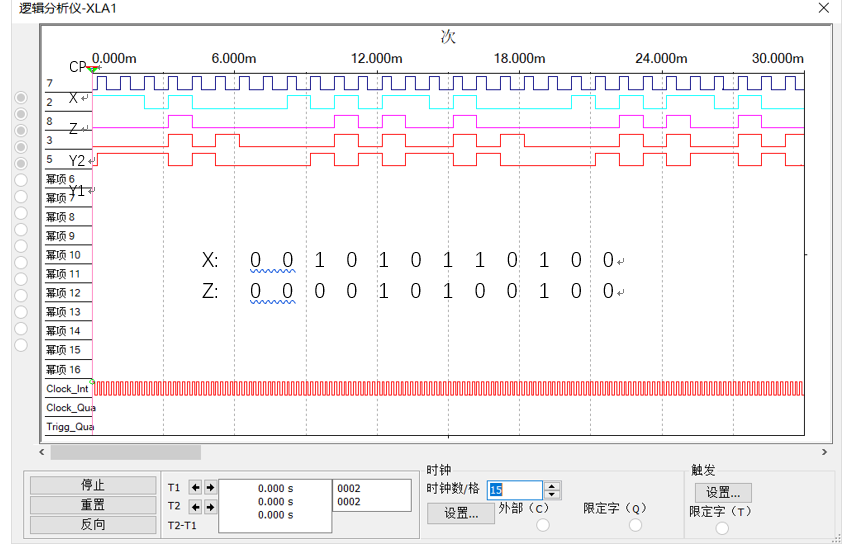

(输入端用自发生器,CP接时钟脉冲发生器,输出端接逻辑分析仪来显示波形)

6.实验现象的记录,采用截屏波形的方法

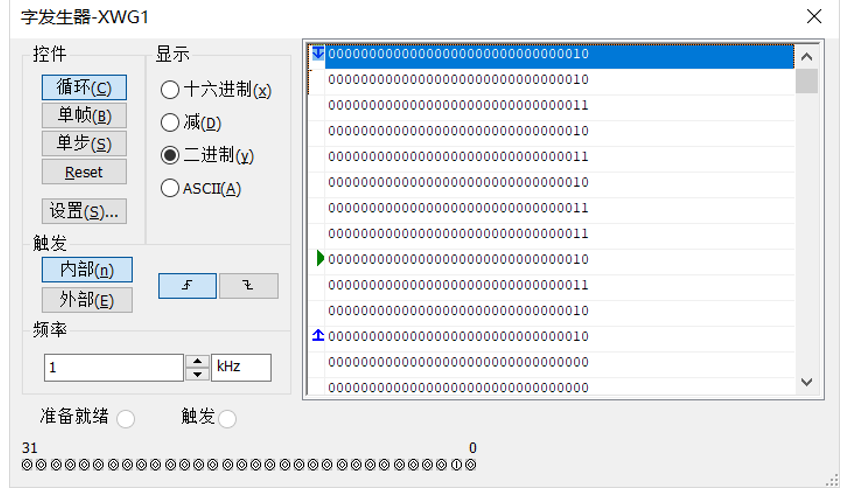

字发生器采用的序列如下:

逻辑分析仪的结果波形如下

二.实验总结与心得

在实验中我们主要遇到了以下的几个问题:

1.为什么逻辑分析仪的CP没有波形

我们以前是把字发生器,时钟脉冲和逻辑分析仪的的频率调成一致,结果一直没有波形,

后来问老师才知道,没有必要把频率调成全部一致,但是其他组的成员调成一致后有波形(很奇怪)。

2. 一开始我们用的是Moore型的同步时序电路得出的波形正好慢了一格

问了老师后才知道可能是因为是CP的下降沿导致的波形的延后,为了做出完美的图,我们果断的采用了Meary型的同步时序电路,果然就没有了问题,推荐一下Meary的电路。

3.改成Meary的电路后还是没有出现想要的波形,问了同学才知道是步骤4确定激励函数和输出函数的过程中出错了(把d 1 写成了d 0),导致了K2求错了,十分感谢他的帮助,也希望大家能够更加仔细,不要像我一样,不然找起错误来真的让人抓狂。

4.还有感谢老师的帮助,老师上课讲得简单易懂,原本对我来说十分抽象的电路,触发器什么的在这次的实验下,竟然都没有那么陌生了,对自己的提升还是很满意的。

最后

以上就是平淡铃铛最近收集整理的关于Ni Multisim 101序列检测器实验报告实验报告的全部内容,更多相关Ni内容请搜索靠谱客的其他文章。

发表评论 取消回复