目录

1 SHIFT4

2 LEFT/RIGHT ROTATOR

3 LEFT/RIGHT ARRITHMETIC SHIFT BY 1 OR 8

4 5-BIT LFSR

5 3-BIT LFSR

6 32-BIT LFSR

7 SHIFT REGISTER-1

8 SHIFT REGISTER-2

9 3-INPUT LUT

1 SHIFT4

Build a 4-bit shift register (right shift), with asynchronous reset, synchronous load, and enable.

- areset: Resets shift register to zero.

- load: Loads shift register with data[3:0] instead of shifting.

- ena: Shift right (q[3] becomes zero, q[0] is shifted out and disappears).

- q: The contents of the shift register.

- (areset:将移位寄存器重置为零。

load:用数据[3:0]加载移位寄存器,而不是移位。

ena:向右移动(q[3]变为零,q[0]移出并消失)。

q:移位寄存器的内容。)

If both the load and ena inputs are asserted (1), the load input has higher priority.

COEERCT:

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,

input ena,

input [3:0] data,

output reg [3:0] q);

always@(posedge clk, posedge areset)

begin

if(areset)

q<=0;

else if(load)

begin

q<=data;

end

else if(ena)

begin

q[0]=q[1];

q[1]=q[2];

q[2]=q[3];

q[3]=0;

end

else

begin

q<=q;

end

end

endmodule

2 LEFT/RIGHT ROTATOR

Build a 100-bit left/right rotator, with synchronous load and left/right enable. A rotator shifts-in the shifted-out bit from the other end of the register, unlike a shifter that discards the shifted-out bit and shifts in a zero. If enabled, a rotator rotates the bits around and does not modify/discard them.

- load: Loads shift register with data[99:0] instead of rotating.

- ena[1:0]: Chooses whether and which direction to rotate.

- 2'b01 rotates right by one bit

- 2'b10 rotates left by one bit

- 2'b00 and 2'b11 do not rotate.

- q: The contents of the rotator.

- (load:用数据[99:0]加载移位寄存器,而不是旋转。

ena[1:0]:选择是否旋转以及旋转的方向。

2'b01向右旋转1位

2'b10向左旋转1位

2'b00和2'b11不旋转。

q:旋转器的内容。)

CORRECT:

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @(posedge clk)

begin

if(load)

q<=data;

else

case(ena)

2'b01:q<={q[0],q[99:1]};

2'b10:q<={q[98:0],q[99]};

2'b00:q<=q;

2'b11:q<=q;

endcase

end

endmodule

3 LEFT/RIGHT ARRITHMETIC SHIFT BY 1 OR 8

Build a 64-bit arithmetic shift register, with synchronous load. The shifter can shift both left and right, and by 1 or 8 bit positions, selected by amount.

An arithmetic right shift shifts in the sign bit of the number in the shift register (q[63] in this case) instead of zero as done by a logical right shift. Another way of thinking about an arithmetic right shift is that it assumes the number being shifted is signed and preserves the sign, so that arithmetic right shift divides a signed number by a power of two.

There is no difference between logical and arithmetic left shifts.

- load: Loads shift register with data[63:0] instead of shifting.

- ena: Chooses whether to shift.

- amount: Chooses which direction and how much to shift.

- 2'b00: shift left by 1 bit.

- 2'b01: shift left by 8 bits.

- 2'b10: shift right by 1 bit.

- 2'b11: shift right by 8 bits.

- q: The contents of the shifter.

(load:用数据[63:0]加载移位寄存器,而不是移位。

ena:选择是否转移。

amount:选择移动的方向和幅度。

2'b00:左移1位。

2'b01:左移8位。

2'b10:右移1位。

2'b11:右移8位。

q:移位器的内容。)

HINT:

A 5-bit number 11000 arithmetic right-shifted by 1 is 11100, while a logical right shift would produce 01100.Similarly, a 5-bit number 01000 arithmetic right-shifted by 1 is 00100, and a logical right shift would produce the same result, because the original number was non-negative.

(5位数11000的算术右移1是11100,而逻辑右移将产生01100。类似地,5位数字01000算术右移1是00100,逻辑右移将产生相同的结果,因为原始数字是非负的。)

CORRECT:

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always @(posedge clk)

begin

if(load)

q<=data;

else if(ena)begin

case(amount)

2'b00:q<={q[62:0],1'b0};

2'b01:q<={q[55:0],8'b0};

2'b10:q<={q[63],q[63:1]};

2'b11:q<={{8{q[63]}},q[63:8]};

endcase

end

else

q<=q;

end

endmodule

ERRO:

module top_module(

input clk,

input load,

input ena,

input [1:0] amount,

input [63:0] data,

output reg [63:0] q);

always @(posedge clk)

begin

if(load)

q<=data;

else if(ena)begin

case(amount)

2'b00:q<={q[62:0],1'b0};

2'b01:q<={q[55:0],8'b0};

2'b10:q<={1'b0,q[63:1]};

2'b11:q<={8'b0,q[63:8]};

endcase

end

else

q<=q;

end

endmodule

4 5-BIT LFSR

A linear feedback shift register is a shift register usually with a few XOR gates to produce the next state of the shift register. A Galois LFSR is one particular arrangement where bit positions with a "tap" are XORed with the output bit to produce its next value, while bit positions without a tap shift. If the taps positions are carefully chosen, the LFSR can be made to be "maximum-length". A maximum-length LFSR of n bits cycles through 2n-1 states before repeating (the all-zero state is never reached).(线性反馈移位寄存器是一种移位寄存器,通常带有几个异或门来产生移位寄存器的下一个状态。伽罗瓦LFSR是一种特殊的安排,其中带有“抽头”的位位与输出位进行xoror以产生下一个值,而没有抽头移位的位位。如果丝锥的位置被仔细选择,LFSR可以被制成“最大长度”。最大长度为n位的LFSR在重复之前经过2n-1个状态(永远不会达到全零状态)。)

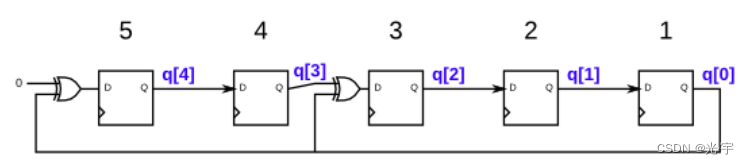

The following diagram shows a 5-bit maximal-length Galois LFSR with taps at bit positions 5 and 3. (Tap positions are usually numbered starting from 1). Note that I drew the XOR gate at position 5 for consistency, but one of the XOR gate inputs is 0.(下图显示了一个5位最大长度的Galois LFSR,在第5位和第3位处有丝锥。(点击位置通常从1开始编号)。注意,为了保持一致性,我在位置5处画了异或门,但其中一个异或门输入是0。)

Build this LFSR. The reset should reset the LFSR to 1.

HINT:

The first few states starting at 1 are 00001, 10100, 01010, 00101, ... The LFSR should cycle through 31 states before returning to 00001.

CORRECT:

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output reg[4:0] q

);

always@(posedge clk )

begin

if(reset)

begin

q<=5'h1;

end

else

begin

q[4]<=1'b0 ^ q[0];

q[3]<=q[4];

q[2]<=q[3] ^ q[0];

q[1]<=q[2];

q[0]<=q[1];

end

end

endmodule

ERRO:

module top_module(

input clk,

input reset, // Active-high synchronous reset to 5'h1

output reg[4:0] q

);

always@(posedge clk or posedge reset)//reset不用非得一到上升沿就起作用

begin

if(reset)

begin

q<=5'h1;

end

else

begin

q[4]<=1'b0 ^ q[0];

q[3]<=q[4];

q[2]<=q[3] ^ q[0];

q[1]<=q[2];

q[0]<=q[1];

end

end

endmodule

5 3-BIT LFSR

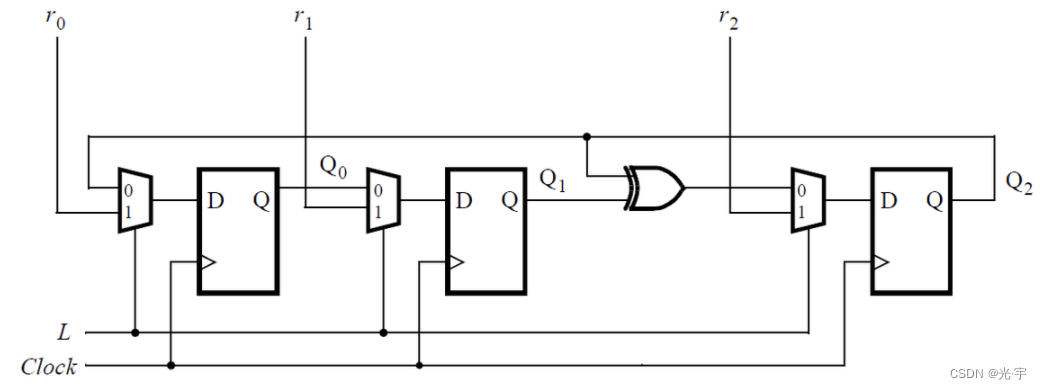

Taken from 2015 midterm question 5. See also the first part of this question: mt2015_muxdff

Write the Verilog code for this sequential circuit (Submodules are ok, but the top-level must be named top_module). Assume that you are going to implement the circuit on the DE1-SoC board. Connect the R inputs to the SW switches, connect Clock to KEY[0], and L to KEY[1]. Connect the Q outputs to the red lights LEDR.

HINT:

This circuit is an example of a Linear Feedback Shift Register (LFSR). A maximum-period LFSR can be used to generate pseudorandom numbers, as it cycles through 2n-1 combinations before repeating. The all-zeros combination does not appear in this sequence.

该电路是线性反馈移位寄存器(LFSR)的一个例子。最大周期LFSR可用于生成伪随机数,因为它在重复之前通过2n-1个组合循环。全零组合不会出现在这个序列中。

CORRECT:

module top_module (

input [2:0] SW, // R

input [1:0] KEY, // L and clk

output [2:0] LEDR); // Q

wire clk;

assign clk = KEY[0];

always @(posedge clk)begin

if(KEY[1])begin

LEDR[0] <= SW[0];

LEDR[1] <= SW[1];

LEDR[2] <= SW[2];

end

else begin

LEDR[0] <= LEDR[2];

LEDR[1] <= LEDR[0];

LEDR[2] <= LEDR[2] ^ LEDR[1];

end

end

endmodule

6 32-BIT LFSR

See Lfsr5 for explanations.

Build a 32-bit Galois LFSR with taps at bit positions 32, 22, 2, and 1.

HINT:

This is long enough that you'd want to use vectors, not 32 instantiations of DFFs.

CORRECT:

module top_module(

input clk,

input reset, // Active-high synchronous reset to 32'h1

output [31:0] q

);

integer i;

always @(posedge clk)begin

if(reset)begin

q <= 32'h1;

end

else begin

for(i=0;i<32;i++)begin

if((i==21)||(i==1)||(i==0))begin

q[i] <= q[i+1] ^ q[0];

end

else if(i==31)begin

q[31] <= 1'b0 ^ q[0];

end

else begin

q[i] <= q[i+1];

end

end

end

end

endmodule

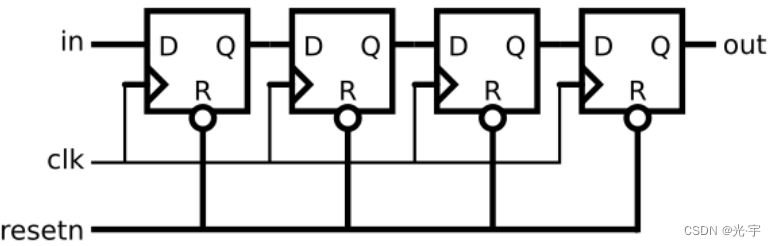

7 SHIFT REGISTER-1

Implement the following circuit:

CORRECT:

module top_module (

input clk,

input resetn, // synchronous reset

input in,

output out);

reg [3:0] tmp;

assign out = tmp[3];

always @(posedge clk)begin

if(!resetn)begin

tmp <= 4'h0;

end

else begin

tmp <= {tmp[2:0],in};

end

end

endmodule

8 SHIFT REGISTER-2

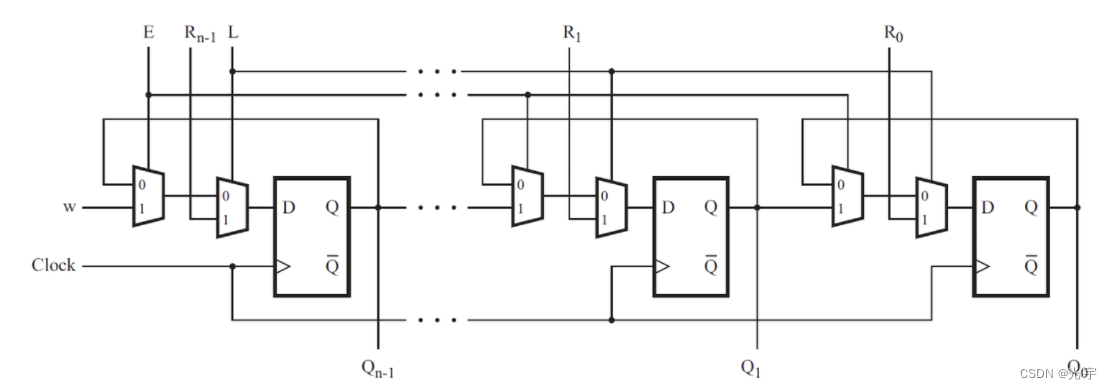

Consider the n-bit shift register circuit shown below:

Write a top-level Verilog module (named top_module) for the shift register, assuming that n = 4. Instantiate four copies of your MUXDFF subcircuit in your top-level module. Assume that you are going to implement the circuit on the DE2 board.(为移位寄存器编写一个顶级Verilog模块(名为top_module),假设n = 4。在顶层模块中实例化MUXDFF子电路的四个副本。假设您将在DE2板上实现电路。)

- Connect the R inputs to the SW switches,

- clk to KEY[0],

- E to KEY[1],

- L to KEY[2], and

- w to KEY[3].

- Connect the outputs to the red lights LEDR[3:0].

(Reuse your MUXDFF from exams/2014_q4a.)

CORRECT:

module top_module (

input [3:0] SW,

input [3:0] KEY,

output [3:0] LEDR

);

MUXDFF u1(.clk(KEY[0]),

.w(KEY[3]),

.R(SW[3]),

.E(KEY[1]),

.L(KEY[2]),

.Q(LEDR[3]));

MUXDFF u2(.clk(KEY[0]),

.w(LEDR[3]),

.R(SW[2]),

.E(KEY[1]),

.L(KEY[2]),

.Q(LEDR[2]));

MUXDFF u3(.clk(KEY[0]),

.w(LEDR[2]),

.R(SW[1]),

.E(KEY[1]),

.L(KEY[2]),

.Q(LEDR[1]));

MUXDFF u4(.clk(KEY[0]),

.w(LEDR[1]),

.R(SW[0]),

.E(KEY[1]),

.L(KEY[2]),

.Q(LEDR[0]));

endmodule

module MUXDFF (

input clk,

input w,R,E,L,

output Q

);

wire tmp;

assign tmp = E ? w : Q;

always @(posedge clk)begin

Q <= L? R : tmp;

end

endmodule

9 3-INPUT LUT

In this question, you will design a circuit for an 8x1 memory, where writing to the memory is accomplished by shifting-in bits, and reading is "random access", as in a typical RAM. You will then use the circuit to realize a 3-input logic function.(在这个问题中,您将为8x1存储器设计一个电路,其中写入存储器是通过移位位来完成的,而读取是“随机访问”,就像在典型的RAM中一样。然后使用该电路实现3输入逻辑功能。)

First, create an 8-bit shift register with 8 D-type flip-flops. Label the flip-flop outputs from Q[0]...Q[7]. The shift register input should be called S, which feeds the input of Q[0] (MSB is shifted in first). The enable input controls whether to shift. Then, extend the circuit to have 3 additional inputs A,B,C and an output Z. The circuit's behaviour should be as follows: when ABC is 000, Z=Q[0], when ABC is 001, Z=Q[1], and so on. Your circuit should contain ONLY the 8-bit shift register, and multiplexers. (Aside: this circuit is called a 3-input look-up-table (LUT)).(首先,创建一个带有8个d型触发器的8位移位寄存器。标记从Q[0]到Q[7]的触发器输出。移位寄存器输入应该称为S,它提供Q[0]的输入(MSB首先移位)。enable输入控制是否移位。然后,扩展电路,增加3个输入A、B、C和一个输出Z。电路的行为应该如下:当ABC为000时,Z=Q[0],当ABC为001时,Z=Q[1],以此类推。你的电路应该只包含8位移位寄存器和多路复用器。(题外话:这个电路被称为3输入查找表(LUT))。)

CORRECT:

module top_module (

input clk,

input enable,

input S,

input A, B, C,

output Z );

reg [7:0] Q;

always @(posedge clk)begin

if(enable)begin

Q <= {Q[6:0],S};

end

else begin

Q <= Q;

end

end

assign Z = Q[{A,B,C}];

endmodule

最后

以上就是寂寞往事最近收集整理的关于HDLbits exercises 12(SHIFT REGISTER全部题)1\ SHIFT42\ LEFT/RIGHT ROTATOR3\ LEFT/RIGHT ARRITHMETIC SHIFT BY 1 OR 84\ 5-BIT LFSR5\ 3-BIT LFSR6\ 32-BIT LFSR7\ SHIFT REGISTER-18\ SHIFT REGISTER-29\ 3-INPUT LUT的全部内容,更多相关HDLbits内容请搜索靠谱客的其他文章。

发表评论 取消回复